Los diagramas de temporización son la columna vertebral de la verificación de sistemas digitales. Traducen la lógica abstracta en líneas de tiempo visuales en las que los ingenieros, diseñadores y probadores confían para validar el comportamiento de las señales. Cuando un diagrama de temporización contiene errores, las consecuencias van mucho más allá del plano de dibujo. Las suposiciones incorrectas sobre el tiempo pueden provocar fallos de hardware, corrupción de datos o inestabilidad del sistema en entornos de producción. Esta guía explora los errores más frecuentes encontrados en el análisis de temporización y proporciona estrategias concretas para garantizar la precisión.

Crear un diagrama de temporización preciso requiere más que simplemente dibujar líneas. Exige una comprensión profunda de los dominios de reloj, la propagación de señales y las restricciones físicas. Los ingenieros a menudo se apresuran en la fase de visualización, pasando por alto detalles sutiles que se vuelven críticos durante la implementación. Al reconocer estos errores comunes desde el principio, los equipos pueden ahorrar tiempo significativo durante las fases de depuración e integración. Examinemos ahora las áreas específicas donde normalmente ocurren estos errores.

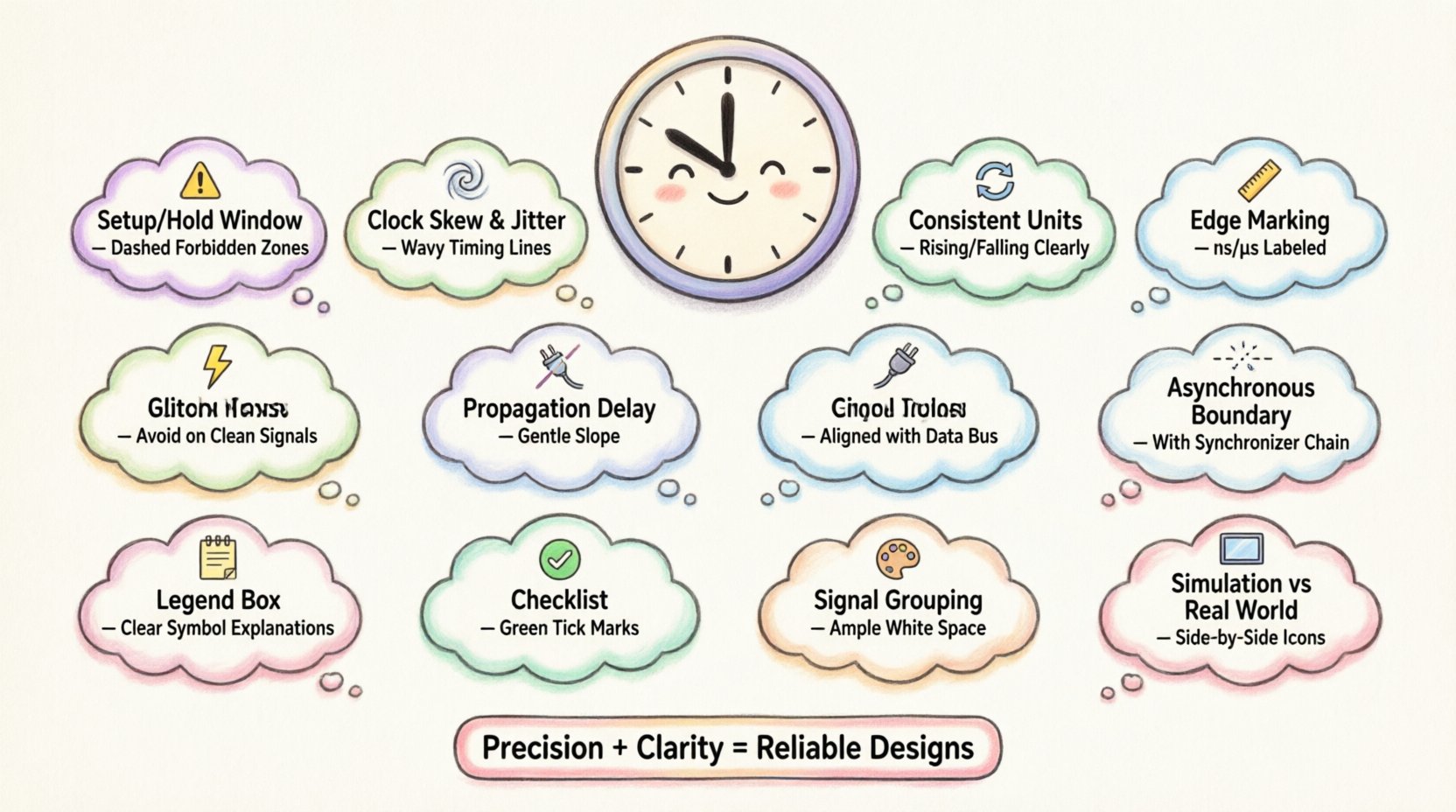

1. Interpretación incorrecta de las violaciones de tiempo de setup y hold ⚠️

Los tiempos de setup y hold son restricciones fundamentales en el diseño digital síncrono. Una violación de setup ocurre cuando los datos llegan demasiado tarde antes del borde activo del reloj. Una violación de hold ocurre cuando los datos cambian demasiado pronto después del borde del reloj. Estos no son solo conceptos teóricos; representan límites físicos de los flip-flops y puertas lógicas.

Muchos diagramas no indican claramente la ventana de validez para las señales de datos. Al dibujar estas señales, los ingenieros a veces omiten las ventanas crítica de setup y hold, lo que genera ambigüedad durante la revisión. Un diagrama sólido debe marcar explícitamente estas ventanas en relación con el borde del reloj.

- Error común:Dibujar las transiciones de datos alineadas exactamente con el borde del reloj sin considerar el jitter o el desfase.

- Error común:Ignorar la dirección del borde (ascendente frente a descendente) para las ventanas de setup/hold.

- Error común:Suponer bordes de reloj ideales con tiempo de transición cero.

Para evitar estos problemas, siempre debe anotarse el margen de setup y hold. Utilice sombreado o marcadores distintivos para mostrar las zonas prohibidas donde las transiciones de datos no son válidas. Esta pista visual obliga a los revisores a comprobar si la ruta de la señal cumple con los requisitos de temporización de la lógica receptora.

2. Descuidar el desfase del reloj y el jitter 🌪️

El desfase del reloj se refiere a la diferencia en los tiempos de llegada de la señal de reloj en diferentes componentes. El jitter representa las variaciones a corto plazo en el tiempo de la señal de reloj. Ambos factores pueden alterar drásticamente las ventanas de temporización efectivas para las señales de datos.

Un error común en los diagramas es tratar el reloj como una línea vertical perfectamente recta en todos los componentes. En la realidad, las redes de distribución introducen retrasos. Si un diagrama muestra una única línea de reloj que se ramifica hacia tres registros diferentes sin tener en cuenta las diferencias de ruta, presenta una visión poco realista del comportamiento del sistema.

- Impacto:El desfase puede reducir el tiempo disponible para que los datos se propaguen, provocando violaciones de setup falsas.

- Impacto:El jitter puede reducir el margen de tiempo de hold, aumentando el riesgo de metastabilidad.

Al crear diagramas, represente las rutas del reloj como líneas separadas con desplazamientos relativos si el desfase es significativo. Si el desfase es despreciable, indique claramente esa suposición en las notas del diagrama. No oculte la complejidad de la distribución del reloj si afecta al presupuesto de temporización.

3. Escalas y unidades de tiempo inconsistentes 📏

Uno de los errores más simples pero más dañinos es mezclar escalas de tiempo dentro de un mismo diagrama. Una sección podría mostrar nanosegundos mientras que otra muestra microsegundos. Esta inconsistencia obliga al lector a recalculas constantemente las proporciones, aumentando la posibilidad de malentendidos.

Otro problema es la ausencia de un eje de tiempo claro. Sin una barra de escala o marcas etiquetadas, la duración de los pulsos se vuelve subjetiva. Un pulso corto podría ser de 10 nanosegundos o de 100 nanosegundos, dependiendo de cómo el lector interprete el espaciado.

Siga estas normas para mantener la consistencia:

- Defina la escala:Coloque una regla de tiempo en la parte inferior o superior del diagrama.

- Utilice notación científica:Etiquete claramente las unidades (ns, μs, ps) en el encabezado.

- Mantenga las proporciones proporcionales: Asegúrese de que la distancia horizontal entre los eventos coincida con la diferencia de tiempo.

La consistencia genera confianza. Cuando cada ingeniero observa el diagrama, debería obtener los mismos valores de temporización sin necesidad de hacer suposiciones sobre la escala del dibujo.

4. Ambigüedad en los desencadenadores de borde 🔄

La lógica digital a menudo depende de desencadenadores específicos de borde, como el borde ascendente o el borde descendente. Un diagrama de temporización debe mostrar explícitamente qué borde desencadena la acción. La ambigüedad aquí puede provocar un comportamiento completamente opuesto en el hardware.

Un error común es dibujar una señal de reloj sin indicar el borde activo. Por ejemplo, si un flip-flop se activa en el borde descendente, pero el diagrama se ve idéntico al de un desencadenador en el borde ascendente, el diseñador de lógica podría implementar un comportamiento incorrecto.

- Mejor práctica:Utilice flechas en la línea del reloj para indicar el borde activo.

- Mejor práctica:Etiquete el tipo de desencadenador en la leyenda (por ejemplo, “Posedge”, “Nedge”).

- Mejor práctica:Evite usar flechas dobles a menos que ambos bordes sean activos.

La claridad es fundamental. Si una señal es asíncrona, asegúrese de que esté claramente separada del dominio del reloj para evitar confusiones sobre qué borde la controla.

5. Ignorar los retrasos de propagación ⏳

El retraso de propagación es el tiempo que tarda una señal en viajar desde la entrada hasta la salida a través de una puerta lógica o un cable. En diagramas ideales, las señales parecen cambiar instantáneamente. En sistemas físicos, siempre existe un retraso.

Cuando los diseñadores omiten los retrasos de propagación, el diagrama de temporización sugiere que la salida cambia inmediatamente después del cambio de entrada. Esto puede ocultar violaciones de temporización que ocurrirán en el silicio. Por ejemplo, una ruta combinacional podría parecer cumplir con el período del reloj en el diagrama, pero el retraso real hace que los datos pasen más allá del siguiente borde del reloj.

| Característica | Diagrama ideal | Implementación en el mundo real |

|---|---|---|

| Transición de señal | Línea vertical | Línea inclinada con retraso |

| Propagación | Instantáneo | Retraso de puerta + retraso de cable |

| Margen de configuración | A menudo no verificado | Debe considerar el peor caso |

Para mitigar esto, anote el retraso esperado en las rutas críticas. Si el retraso es significativo en comparación con el período del reloj, dibuje la transición con una pendiente o marque explícitamente el valor del retraso. Esta representación visual ayuda a los revisores a detectar cuellos de botella potenciales antes de la fabricación.

6. Ignorar los riesgos de metastabilidad 🌌

La metastabilidad ocurre cuando un flip-flop recibe datos cerca del borde del reloj, provocando que entre en un estado indefinido durante una duración impredecible. Los diagramas de temporización rara vez capturan este estado explícitamente porque es un modo de fallo, no una operación normal.

Sin embargo, ignorar la posibilidad de metastabilidad en interfaces asíncronas es un error crítico. Si un diagrama muestra una señal asíncrona sincronizándose con un reloj sin una cadena de sincronización, implica un riesgo de pérdida o corrupción de datos.

- Identificación: Busque señales que cruzan dominios de reloj sin una sincronización adecuada.

- Documentación: Observe dónde la metastabilidad es un riesgo conocido y cómo se mitiga.

- Visualización: Utilice líneas punteadas para indicar límites asíncronos.

Aunque el sistema esté diseñado para manejar la metastabilidad, el diagrama debe reflejar las etapas de sincronización. Esto garantiza que el equipo de verificación sepa que debe probar estas condiciones específicas.

7. Glitchs de señal y peligros ⚡

Los glitchs son pulsos transitorios que ocurren debido a retrasos de propagación desiguales en caminos paralelos. Pueden causar activación falsa de lógica si no se tienen en cuenta en el análisis de tiempo.

Un error común es dibujar señales limpias y estables donde los glitchs son físicamente inevitables. Por ejemplo, en un multiplexor que cambia entre entradas, la salida podría parpadea brevemente antes de estabilizarse. Si el diagrama muestra una transición suave, la lógica posterior podría no estar diseñada para filtrar estos glitchs.

Resalte las zonas de peligro potenciales en el diagrama. Utilice anotaciones para advertir que una señal específica podría presentar un comportamiento transitorio durante los cambios de estado. Esto informa la estrategia de prueba para incluir escenarios de detección de glitchs.

8. Falta de contexto para señales de control 🔌

Las señales de datos son inútiles sin el contexto de señales de control como habilitar, reinicio o selección de chip. Un diagrama que se centra únicamente en las líneas de datos a menudo omite las condiciones necesarias para que esos datos sean válidos.

Por ejemplo, un bus de datos podría mostrar valores válidos, pero si la señal «Habilitar Escritura» no se muestra como activa durante esa ventana, los datos quedan efectivamente ignorados. Por el contrario, si la señal «Habilitar Escritura» está activa pero los datos son inválidos, el sistema escribe datos basura.

- Incluir control: Muestre siempre las señales de control junto con las señales de datos.

- Definir validez: Utilice una bandera «Válida» o indicador similar para indicar cuándo los datos son confiables.

- Condiciones de estado: Etiquete claramente el estado de las señales de control (activo alto frente a activo bajo).

La completitud es clave. Un diagrama de tiempo que carece de contexto de señales de control suele ser una fuente de confusión durante la depuración. Asegúrese de que la relación entre control y datos sea visualmente explícita.

9. Mala utilización de anotaciones y leyendas 📝

Incluso un diagrama perfectamente preciso puede ser malinterpretado si carece de anotaciones adecuadas. Los símbolos, abreviaturas y leyendas deben ser coherentes y explicados.

Errores comunes de anotación incluyen:

- Usar etiquetas genéricas como «Señal A» en lugar de nombres descriptivos.

- No explicar el significado de estilos de línea específicos (sólido frente a punteado).

- Omitir la definición del nivel activo (activo alto frente a activo bajo).

Una sección de leyenda dedicada debe formar parte de cada diagrama de tiempo. Define cada símbolo, estilo de línea y abreviatura utilizada. Esto reduce la carga cognitiva para el lector y garantiza que todos interpreten el diagrama de la misma manera.

10. Lista de verificación y revisión ✅

Antes de finalizar un diagrama de tiempos, es necesario realizar una revisión sistemática. Utilice la siguiente lista de verificación para validar la precisión y claridad de su trabajo.

| Elemento de verificación | Criterio de aprobación |

|---|---|

| Escala de tiempo | Unidades consistentes y regla clara proporcionadas |

| Borde de reloj | Borde activo claramente marcado para todos los relojes |

| Tiempo de establecimiento/tiempo de retención | Ventanas definidas para señales síncronas |

| Propagación | Retardos considerados en las rutas críticas |

| Señales de control | Señales de habilitación/reinicio mostradas junto con los datos |

| Leyendas | Todos los símbolos y abreviaturas explicados |

| Cruce de dominios | Puntos de CDC identificados y marcados |

Actualizar regularmente esta lista de verificación garantiza que ningún error común pase desapercibido. Sirve como una puerta de calidad para la documentación antes de que llegue al equipo de ingeniería.

11. Claridad visual y diseño de disposición 🎨

La disposición de un diagrama de tiempos afecta la facilidad con la que se detectan los errores. Los diagramas congestionados con señales superpuestas son propensos a ser malinterpretados. La alineación vertical de señales relacionadas ayuda al ojo a rastrear la relación entre los eventos.

Siga estos principios de disposición:

- Agrupar señales:Mantenga las señales relacionadas (como dirección y datos) cerca unas de otras.

- Alinear bordes:Asegúrese de que los bordes de reloj estén alineados verticalmente en todos los canales.

- Espaciado:Deje suficiente espacio en blanco para evitar la superposición de señales.

- Codificación por colores:Utilice colores diferentes para diferentes dominios de reloj si está disponible (aunque el negro y blanco es el estándar para impresión).

Una disposición limpia reduce el esfuerzo cognitivo necesario para interpretar el diagrama. Esto facilita detectar anomalías y violaciones de tiempo a simple vista.

12. Limitaciones del mundo real frente a la simulación 🖥️

Los diagramas de temporización derivados únicamente de la simulación podrían no reflejar las realidades físicas. Las herramientas de simulación suelen asumir condiciones ideales, como capacitancia parásita cero y ruteo perfecto.

Al traducir los resultados de la simulación a documentación, los ingenieros deben tener en cuenta las variaciones de fabricación. Las esquinas de proceso, voltaje y temperatura (PVT) pueden desplazar los márgenes de temporización. Un diagrama que solo muestre valores nominales podría ser insuficiente para un diseño robusto.

- Peor caso:Considere la esquina de proceso más lenta para el análisis de temporización.

- Mejor caso:Considere la esquina de proceso más rápida para el análisis del tiempo de retención.

- Margen:Agregue márgenes de seguridad al diagrama para tener en cuenta las variaciones de PVT.

La documentación debe reflejar la robustez del diseño, no solo los resultados de simulación en el mejor caso. Esto prepara al equipo para escenarios de despliegue en el mundo real.

Reflexiones finales sobre la precisión de temporización 🛡️

Los diagramas de temporización son herramientas de comunicación tanto como especificaciones técnicas. Su objetivo principal es transmitir claramente la intención y las restricciones a todos los interesados. Al evitar errores comunes como ignorar el desfase, omitir los disparos por flanco o omitir las señales de control, los ingenieros aseguran que la intención del diseño se preserve desde la documentación hasta el hardware.

La precisión en estos diagramas evita re-spins costosos y ciclos de depuración. Un diagrama bien estructurado sirve como fuente única de verdad durante todo el ciclo de vida del proyecto. Invierta el tiempo necesario para realizar correctamente el análisis de temporización, y la implementación posterior fluirá sin problemas.

Recuerde que un diagrama de temporización es un documento vivo. Debe actualizarse cada vez que cambie el diseño. Mantener la integridad de la información de temporización asegura que el sistema permanezca confiable durante toda su vida operativa. Enfóquese en la precisión, claridad y completitud para entregar diseños digitales robustos.