Los diagramas de tiempo son la columna vertebral del diseño de sistemas digitales. Sirven como el contrato visual entre la lógica, el hardware y el software, definiendo exactamente cuándo deben cambiar de estado las señales. Sin embargo, a pesar de su amplia utilización en ingeniería, persiste una niebla de malentendidos sobre cómo se crean, interpretan y utilizan estos diagramas. Muchos profesionales los tratan como ilustraciones estáticas en lugar de representaciones dinámicas del comportamiento del sistema.

Esta guía tiene como objetivo aclarar las ideas. Desmontaremos los malentendidos comunes, exploraremos las realidades técnicas de la propagación de señales y estableceremos un marco para crear documentación de tiempos precisa. Al separar el hecho de la ficción, los ingenieros podrán reducir el tiempo de depuración y mejorar la confiabilidad del sistema.

¿Qué es un diagrama de tiempo? 🤔

Un diagrama de tiempo es una representación gráfica del comportamiento de las señales en un circuito digital a lo largo del tiempo. A diferencia de un esquema, que muestra la conectividad, un diagrama de tiempo muestra causalidad y relaciones temporales. Representa los niveles de señal (alto, bajo o flotante) contra una línea de tiempo, permitiendo a los diseñadores verificar que los datos estén estables cuando se espera.

Las características clave incluyen:

- Eje del tiempo:Normalmente se extiende horizontalmente, representando la progresión de los eventos.

- Líneas de señal:Líneas verticales que representan cables específicos, buses o estados lógicos.

- Bordes:Transiciones desde bajo a alto (ascendente) o desde alto a bajo (descendente).

- Etiquetas:Anotaciones que indican tiempos de preparación, tiempos de retención o retardos.

Sin una comprensión clara de estos componentes, el diagrama se convierte en una fuente de confusión en lugar de claridad.

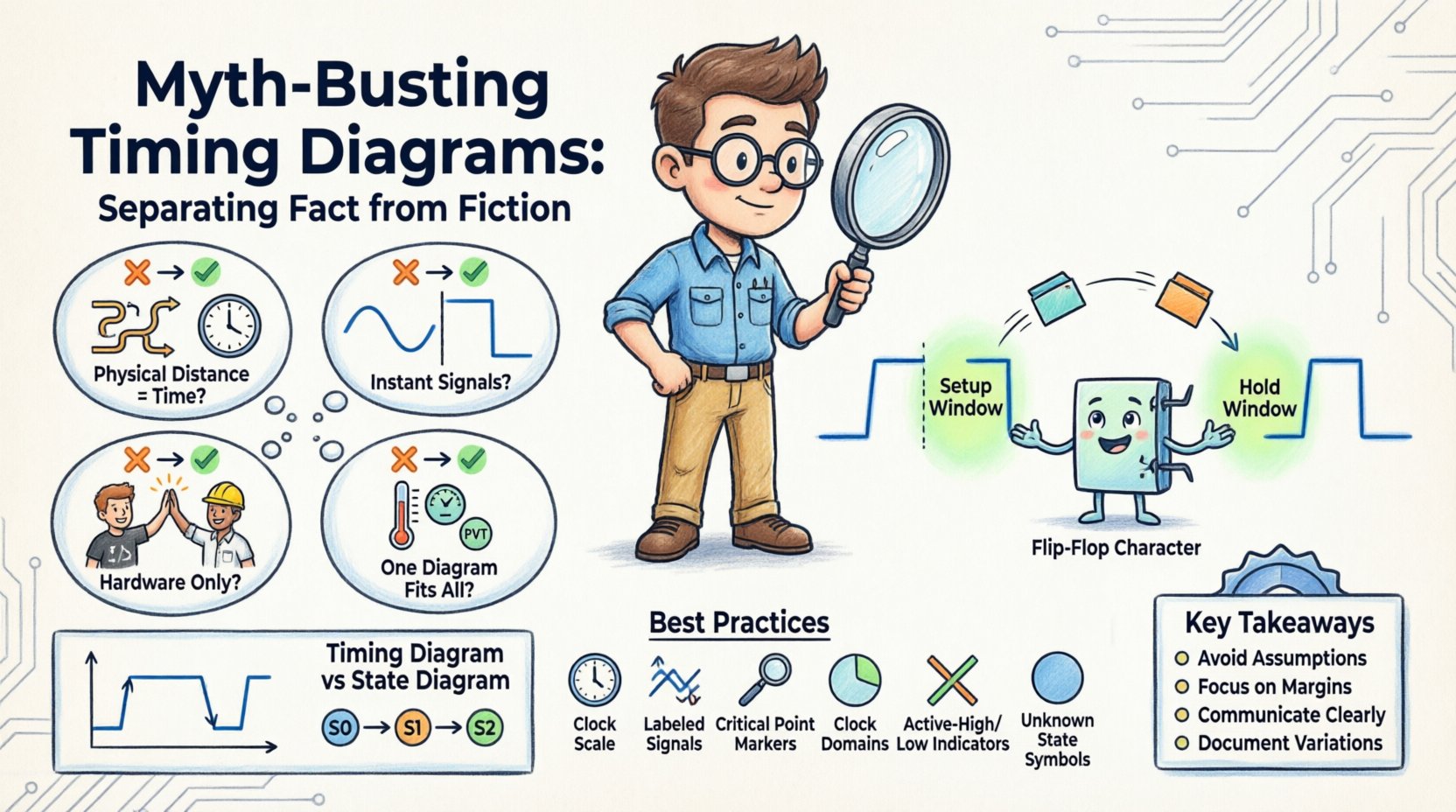

Mitos comunes sobre los diagramas de tiempo 🚫

Para mejorar la calidad del diseño, primero debemos identificar las creencias falsas que conducen a errores. A continuación se presentan los mitos más prevalentes que circulan en círculos técnicos.

Mito 1: Los diagramas de tiempo muestran la distancia física exacta 📏

La ficción:Los ingenieros a menudo asumen que la distancia horizontal entre dos bordes en un diagrama se correlaciona directamente con la longitud física de la traza en una placa de circuito impreso.

El hecho:Los diagramas de tiempo representan el tiempo lógico o eléctrico, no el espacio físico. Aunque la longitud de la traza afecta el retardo de propagación, el diagrama se centra en el resultadode ese retardo, no en la geometría misma. Un retardo de 1 nanosegundo podría representar una traza de 15 cm en una placa de FR4 o una traza de 10 cm en una traza de cobre con constantes dieléctricas diferentes. El diagrama abstrae el medio físico para centrarse en la ventana de tiempo.

- La longitud física determina el retardo, pero el diagrama muestra el valor del retardo.

- La complejidad de la ruta se oculta; solo importa el resultado final.

- Suponer una escala 1:1 entre tiempo y distancia conduce a errores en el diseño de la disposición.

Mito 2: Las transiciones de señal son instantáneas ⚡

La ficción:En muchos diagramas, las líneas verticales indican que una señal cambia de estado inmediatamente.

El hecho:Ninguna señal física cambia de estado instantáneamente. Siempre existe un tiempo de subida y un tiempo de bajada. Cuando un diagrama muestra una arista vertical, representa una transición que es rápida en comparación con el período del reloj, pero no cero. Ignorar los tiempos de transición puede provocar problemas de integridad de la señal, como sobrepasamientos o crosstalk, que no son visibles en diagramas idealizados.

- El tiempo de subida es la duración para pasar del 10% al 90% del voltaje.

- Los diagramas a menudo simplifican esto para mejorar la legibilidad, pero la simulación debe tenerlo en cuenta.

- Los diseños de alta velocidad requieren un modelado explícito de las pendientes de transición.

Mitología 3: Los diagramas de temporización solo son para ingenieros de hardware 🛠️

La ficción:Los desarrolladores de software y los arquitectos de sistemas a menudo ignoran los diagramas de temporización, asumiendo que no son relevantes para la lógica del código.

El hecho:El software debe cumplir con las restricciones de temporización del hardware. Las interrupciones, las transferencias DMA y la E/S mapeada en memoria dependen todas del temporizado establecido por el hardware. Si un controlador intenta leer datos antes de que el hardware active la señal «Listo», se produce un error de bus. Los diagramas de temporización son esenciales para la comunicación entre disciplinas.

- Las interrupciones de software deben alinearse con los ciclos de reloj del hardware.

- Las ventanas de acceso a memoria están definidas por las especificaciones de temporización.

- Tanto los equipos de hardware como los de software necesitan una comprensión compartida de la cronología.

Mitología 4: Un diagrama sirve para todos los contextos 🌍

La ficción:Un único diagrama de temporización puede describir todo un sistema, independientemente de las condiciones de operación.

El hecho:El temporizado varía con la temperatura, el voltaje y las variaciones de proceso (PVT). Un diagrama trazado para condiciones nominales puede fallar en los extremos. Los diseñadores deben tener en cuenta los escenarios de peor caso. Un diagrama que muestra un comportamiento de mejor caso suele ser menos útil que uno que destaque los límites de operación.

- El retardo de peor caso determina el período mínimo del reloj.

- La temperatura afecta la resistencia y la capacitancia.

- Las variaciones de proceso cambian las velocidades de conmutación de los transistores.

Análisis profundo: Tiempos de setup y hold ⏱️

Comprender las violaciones de temporización es fundamental. Dos conceptos específicos dominan el análisis de la integridad de los datos: el tiempo de setup y el tiempo de hold. Estos suelen ser la causa de los errores más difíciles de detectar en los sistemas digitales.

Tiempo de setup (Tsu)

El tiempo de setup es la cantidad mínima de tiempoantesque debe estar estable antes de una arista del reloj. Si los datos cambian demasiado cerca de la arista del reloj, el flip-flop receptor puede no capturar el valor correcto.

- Garantiza que los datos estén estables antes de que se cierre la ventana de captura.

- Las violaciones causan metastabilidad o estados lógicos incorrectos.

- El retardo de la ruta debe ser menor que el período del reloj menos el tiempo de configuración.

Tiempo de retención (Th)

El tiempo de retención es la cantidad mínima de tiempodespuésdespués de una transición del reloj en la que los datos deben permanecer estables. Si los datos cambian demasiado pronto después de la transición del reloj, el flip-flop podría perder el valor previamente capturado.

- Garantiza que los datos permanezcan estables durante suficiente tiempo para ser capturados.

- Las violaciones suelen ser más difíciles de corregir que las violaciones de configuración.

- El retardo de la ruta debe ser mayor que el requisito de tiempo de retención.

Escenarios de violación de temporización

Al analizar un diagrama de temporización, busque los siguientes patrones:

- Violación de configuración:La señal de datos aún está cambiando cuando llega la transición del reloj.

- Violación de retención:La señal de datos cambia inmediatamente después de la transición del reloj.

- Glitch:Un pulso corto que cae dentro de la ventana de configuración/retención pero no es una transición válida.

Diagrama de temporización frente a diagrama de estados 🔄

A menudo surge confusión entre los diagramas de temporización y los diagramas de estados. Aunque ambos describen el comportamiento del sistema, responden a preguntas diferentes. Un diagrama de estados muestraquélo que hace el sistema (flujo lógico), mientras que un diagrama de temporización muestracuándoocurre (flujo temporal).

| Característica | Diagrama de temporización | Diagrama de estados |

|---|---|---|

| Enfoque principal | Tiempo y niveles de señal | Lógica y flujo de control |

| Representación de ejes | Horizontal = Tiempo | Horizontal = Estados lógicos |

| Mejor para | Integridad de señal, sincronización | Diseño de algoritmos, lógica de FSM |

| Complejidad | Alta resolución temporal | Alto grado de ramificación lógica |

| Detalles de la señal | Muestra niveles de voltaje (Alto/Bajo) | Muestra estados abstractos (Ocioso/Ejecución) |

Usar el diagrama correcto para la tarea evita malentendidos. Una máquina de estados puede diseñarse sin un diagrama de temporización, pero una interfaz de bus de alta velocidad no puede.

Mejores prácticas para crear diagramas precisos ✅

Para asegurar que su documentación sea efectiva, siga estas directrices. La precisión en la documentación reduce la ambigüedad en la implementación.

- Defina la escala de tiempo: Siempre especifique las unidades (ns, µs, ciclos). Si utiliza ciclos, defina la frecuencia del reloj.

- Etiquete cada señal: No use nombres genéricos como «Señal 1». Use nombres descriptivos como «CLK_IN» o «DATA_VALID».

- Marque los puntos críticos: Resalte explícitamente las ventanas de setup y hold con sombreado o anotaciones.

- Incluya dominios de reloj: Si existen múltiples relojes, distíngalos claramente. Muestre la relación entre relojes asíncronos si es aplicable.

- Muestre activo alto/bajo: Aclare si un estado activo es alto (1) o bajo (0) para evitar errores de polaridad.

- Indique estados desconocidos: Use X o Z para representar estados indefinidos o de alta impedancia en lugar de dejarlos en blanco.

Manejo de señales asíncronas 🔄

Uno de los aspectos más desafiantes de los diagramas de temporización es el manejo de señales asíncronas. Estas son señales que no están sincronizadas con el reloj principal del sistema. Introducen incertidumbre que debe ser gestionada.

- Metastabilidad: Cuando una señal asíncrona llega cerca de un borde de reloj, el flip-flop puede entrar en un estado metastable. Finalmente se resolverá en 0 o 1, pero el tiempo que tarda es impredecible.

- Sincronizadores: Utilice cadenas de flip-flops para resolver la metastabilidad. Los diagramas de tiempo deben mostrar que la región metastable se resuelve antes del siguiente borde de reloj.

- Handshaking (negociación de señales): Protocolos como I2C o SPI utilizan handshaking asíncrono. El diagrama de tiempo debe mostrar los estados de espera en los que el maestro espera al esclavo.

Aplicación en el mundo real: Depuración de una condición de carrera 🐞

Imagine una situación en la que una bus de datos no se está leyendo correctamente. El sistema se bloquea ocasionalmente. Un análisis del diagrama de tiempo revela el problema.

- Observación: La señal «Listo» se activa ligeramente después del estrobo «Lectura».

- Verificación del diagrama: El diagrama de tiempo muestra que el borde de «Listo» cae dentro de la ventana de configuración del estrobo «Lectura».

- Conclusión: Los datos se están leyendo antes de que sean válidos.

- Solución: Ajuste la lógica para retrasar el estrobo «Lectura» o prolongar el pulso de «Listo».

Este ejemplo destaca por qué visualizar la cronología es crucial. Sin el diagrama, la condición de carrera permanece oculta en la lógica del código.

Herramientas y métodos de análisis 🔍

Aunque los nombres específicos de software no son el enfoque, los métodos de análisis permanecen constantes. La ingeniería moderna depende de la simulación y los visualizadores de ondas para validar los diagramas de tiempo.

- Simulación: Ejecute testbenches para generar ondas que coincidan con la intención del diseño.

- Análisis de Tiempo Estático (STA): Calcule los retrasos sin simulación para verificar violaciones en todos los caminos.

- Depuración de hardware: Utilice osciloscopios para capturar ondas del mundo real y compararlas con el diagrama teórico.

- Control de versiones: Mantenga los diagramas de tiempo bajo control de versiones. Los cambios en el hardware a menudo requieren actualizaciones en las especificaciones de tiempo.

El impacto del jitter y el skew 📉

Los diagramas de tiempo a menudo se dibujan con líneas perfectas y rectas. La realidad es más desordenada. El jitter y el skew son fuentes de ruido que afectan la precisión del tiempo.

- Jitter: Variaciones en el momento de los bordes de una señal. El jitter del reloj hace que la ventana de muestreo se desplace.

- S skew: La diferencia en el tiempo de llegada de la misma señal de reloj en diferentes puntos del circuito.

- Impacto: Ambos reducen el margen de tiempo. Un diagrama de tiempo debería mostrar idealmente el margen, no solo el borde ideal.

Resumen de los puntos clave 📝

Los diagramas de tiempo son más que simples dibujos; son especificaciones de comportamiento. Al comprender los mitos y hechos que los rodean, los ingenieros pueden diseñar sistemas más robustos.

- Evite suposiciones: No asuma transiciones instantáneas ni sincronización perfecta.

- Enfóquese en los márgenes: Los tiempos de preparación y retención son los amortiguadores de seguridad que evitan el fallo.

- Comuníquese claramente: Utilice diagramas para cerrar la brecha entre los equipos de hardware y software.

- Documente las variaciones: Reconozca que el tiempo cambia con el entorno y el proceso.

Cuando mire un diagrama de tiempo, vea el tiempo. Vea las restricciones. Vea la confiabilidad. Esta perspectiva transforma una imagen estática en una herramienta poderosa para la excelencia en ingeniería.