En el mundo complejo de la electrónica digital y el diseño de sistemas, la comunicación entre componentes depende en gran medida de relaciones temporales precisas. Un diagrama de tiempo sirve como el lenguaje visual que describe estas relaciones. Es una representación gráfica que muestra cómo cambian las señales con el tiempo. Sin esta herramienta, depurar interacciones de hardware o verificar el comportamiento lógico sería casi imposible. Esta guía explora los elementos esenciales, parámetros y estrategias de lectura necesarios para interpretar estos diagramas de forma efectiva.

¿Qué es exactamente un diagrama de tiempo? 📐

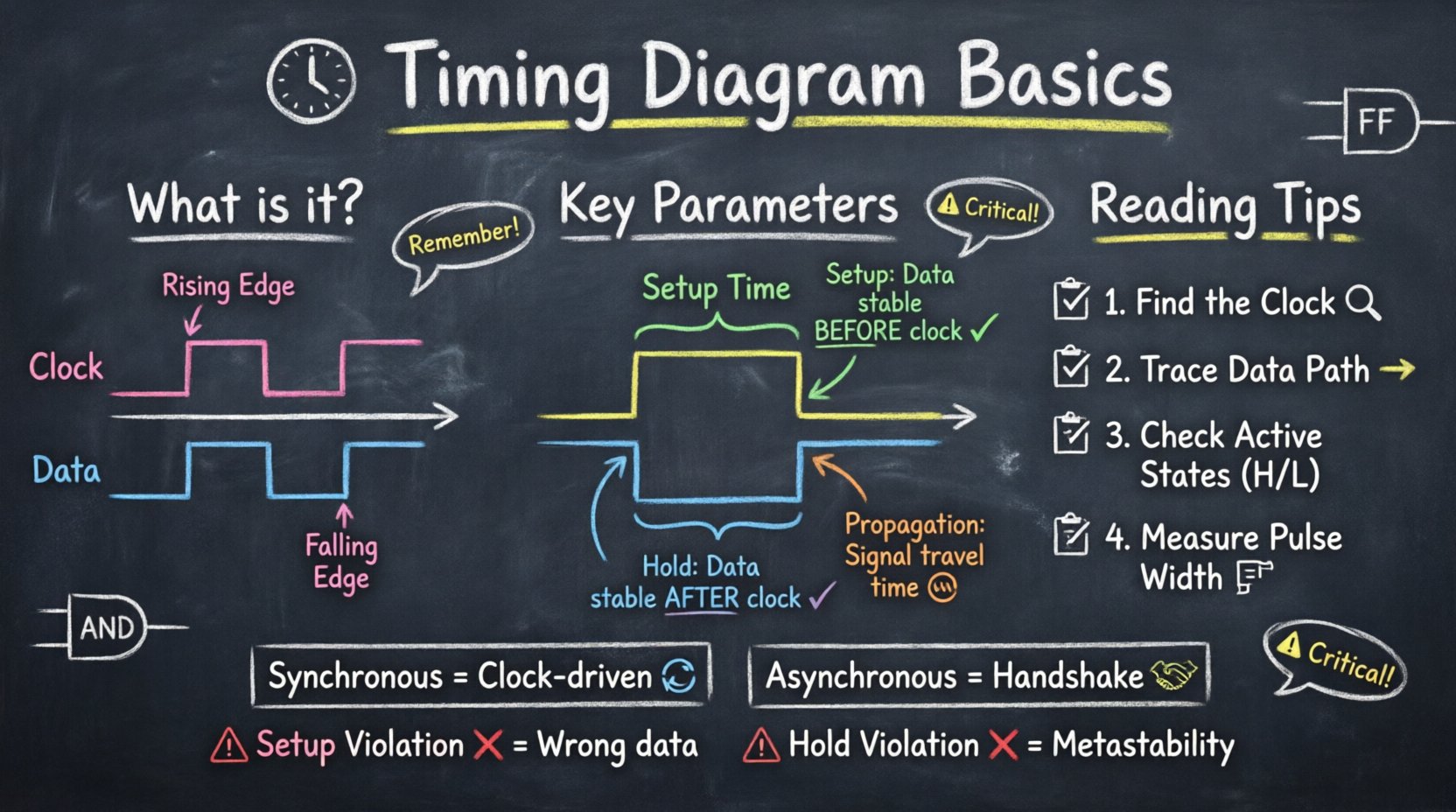

Un diagrama de tiempo es un tipo específico de gráfico utilizado para ilustrar la relación entre dos o más señales durante un período definido. A diferencia de una tabla de estados lógicos, que lista los estados en una cuadrícula, un diagrama de tiempo representa estos estados sobre un eje horizontal de tiempo. Este enfoque visual permite a los ingenieros ver la secuencia de eventos, la duración de los pulsos y la sincronización entre diferentes partes de un circuito.

Estos diagramas son críticos en varios contextos:

- Diseño de hardware:Verificar que los datos estén estables antes de que llegue el borde del reloj.

- Análisis de protocolos:Comprender estándares de comunicación como I²C, SPI o UART.

- Verificación del sistema:Asegurar que las máquinas de estado cambien correctamente sin condiciones de carrera.

- Depuración:Identificar violaciones de setup o hold que causan fallas en el sistema.

Al visualizar el tiempo, los diseñadores pueden predecir cómo se comporta un sistema bajo carga, asegurando fiabilidad y rendimiento.

Elementos principales de un diagrama de tiempo 🎯

Para leer un diagrama de tiempo, primero se debe entender sus bloques fundamentales. Cada diagrama consta de señales, tiempo y transiciones. La disposición de estos elementos cuenta una historia sobre el comportamiento eléctrico del sistema.

Señales y líneas

Cada línea horizontal representa una señal específica. Esto podría ser una señal de reloj, una línea de datos, un bus de direcciones o una bandera de control. Las señales suelen etiquetarse al inicio de la línea o en una leyenda. La posición vertical de la línea no indica niveles de voltaje; más bien, la posición vertical respecto a la línea de referencia indica estados lógicos.

El eje del tiempo

El eje horizontal representa el tiempo. Fluye de izquierda a derecha. En muchos diagramas, los intervalos de tiempo se marcan con líneas verticales punteadas. Estos marcadores a menudo corresponden a ciclos de reloj. Es importante tener en cuenta que la escala de tiempo no siempre es lineal. A veces, momentos específicos se amplían para mostrar detalles de microsegundos o nanosegundos, mientras que otras partes muestran un comportamiento de nivel macro.

Niveles lógicos

Las señales suelen alternar entre dos estados: Alto y Bajo. Estos corresponden a los valores binarios 1 y 0. En algunos contextos, Bajo puede representar un estado activo (activo bajo), mientras que Alto representa el estado activo (activo alto). Comprender el estado activo es crucial para interpretar señales de control como Reset o Selección de Chip.

Transiciones y bordes

Las líneas verticales que conectan los niveles lógicos representan transiciones. Hay dos tipos principales de bordes:

- Borde ascendente:Una transición de Bajo a Alto.

- Borde descendente:Una transición de Alto a Bajo.

Estos bordes a menudo desencadenan acciones en circuitos digitales. Por ejemplo, un registro podría actualizar sus datos precisamente cuando la señal de reloj asciende.

Parámetros de tiempo críticos ⚙️

Comprender las líneas estáticas es solo la mitad de la batalla. Los parámetros dinámicos definen las restricciones dentro de las cuales debe operar el sistema. Violar estos parámetros conduce a la corrupción de datos o fallas del sistema.

Tiempo de preparación

El tiempo de preparación es la cantidad mínima de tiempo antes de una transición de reloj en la que una señal de datos debe estar estable y válida. Si los datos cambian demasiado cerca de la transición del reloj, el circuito receptor puede no tener suficiente tiempo para registrar correctamente el valor. Este parámetro se aplica estrictamente en sistemas síncronos.

Tiempo de retención

El tiempo de retención es la cantidad mínima de tiempo después de una transición de reloj en la que la señal de datos debe permanecer estable. Aunque el reloj ya haya activado la captura, los datos no pueden cambiar inmediatamente. Si cambian demasiado rápido, el latch o flip-flop interno podría entrar en un estado inestable.

Retardo de propagación

El retardo de propagación es el tiempo que tarda una señal en viajar desde la entrada de un componente hasta su salida. Esto es inherente a las propiedades físicas del circuito. Cuando múltiples componentes están en cascada, estos retardos se acumulan, afectando la frecuencia máxima de operación del sistema.

Ciclo y frecuencia del reloj

El ciclo del reloj es la duración de un período completo de la señal de reloj. La frecuencia es el inverso de este período, medido en hercios (Hz). El presupuesto de tiempo de un sistema suele definirse por el período del reloj. Si la suma de todos los retardos de propagación excede el período del reloj, el sistema no funcionará correctamente.

| Parámetro | Definición | Impacto de la violación |

|---|---|---|

| Tiempo de preparación | Tiempo durante el cual los datos deben estar estables antes de la transición del reloj | Datos perdidos o captura incorrecta |

| Tiempo de retención | Tiempo durante el cual los datos deben estar estables después de la transición del reloj | Metastabilidad o corrupción de datos |

| Retardo de propagación | Tiempo que tarda la señal en viajar a través de la lógica | Frecuencia máxima reducida o fallo de temporización |

| Desfase | Diferencia en el tiempo de llegada de la señal de reloj | Margen de temporización reducido |

| Jitter | Variaciones a corto plazo en la temporización de la señal | Operación inestable a altas velocidades |

Lectura y análisis de señales 📖

Interpretar un diagrama de temporización requiere un enfoque sistemático. Apresurarse al examinar la información visual puede llevar a una interpretación errónea del comportamiento del sistema. Siga estos pasos para analizar un diagrama con precisión.

- Identifique el reloj: Localice la señal periódica que impulsa el sistema. Esta suele ser la referencia para todas las demás acciones.

- Rastree la ruta de datos:Siga las líneas de señal desde la fuente hasta el destino. Observe dónde se genera los datos y dónde se consumen.

- Verifique los estados activos:Determine si las señales están activas en alto o en bajo. Una señal baja podría significar «Habilitar», mientras que una señal alta podría significar «Deshabilitar».

- Mida las duraciones:Observe la anchura de los pulsos. ¿Es el pulso lo suficientemente ancho para ser detectado? ¿Es demasiado estrecho para ser un parpadeo?

- Verifique las secuencias:Asegúrese de que las señales de control cambien en el orden correcto. Por ejemplo, una señal de reinicio debe activarse antes de que el sistema comience a procesar.

Al analizar diagramas complejos, ayuda dividir la línea de tiempo en ciclos discretos. Analice un período de reloj a la vez para comprender las transiciones de estado.

Sistemas síncronos frente a asíncronos 🔄

Los diagramas de temporización difieren significativamente según si el sistema es síncrono o asíncrono. Comprender esta distinción es vital para una interpretación correcta.

Sistemas síncronos

En un sistema síncrono, todas las operaciones están coordinadas por un reloj global. Cada cambio de estado ocurre en relación con una transición del reloj. Esto hace que el análisis de temporización sea más predecible. Puede calcular la velocidad máxima del sistema sumando los retrasos de la ruta más larga entre dos registros. Los diagramas de temporización aquí son altamente regulares, con eventos alineados verticalmente con las transiciones del reloj.

Sistemas asíncronos

Los sistemas asíncronos no dependen de un reloj global. En su lugar, utilizan protocolos de intercambio de señales en los que las señales cambian de estado según la preparación de la etapa anterior. Los diagramas de temporización para estos sistemas parecen menos regulares. Los eventos se activan por transiciones específicas de señal en lugar de un tic periódico. Analizarlos requiere una atención cuidadosa a la dependencia entre señales.

Problemas y violaciones de temporización comunes ⚠️

Incluso con un diseño cuidadoso, pueden surgir problemas de temporización. Estos problemas a menudo se manifiestan como fallas intermitentes que son difíciles de reproducir. Reconocerlos en un diagrama de temporización es una habilidad clave para el diagnóstico de fallos.

Violaciones de configuración

Una violación de configuración ocurre cuando los datos llegan demasiado tarde para la transición del reloj. Visualmente, esto se ve como una transición de datos que ocurre después de que la transición del reloj ya ha pasado. El resultado suele ser que el componente receptor captura el valor incorrecto o el valor anterior.

Violaciones de retención

Una violación de retención ocurre cuando los datos cambian demasiado pronto después de la transición del reloj. Esto significa que los nuevos datos sobrescriben los datos antiguos antes de que el componente haya terminado de capturarlos. Esto es particularmente peligroso porque puede provocar metastabilidad, en la que el voltaje de salida flota entre niveles alto y bajo.

Desviación y jitter

La desviación del reloj ocurre cuando la señal de reloj llega a diferentes componentes en tiempos distintos. Si la desviación es demasiado grande, la ventana de temporización efectiva para configuración y retención se reduce. El jitter se refiere a la inestabilidad del tiempo de transición del reloj. Un alto jitter dificulta garantizar márgenes de temporización, lo que requiere velocidades de reloj más bajas.

Mejores prácticas para la integridad de la señal 🛡️

Para garantizar un rendimiento robusto, los ingenieros deben seguir las mejores prácticas al diseñar y analizar el temporizado. Estas directrices ayudan a minimizar riesgos e incrementar la estabilidad del sistema.

- Minimice las longitudes de trazado:Los trazados más largos aumentan el retraso de propagación y la susceptibilidad al ruido. Mantenga las rutas de señal lo más cortas posible.

- Alinee las impedancias:Asegúrese de que la impedancia de la línea de transmisión coincida con la del transmisor y el receptor para prevenir reflexiones.

- Utilice planos de tierra:Un plano de tierra sólido proporciona una ruta de retorno de baja impedancia, reduciendo el ruido y la interferencia cruzada.

- Tenga en cuenta la temperatura:Los componentes electrónicos se comportan de manera diferente a diversas temperaturas. Los márgenes de diseño deben tener en cuenta las condiciones térmicas más desfavorables.

- Simule desde temprano:Utilice herramientas de simulación para modelar el comportamiento de temporización antes de construir prototipos físicos. Esto detecta las violaciones desde etapas tempranas del ciclo de diseño.

Aplicación en la depuración de hardware 🔍

Los diagramas de temporización no son solo para el diseño; son herramientas esenciales para la depuración. Cuando un sistema falla, los ingenieros utilizan osciloscopios o analizadores lógicos para capturar las formas de onda reales de las señales. Estas trazas capturadas luego se comparan con el diagrama de temporización esperado.

Si la forma de onda real se desvía del diagrama, la discrepancia apunta hacia la causa raíz. Por ejemplo, si una línea de datos presenta ruido durante la ventana de captura, indica un problema de alimentación o interferencia electromagnética. Si el borde del reloj está inclinado en lugar de ser agudo, sugiere un problema de fuerza del conductor.

Al correlacionar los datos visuales del osciloscopio con los requisitos lógicos del diagrama de temporización, los ingenieros pueden localizar con precisión los fallos. Este proceso transforma las restricciones de temporización abstractas en evidencia física tangible.

Resumen de los conceptos clave 💡

Dominar los fundamentos de los diagramas de temporización es fundamental para trabajar con sistemas digitales. Implica comprender la relación entre señales, tiempo y estados lógicos. Al prestar atención cuidadosa a parámetros como el tiempo de preparación, el tiempo de retención y el retardo de propagación, los diseñadores pueden crear sistemas que funcionen de forma confiable a altas velocidades.

La capacidad de leer e interpretar estos diagramas permite una comunicación efectiva entre los equipos de hardware y software. Cierra la brecha entre la lógica teórica y la realidad física. Ya sea que esté diseñando un circuito de control simple o un microprocesador complejo, el análisis de temporización sigue siendo una piedra angular del éxito de la ingeniería.

Recuerde siempre verificar sus estados activos, respetar los límites del reloj y tener en cuenta las limitaciones físicas. Con práctica, interpretar estas representaciones visuales se vuelve algo natural, lo que le permite diagnosticar problemas y optimizar el rendimiento con confianza.