En el mundo de la electrónica digital y la ingeniería de hardware, la comunicación entre componentes depende de una coordinación precisa. Sin una comprensión clara de cuándo cambian de estado las señales, los sistemas fallan. El diagrama de tiempo sirve como plano maestro para esta coordinación. Visualiza la relación entre señales a lo largo del tiempo, revelando si los datos son válidos, estables y listos para procesarse. Esta guía aborda las preguntas fundamentales que enfrentan ingenieros y estudiantes al analizar estas herramientas visuales críticas.

Ya sea que esté diseñando una interfaz de microcontrolador, depurando un protocolo de comunicación o estudiando lógica digital, comprender los aspectos temporales de su diseño es imprescindible. Este artículo explora la anatomía de los diagramas de tiempo, explica parámetros clave y responde preguntas comunes sobre la integridad de la señal y la sincronización.

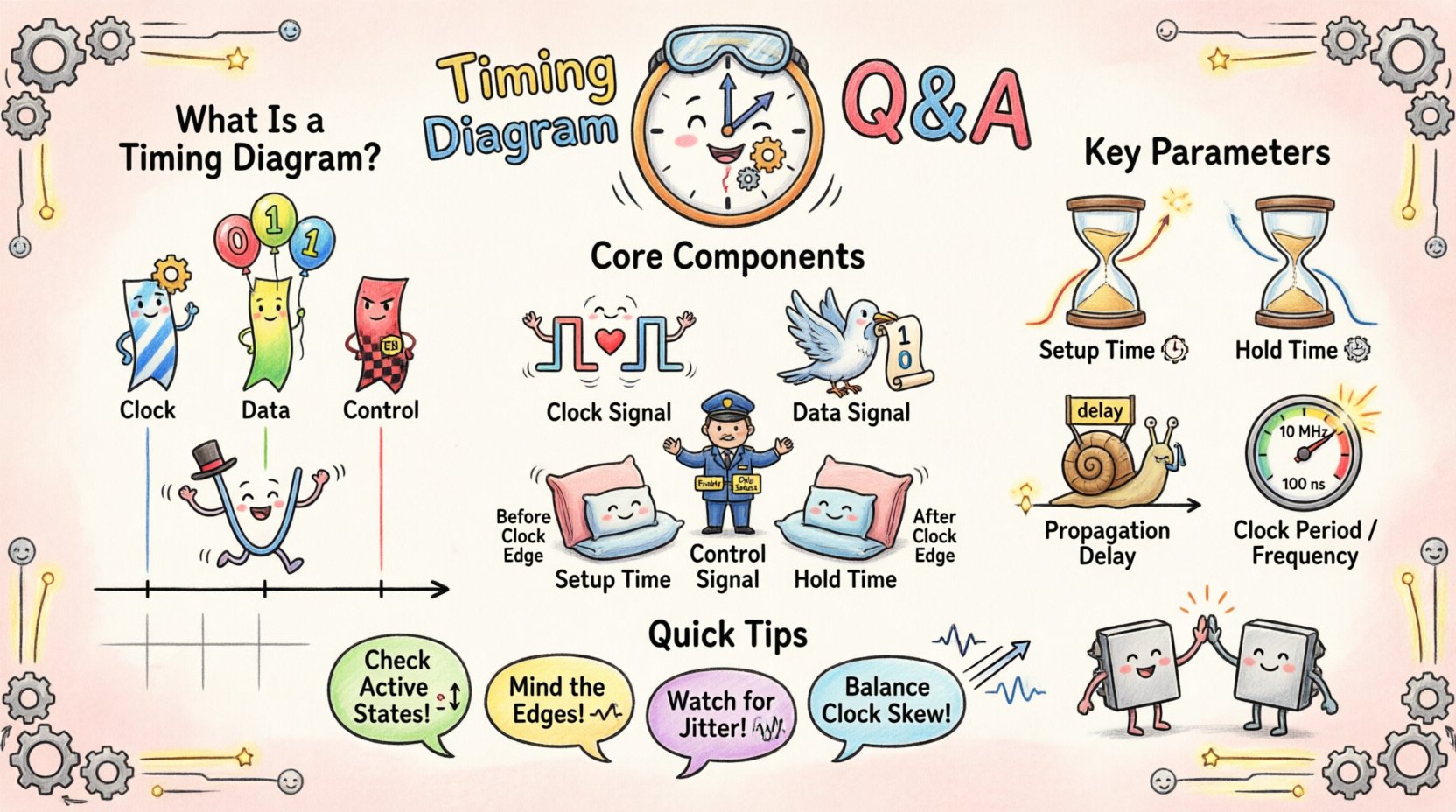

¿Qué es exactamente un diagrama de tiempo? 📊

Un diagrama de tiempo es una representación gráfica de la secuencia de eventos en un sistema. Representa los niveles de señal contra un eje horizontal de tiempo. A diferencia de un diagrama lógico, que muestra la conectividad, un diagrama de tiempo muestra el comportamiento. Permite ver si una señal cambia a alto o bajo antes o después de otra señal. Este contexto visual es esencial para verificar que el receptor tenga suficiente tiempo para leer los datos antes de que llegue el siguiente borde de reloj.

Las características clave incluyen:

- Eje de tiempo:Generalmente corre horizontalmente de izquierda a derecha.

- Líneas de señal:Líneas horizontales que representan cables individuales o buses de datos.

- Niveles lógicos:Los estados alto (1) y bajo (0) se representan como plataformas de voltaje distintas.

- Bordes:Líneas verticales que indican la transición de un estado a otro.

Componentes principales de un diagrama de tiempo 🧩

Para leer estos diagramas de forma efectiva, debe identificar los elementos estándar que componen la onda. Cada elemento desempeña un papel específico en la sincronización del sistema.

| Componente | Descripción | Indicador visual |

|---|---|---|

| Señal de reloj | Proporciona el latido del sistema. Otras señales suelen muestrearse en relación con esta. | Patrón de onda cuadrada regular |

| Señal de datos | Transporta la información real que se está transfiriendo. | Transiciones irregulares basadas en la entrada |

| Señal de control | Gestiona el flujo de datos (por ejemplo, Habilitar, Selección de chip, Escritura). | Pulsos activos alto o activos bajo |

| Tiempo de preparación | La duración durante la cual los datos deben permanecer estables antes de un borde de reloj. | Distancia horizontal antes del borde |

| Tiempo de retención | La duración de los datos debe permanecer estable después de un borde del reloj. | Distancia horizontal después del borde |

Comprendiendo los parámetros clave de temporización ⚙️

Los parámetros de temporización definen las restricciones dentro de las cuales un circuito digital opera correctamente. Violar estos parámetros a menudo conduce a un comportamiento impredecible. A continuación se presentan las definiciones e implicaciones de las métricas más críticas.

1. Tiempo de preparación ⏳

El tiempo de preparación es la cantidad mínima de tiempo durante la cual la señal de datos debe mantenerse estable antes del borde activador de la señal de reloj. Si los datos cambian demasiado cerca del borde del reloj, el flip-flop puede no capturar correctamente el valor. Este es a menudo el requisito más crítico en diseños de alta velocidad, ya que determina la frecuencia máxima de operación.

2. Tiempo de retención ⏳

El tiempo de retención es la cantidad mínima de tiempo durante la cual la señal de datos debe mantenerse estable después del borde activador de la señal de reloj. A diferencia del tiempo de preparación, el tiempo de retención es generalmente independiente de la frecuencia del reloj. Depende del retardo interno del flip-flop y del retardo de propagación externo de la ruta de datos.

3. Retardo de propagación ⏳

Este es el tiempo que tarda una señal en viajar desde la entrada de un componente hasta su salida. Varía según la temperatura, el voltaje y las tolerancias de fabricación. En un diagrama de temporización, esto aparece como el retraso entre un cambio en una señal y el cambio resultante en otra.

4. Período y frecuencia del reloj ⏳

El período del reloj es la duración de un ciclo completo de la señal de reloj. La frecuencia es el inverso del período. Un período más corto significa una frecuencia más alta, lo que permite un procesamiento más rápido, pero estrecha la ventana para la estabilidad de la señal.

Preguntas frecuentes ❓

Los ingenieros a menudo se enfrentan a escenarios específicos que generan confusión. A continuación se presentan respuestas detalladas a las preguntas más urgentes sobre el análisis de temporización.

P: ¿Qué ocurre si se viola el tiempo de preparación? 🛑

Cuando no se cumple el requisito de tiempo de preparación, el flip-flop entra en un estado conocido como metastabilidad. En este estado, la salida no se establece inmediatamente en un nivel lógico alto o bajo válido. En cambio, puede oscilar o permanecer en un nivel de voltaje intermedio durante una cantidad de tiempo impredecible. Esto puede hacer que la lógica posterior lea un valor corrupto, lo que provoca errores del sistema o bloqueos. En casos graves, la metastabilidad puede propagarse a través de todo el circuito, causando un fallo funcional que es difícil de depurar.

P: ¿Cómo manejo el desfase del reloj? 🔄

El desfase del reloj ocurre cuando la señal de reloj llega a diferentes componentes en tiempos distintos. Esto puede ocurrir debido a longitudes de ruta variables o diferencias de carga. Para gestionar el desfase:

- Ruteo equilibrado: Asegúrese de que las trazas del reloj se ruten con longitudes y anchos similares.

- Bufferización: Utilice buffers de reloj para alimentar múltiples cargas de forma equilibrada.

- Margen de temporización: Diseñe el sistema con suficiente margen en los tiempos de preparación y retención para absorber variaciones menores del desfase.

P: ¿Cuál es la diferencia entre la temporización síncrona y asíncrona? ⚖️

En síncrono sistemas, todas las operaciones se coordinan mediante una única señal de reloj. Los diagramas de tiempo para estos sistemas muestran bordes de reloj regulares y repetitivos. En asíncrono sistemas, las señales desencadenan acciones sin un reloj global. Los diagramas de tiempo para estos sistemas muestran transiciones impulsadas por eventos, a menudo con mayor variación en los intervalos entre señales. Los diseños asíncronos son más difíciles de analizar, pero pueden ser más eficientes en consumo de energía en aplicaciones específicas de bajo consumo.

P: ¿Cómo afecta el jitter a un diagrama de tiempo? 📉

El jitter es la variación a corto plazo de una señal respecto a su posición ideal en el tiempo. En un diagrama de tiempo, esto se manifiesta como los bordes de la señal de reloj que aparecen ligeramente antes o después de lo que deberían. Un jitter excesivo reduce la ventana efectiva para capturar datos. Reduce efectivamente los márgenes de setup y hold, aumentando el riesgo de violaciones de tiempo. Las interfaces de alta velocidad requieren un control estricto del jitter para mantener la integridad de los datos.

P: ¿Puedo leer diagramas de tiempo sin un reloj? 🕵️

Sí, pero requiere un enfoque diferente. Los protocolos asíncronos como I2C o UART no siempre utilizan una línea de reloj compartida. En su lugar, dependen de tasas de baudios predefinidas o señales de intercambio de mensajes. En estos diagramas, debes observar las anchuras de los pulsos y el tiempo entre las transiciones para inferir la tasa de datos. Por ejemplo, en UART, la duración del bit de inicio define el tiempo para los bits de datos siguientes.

Lectura e interpretación de formas de onda 🔍

Interpretar un diagrama de tiempo requiere un enfoque sistemático. Escanear aleatoriamente las líneas con frecuencia conduce a detalles omitidos. Sigue este proceso para un análisis preciso.

- Identifica la referencia: Encuentra la señal de reloj o la señal de control principal. Todos los demás tiempos son relativos a esta.

- Verifica los estados activos: Determina si las señales son activas en alto o en bajo. Un pulso bajo podría significar «habilitado», mientras que un pulso alto significa «deshabilitado». Esto a menudo se indica mediante un símbolo de burbuja en el nombre del pin en los esquemas.

- Analiza la alineación de los bordes: Observa detenidamente dónde se alinean los bordes de datos con los bordes de reloj. Los datos deberían cambiar idealmente cuando el reloj esté estable (por ejemplo, en la fase baja) y permanecer estables durante el borde activo.

- Rastrea las dependencias: Sigue la relación causa-efecto. Si la señal A desencadena la señal B, debería haber un retraso claro entre ellas correspondiente al retardo de propagación.

- Verifica las anchuras de los pulsos: Asegúrate de que los pulsos activos sean lo suficientemente anchos para que el componente receptor los detecte. Un pulso demasiado estrecho puede filtrarse como ruido.

Errores comunes en la interpretación de diagramas ❌

Incluso los ingenieros con experiencia pueden malinterpretar diagramas si omiten detalles específicos. Evita estos errores comunes.

- Ignorar los niveles lógicos: Suponer que todas las señales son activas en alto sin verificarlo. Siempre consulta la hoja de datos o el esquema.

- Pasarse por alto los retardos de propagación: Suponer que las señales cambian instantáneamente. Los componentes del mundo real tienen tiempos de respuesta finitos.

- Leer incorrectamente las escalas de tiempo: No darse cuenta de la unidad de tiempo (nanosegundos frente a microsegundos). Una señal que parece estable en una vista lenta puede mostrar fallos en una vista rápida.

- Descuidar los estados de alimentación: Los diagramas de tiempo a menudo cambian cuando un dispositivo entra en modo de suspensión. Asegúrate de estar viendo la secuencia de tiempo activa.

Estrategias para un análisis preciso 🛠️

Para asegurar que su análisis de temporización sea sólido, adopte estas estrategias. Estos métodos ayudan a mantener la consistencia y reducen la posibilidad de error.

- Utilice líneas de cuadrícula:Alinee sus cursores o marcadores con las líneas de cuadrícula del diagrama para medir los intervalos de tiempo con precisión.

- Documente sus supuestos:Escriba la frecuencia de reloj supuesta y los niveles lógicos antes de comenzar el análisis. Esto evita la confusión más adelante.

- Cruce de referencias:Compare el diagrama de temporización con la lógica de la máquina de estados. Cada transición de estado debe tener un evento de temporización correspondiente.

- Simule variaciones:Considere escenarios de peor caso. ¿Qué sucede si la temperatura aumenta y los retrasos se incrementan? ¿Qué sucede si el voltaje disminuye y la capacidad de conducción disminuye?

- Enfóquese en las rutas críticas:Identifique la ruta más larga en su lógica. Esta ruta determina la velocidad máxima del reloj del sistema. Priorice el análisis de temporización para estas rutas específicas.

El impacto de las violaciones de temporización ⚠️

Comprender por qué la temporización es importante es crucial. Cuando ocurre una violación de temporización, el comportamiento físico del circuito cambia. La consecuencia más común es la corrupción de datos. Un registro podría capturar un ‘1’ cuando debería haber capturado un ‘0’. En protocolos de comunicación, esto da lugar a errores de enmarcado o paquetes perdidos. En sistemas de control, puede provocar comandos incorrectos para los actuadores, lo que podría causar daños físicos o riesgos de seguridad.

Además, las violaciones de temporización pueden causar fallas intermitentes. Un sistema podría funcionar perfectamente a temperatura ambiente pero fallar cuando se calienta. Esto ocurre porque los retrasos de propagación aumentan con la temperatura. Diseñar con márgenes de temporización suficientes tiene en cuenta estos cambios ambientales.

Mejores prácticas para diagramas de temporización 📝

Crear diagramas de temporización claros y precisos es una habilidad que mejora con la práctica. Siga estas pautas para producir diagramas que sean fáciles de entender para otros.

- Etiquete todo:Cada línea de señal debe tener un nombre claro. Evite etiquetas genéricas como ‘Señal 1’.

- Utilice una escala consistente:Mantenga una escala de tiempo uniforme en todo el diagrama, a menos que necesite ampliar un evento específico.

- Resalte los eventos críticos:Utilice colores diferentes o líneas más gruesas para marcar las ventanas de establecimiento y retención.

- Incluya anotaciones:Agregue notas de texto para explicar interacciones complejas o restricciones específicas.

- Verifique con las hojas de datos:Verifique siempre los parámetros de su diagrama contra las especificaciones oficiales del componente.

Consideraciones avanzadas: Dominios de reloj múltiples 🌐

Los sistemas modernos a menudo utilizan múltiples dominios de reloj. Por ejemplo, un procesador podría funcionar a 2 GHz mientras que un controlador de memoria funciona a 400 MHz. Los diagramas de temporización para estos sistemas se vuelven significativamente más complejos. Debe tener en cuenta:

- Muestreo entre relojes: Cómo los datos se mueven de una frecuencia a otra.

- Búferes FIFO:Cómo sincronizar el flujo de datos entre relojes asíncronos.

- Sincronización de reinicio:Asegurar que todos los dominios se reinicien de manera coordinada para evitar inconsistencias de estado.

Al analizar estos diagramas, busca la lógica de sincronización, como las señales de intercambio de mensajes o cadenas de sincronización. Estos componentes están diseñados específicamente para cerrar la brecha entre diferentes dominios de tiempo de forma segura.

Conclusión: La precisión es clave 🔑

Los diagramas de temporización son más que simples imágenes; son la prueba matemática de un sistema funcional. Definen los límites de fiabilidad y rendimiento. Al comprender los componentes fundamentales, parámetros y posibles problemas, puedes diseñar sistemas que funcionen correctamente en condiciones del mundo real. Prestar atención a los tiempos de preparación, tiempos de retención y tiempos de propagación separa un prototipo funcional de un producto listo para producción. La práctica continua en la lectura y creación de estos diagramas agudizará tu intuición técnica y mejorará tus resultados ingenieriles.

Recuerda que cada borde cuenta una historia sobre el flujo de información. Respeta el tiempo que tarda esa información en viajar, y tus diseños resistirán la prueba del tiempo.