En el mundo complejo de la ingeniería embebida, la precisión no es simplemente una preferencia; es una exigencia. Los diagramas de tiempo sirven como plano visual para comprender cómo las señales interactúan con el tiempo. Estas representaciones gráficas mapean niveles de voltaje, ciclos de reloj y transiciones de datos contra un eje temporal. Para los ingenieros que diseñan microcontroladores, sensores o interfaces de comunicación, dominar la lectura y creación de estos diagramas es esencial para garantizar la fiabilidad del sistema.

Sin una visión clara de las relaciones temporales, los componentes de hardware podrían no comunicarse, lo que provocaría corrupción de datos o fallos del sistema. Esta guía explora las aplicaciones prácticas de los diagramas de tiempo en diversos dominios dentro del desarrollo embebido, ofreciendo una profundización en su utilidad sin depender de herramientas de software específicas.

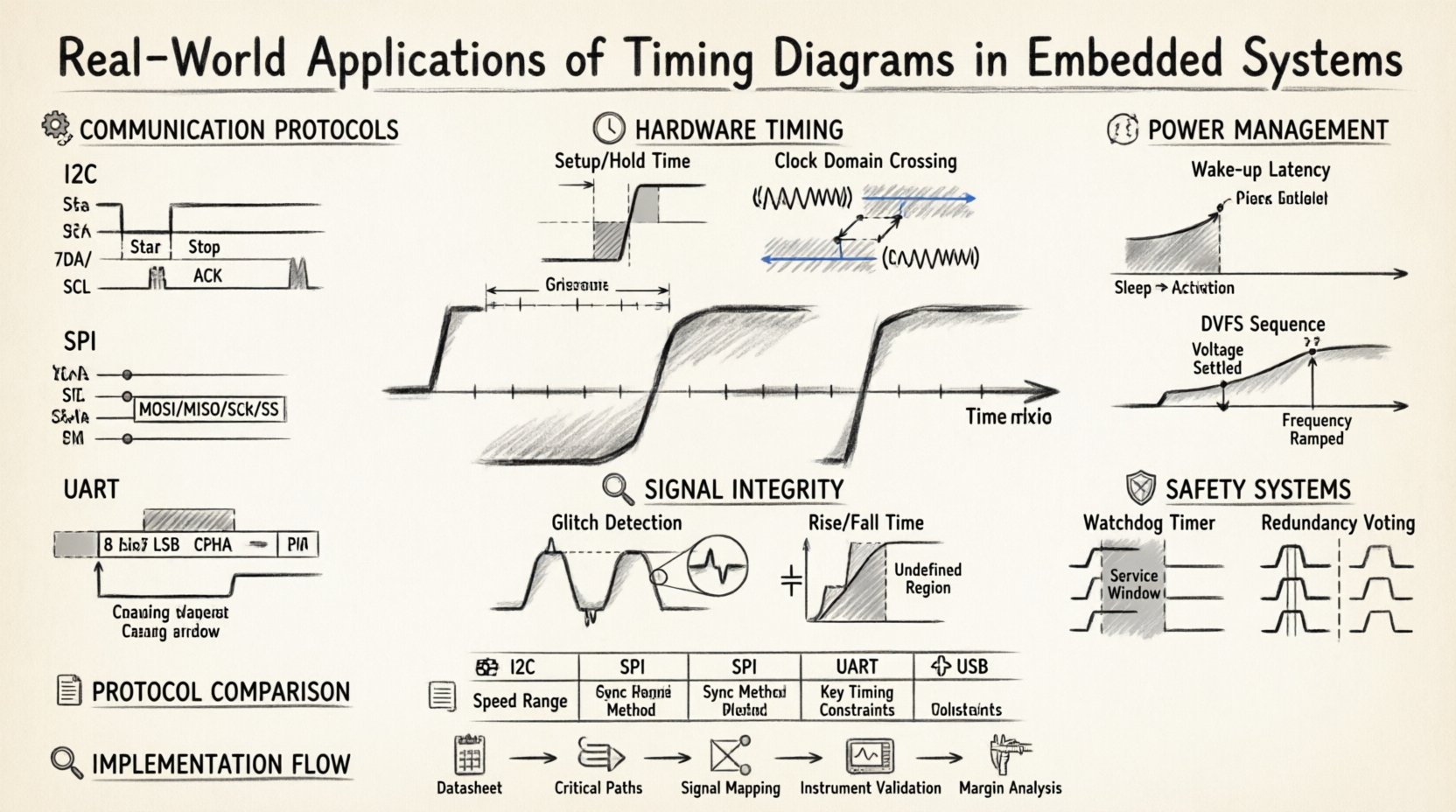

🔌 Análisis de protocolos de comunicación

La comunicación serial es la columna vertebral de los sistemas embebidos modernos. Los datos rara vez permanecen dentro de un solo chip; se mueven entre procesadores, memoria y periféricos. Los diagramas de tiempo son fundamentales para definir y verificar estas interacciones.

Circuito integrado interno (I2C)

El protocolo I2C utiliza una interfaz de dos hilos: Datos Serie (SDA) y Reloj Serie (SCL). Un diagrama de tiempo para I2C revela la secuencia específica requerida para la transmisión de datos.

- Condición de inicio: La línea SDA cambia de alto a bajo mientras la línea SCL permanece alta. Esto indica al bus que comience una transacción.

- Marco de dirección: El primer byte enviado contiene la dirección de 7 bits del dispositivo objetivo más un bit de lectura/escritura.

- Confirmación: El receptor baja la línea SDA durante el noveno pulso de reloj para confirmar la recepción.

- Condición de parada: La línea SDA cambia de bajo a alto mientras SCL está alto, liberando el bus.

Los ingenieros utilizan estos diagramas para detectar problemas como el estiramiento del reloj. Si un dispositivo esclavo no puede procesar los datos con suficiente rapidez, mantiene la línea SCL baja. El diagrama de tiempo muestra esta extensión, permitiendo al diseñador ajustar los bucles de procesamiento o los tamaños de los búferes.

Interfaz periférica serial (SPI)

SPI es un protocolo síncrono que a menudo se utiliza para comunicaciones de mayor velocidad. Involucra cuatro líneas: Maestro a Salida del Esclavo (MOSI), Maestro a Entrada del Esclavo (MISO), Reloj Serie (SCK) y Selección de Esclavo (SS).

- Polaridad del reloj (CPOL): Determina el estado inactivo de la línea de reloj. ¿Está alto o bajo antes de que comience la transmisión de datos?

- Fase del reloj (CPHA): Define cuándo se muestrea los datos. ¿En el primer o segundo borde del reloj?

- Tiempo de selección de chip: La línea SS debe permanecer baja durante toda la duración de la transacción. Si se produce un pico alto, la transacción se interrumpe.

Comprender estas fases es vital. Una discrepancia en CPOL o CPHA entre el maestro y el esclavo produce datos inválidos. Un diagrama de tiempo visualiza estos bordes, facilitando la detección de discrepancias durante el arranque del hardware.

Receptor/transmisor asíncrono universal (UART)

A diferencia de SPI e I2C, UART no utiliza una línea de reloj. La sincronización depende de tasas de baudios acordadas. Los diagramas de tiempo aquí se centran en la duración del bit y el marco.

- Bit de inicio: Un pulso bajo indica el inicio de un byte.

- Bits de datos: Típicamente 8 bits, transmitidos con el bit menos significativo (LSB) primero.

- Bit de parada:Un pulso alto indica el final del byte.

Los diagramas de tiempo ayudan a los ingenieros a calcular la ventana de tolerancia. Si los relojes de los dos dispositivos se separan demasiado, el punto de muestreo se desplaza, causando errores. El diagrama ilustra la ventana de muestreo, generalmente centrada en la mitad del tiempo de bit.

⏱️ Sincronización de hardware y tiempos de preparación

Más allá de la comunicación, los diagramas de tiempo son indispensables para comprender cómo interactúan las puertas lógicas y los flip-flops. La lógica digital depende de restricciones de tiempo precisas para funcionar correctamente.

Tiempo de preparación y tiempo de retención

Cuando los datos entran en un registro o flip-flop, deben cumplir requisitos específicos de tiempo respecto al borde del reloj.

- Tiempo de preparación:La duración mínima durante la cual los datos deben permanecer establesantesde que llegue el borde del reloj.

- Tiempo de retención:La duración mínima durante la cual los datos deben permanecer establesdespuésde que llegue el borde del reloj.

Si una señal viola el tiempo de preparación, el registro podría capturar un valor incorrecto. Si viola el tiempo de retención, puede ocurrir metastabilidad. Un diagrama de tiempo visualiza la señal de datos respecto al borde del reloj, destacando las zonas prohibidas donde no se permiten cambios en los datos.

Cruce de dominios de reloj (CDC)

Los sistemas complejos a menudo ejecutan diferentes partes de la lógica a frecuencias de reloj distintas. Mover datos desde un dominio de reloj rápido a uno lento, o viceversa, introduce riesgos.

- Sincronización:Utilizar una cadena de flip-flops para asegurar que la señal esté estable antes de usarla.

- Handshaking:Utilizar señales de solicitud y reconocimiento para coordinar la transferencia de datos sin un reloj compartido.

Un diagrama de tiempo para CDC muestra la secuencia de handshaking. Asegura que los datos sean válidos antes de que el dominio receptor los reconozca. Esto evita la pérdida de datos en transferencias asíncronas.

🔍 Depuración e integridad de señales

Cuando un sistema embebido se comporta de forma inesperada, los diagramas de tiempo suelen ser el primer lugar al que los ingenieros recurren. Proporcionan un registro histórico del comportamiento de las señales que las pruebas estáticas no pueden capturar.

Identificación de picos

Un pico es un pulso breve e involuntario en una línea de señal. Puede durar solo unos pocos nanosegundos, pero puede desencadenar un cambio de estado en un flip-flop.

- Condiciones de carrera:Ocurren cuando el orden de los eventos importa y el tiempo es demasiado ajustado.

- Retardo de propagación:Las señales tardan tiempo en atravesar las puertas lógicas. Los diagramas de tiempo muestran estos retrasos claramente.

Al superponer el diagrama de tiempo esperado con las señales reales capturadas, los ingenieros pueden identificar exactamente dónde ocurre la desviación. Esto permite realizar correcciones específicas en el firmware o en el diseño de hardware.

Margen de ruido y tiempos de subida/bajada

Las señales del mundo real no son ondas cuadradas perfectas. Tienen tiempos de subida y bajada debido a la capacitancia e inductancia en las trazas.

- Tiempo de subida: El tiempo que tarda una señal en pasar del estado bajo al alto.

- Tiempo de bajada: El tiempo que tarda una señal en pasar del estado alto al bajo.

Si estas transiciones son demasiado lentas, la señal podría pasar demasiado tiempo en la región de voltaje indefinido entre el lógico 0 y el lógico 1. Esto puede provocar que se activen múltiples bordes de reloj o errores lógicos. Un diagrama de tiempo ayuda a medir estas pendientes para asegurarse de que cumplan con las especificaciones del chip receptor.

💤 Gestión de energía y estados de bajo consumo

La eficiencia energética es una preocupación principal en dispositivos embebidos alimentados por batería. Los diagramas de tiempo desempeñan un papel clave en la optimización del consumo de energía.

Latencia de activación

Cuando un dispositivo entra en modo de suspensión, detiene el reloj para ahorrar energía. Activarse requiere restaurar el reloj y estabilizar el voltaje.

- Tiempo de transición: El tiempo que tarda en pasar del estado de suspensión al estado activo.

- Latencia: El retardo entre un evento de activación y la ejecución de código por parte del procesador.

Un diagrama de tiempo de la secuencia de encendido muestra el retardo entre la señal de activación y la estabilización del reloj del sistema. Esta información es crucial para aplicaciones en tiempo real donde un retardo de unos pocos milisegundos tiene importancia.

Escalado dinámico de voltaje y frecuencia (DVFS)

Los sistemas pueden ajustar el voltaje y la frecuencia según la carga de trabajo. Los diagramas de tiempo ayudan a verificar las transiciones entre diferentes estados de rendimiento.

- Pendiente de frecuencia: ¿El reloj cambia de forma suave o brusca?

- Estabilización de voltaje: ¿El voltaje está estable antes de aplicar la nueva frecuencia?

Una secuencia incorrecta durante el DVFS puede provocar caídas de voltaje (brownouts) o errores lógicos. El diagrama de tiempo proporciona la verificación de secuencia necesaria para garantizar transiciones seguras.

🛡️ Sistemas críticos para la seguridad

En aplicaciones automotrices, médicas e industriales, la seguridad es fundamental. Los diagramas de tiempo se utilizan para verificar que los mecanismos de seguridad funcionen dentro de los límites de tiempo requeridos.

Temporizadores de supervisión (watchdog)

Un temporizador de supervisión reinicia el sistema si el software se queda colgado. Los diagramas de tiempo definen el período de tiempo de espera (timeout).

- Período de tiempo de espera: El tiempo máximo permitido entre reinicios.

- Ventana de servicio: El tiempo que el software tiene para reiniciar el temporizador.

Si la ventana de servicio es demasiado larga, el perro de guardia podría activarse innecesariamente. Si es demasiado corta, una interrupción lenta podría causar un reinicio falso. El diagrama asegura que el tiempo se alinee con los requisitos de estándares de seguridad.

Redundancia y votación

Algunos sistemas utilizan múltiples procesadores para votar sobre la salida correcta. Los diagramas de tiempo aseguran que todos los procesadores alcancen la etapa de votación al mismo tiempo.

- Sincronización: Todos los canales deben alinear sus datos.

- Tiempo de espera: Si un canal llega tarde, el sistema debe detectar la discrepancia.

Esto es crítico en sistemas de control de frenos o dirección, donde un retraso puede ser peligroso. El diagrama de tiempo mapea la latencia de cada canal para asegurar que la lógica de votación funcione correctamente.

📋 Visión general de comparación de protocolos

La siguiente tabla resume las características clave de tiempo de las interfaces embebidas comunes para ayudar en la selección y el diseño.

| Protocolo | Rango de velocidad | Método de sincronización | Casos de uso típicos | Restricción de tiempo clave |

|---|---|---|---|---|

| I2C | 100 kHz a 3,4 MHz | Reloj compartido | Sensores, EEPROM | Estiramiento de reloj |

| SPI | 1 MHz a 50 MHz+ | Reloj maestro | Memoria flash, pantallas | Configuración de selección de chip |

| UART | 9600 a 921600 bps | Asincrónico | Depuración, GPS, Bluetooth | Tolerancia de tasa de baudios |

| USB | 1,5 Mbps a 20 Gbps | Basado en paquetes | Periféricos, Almacenamiento | Tiempo de token/manejo de señales |

🛠️ Pasos prácticos de implementación

Crear un diagrama de tiempos implica un enfoque sistemático. Comienza con la comprensión de la especificación y termina con la verificación.

- Revisar fichas técnicas:Cada componente tiene una sección de tiempos. Busque las tablas de características AC.

- Identificar rutas críticas: Determine qué señales dictan la velocidad máxima del sistema.

- Mapa de dependencias: Dibuje las relaciones entre las señales. ¿Cuál activa a la otra?

- Validar con instrumentos: Utilice analizadores lógicos o osciloscopios para capturar formas de onda reales.

- Analizar márgenes: Asegúrese de que haya suficiente tiempo entre las señales para tener en cuenta las variaciones de temperatura y voltaje.

La documentación es clave. Un diagrama de tiempos bien anotado sirve como referencia para el mantenimiento futuro. Explica por qué se agregaron ciertos retrasos o por qué se eligieron resistencias de pull-up específicas.

🚀 Consideraciones avanzadas

A medida que los sistemas se vuelven más complejos, el análisis de tiempos requiere una atención más profunda.

Jitter y ruido de fase

Los relojes no son perfectamente estables. El jitter es la desviación del borde del reloj respecto a su posición ideal. Los diagramas de tiempos muestran la variación en la colocación del borde a lo largo de múltiples ciclos.

- Jitter de período:Variación en el período del reloj.

- Jitter ciclo a ciclo:Variación de un ciclo al siguiente.

Un alto jitter reduce los márgenes de configuración y retención. En interfaces de alta velocidad como la memoria DDR, esto puede provocar errores de lectura/escritura. Los diagramas de tiempo ayudan a cuantificar este jitter para asegurarse de que permanezca dentro de límites aceptables.

Efectos térmicos

La temperatura afecta la velocidad de los transistores. A medida que un chip se calienta, las señales se ralentizan.

- Análisis del peor caso:Diseñe para la temperatura de operación máxima.

- Limitación térmica:Asegúrese de que el sistema no supere los límites térmicos seguros durante la operación de alta velocidad.

Un diagrama de tiempo creado a temperatura ambiente podría no ser válido a 85 °C. Los ingenieros deben tener en cuenta estos cambios térmicos para garantizar la robustez.

📝 Reflexiones finales

Los diagramas de tiempo son más que simples dibujos; son el lenguaje de la sincronización. Cerraran la brecha entre la lógica teórica y la realidad física. En los sistemas embebidos, donde el hardware y el software se entrelazan, una comprensión clara del tiempo de las señales evita reingenierías costosas y garantiza fiabilidad.

Ya sea que esté depurando un protocolo de comunicación, optimizando el consumo de energía o asegurando la seguridad en un sistema crítico, estos diagramas proporcionan la claridad necesaria para tomar decisiones informadas. Al centrarse en los tiempos de configuración, los retrasos de propagación y la integridad de la señal, los ingenieros pueden construir sistemas que funcionen de manera consistente en condiciones del mundo real.

La inversión en comprender las relaciones de tiempo se traduce en estabilidad y rendimiento. A medida que la tecnología avanza, los principios permanecen iguales. El tiempo es la constante, y dominar su medición es la clave para un diseño embebido exitoso.