在數位系統複雜的架構中,了解信號狀態變化的精確時刻至關重要。時序圖提供了信號隨時間演變的視覺化表示。它們是工程師、開發人員和設計師不可或缺的工具,用於驗證組件之間是否正確互動。若無這些視覺輔助,調試非同步通訊或驗證時鐘域將變成猜測遊戲。本指南探討時序圖在系統設計中的運作原理、優勢與應用。

什麼是時序圖? ⚙️

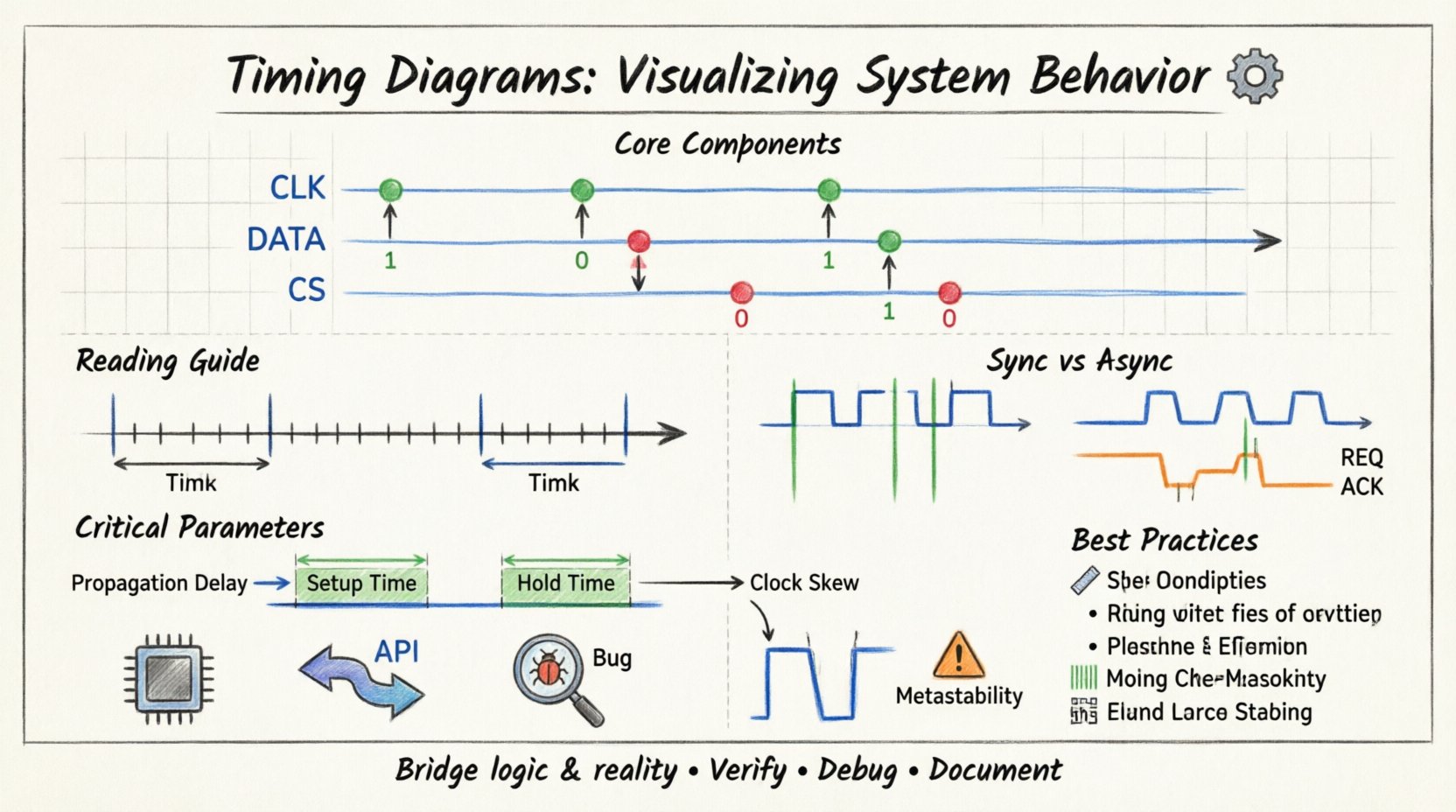

時序圖是一種圖表,用以顯示信號在一段時間內的行為。它將信號的邏輯狀態與時間軸對應起來。與顯示物理連接的電路圖不同,時序圖專注於事件之間的時間關係。它能回答諸如:信號A是否在信號B之前改變?時鐘脈衝是否足夠寬?資料需要多長時間才能穩定?等問題。

這些圖表在以下方面至關重要:

- 驗證硬體協定

- 記錄軟體邏輯互動

- 調試競爭條件

- 驗證時鐘與資料對齊

時序圖的核心元件 🧩

要有效解讀時序圖,必須理解其基本構成要素。每個圖表都由特定元素組成,用以傳達系統運作的資訊。

1. 時間軸 📏

水平軸代表時間,通常從左向右流動。比例可以是絕對的(奈秒、微秒)或相對的(時鐘週期)。在同步系統中,時間通常被劃分為與時鐘邊緣對應的離散步驟。

2. 訊號線 📡

每條線代表一個特定的訊號、導線或資料匯流排。這些線以名稱標示,例如CLK, DATA, CS(晶片選擇),或RST(重置)。線條的垂直位置用以區分不同訊號,避免混淆。

3. 邏輯電平 🟢🔴

訊號通常處於離散狀態。在數位邏輯中,這些狀態為高電平(邏輯1)與低電平(邏輯0)。時序圖顯示這些狀態之間的轉換。從低到高的轉換稱為上升沿,從高到低的轉換稱為下降沿。

4. 事件與轉換 🔄

事件是訊號狀態改變的特定時刻。這些時刻通常以垂直線或箭頭標示。重要事件包括時鐘邊緣、資料鎖存與確認訊號。這些事件之間的間距代表持續時間。

有效閱讀時序圖 👁️

閱讀這些圖表需要系統性的方法。誤解事件的順序可能導致設計缺陷。遵循以下原則以確保準確性。

- 由左至右: 始終從起點(左側)開始,向終點(右側)閱讀時間軸。這代表了操作的時間順序流動。

- 垂直對齊: 垂直對齊的事件同時發生。如果兩個信號在完全相同的垂直線上變更,則它們是並發的。

- 持續時間: 訊號狀態的水平長度表示其在該狀態中停留的時間長短。寬脈衝代表較長的持續時間。

- 依賴關係: 注意因果關係。一個訊號的變更通常會觸發另一個訊號。圖表顯示了這些觸發之間的延遲時間。

同步系統與非同步系統 🔄

時間圖形會因系統為同步或非同步而有顯著差異。理解此區別對於準確分析至關重要。

同步系統 ⏰

這些系統依賴於全局時鐘信號。所有狀態變更都發生在特定的時鐘邊沿(上升或下降)。圖表會顯示規律的時鐘模式。資料僅在時鐘允許時才被採樣。這使得時序可預測,但同時引入了建立時間和保持時間等限制。

非同步系統 🕰️

這些系統不依賴全局時鐘。狀態變更發生在輸入訊號變更時。此處的時間圖形較不規律。它們專注於握手協議。一個訊號必須先變高,然後另一個訊號變高,最後再回到低電平。這需要仔細分析延遲,以避免競爭條件。

時間分析中的關鍵參數 ⚙️

除了簡單繪製線條外,工程師還會分析特定參數以確保可靠性。這些參數定義了系統正確運作的時間窗口。

- 傳播延遲: 訊號通過元件從輸入到輸出所需的時間。此延遲會在邏輯閘之間累積。

- 建立時間: 在時鐘邊沿之前,資料必須保持穩定的最短時間。如果資料變更過晚,觸發器將無法正確捕獲。

- 保持時間: 在時鐘邊沿之後,資料必須保持穩定的最短時間。如果資料變更過早,當前值將丟失。

- 時鐘偏移: 時鐘信號到達不同元件的時間差異。高偏移可能導致建立時間或保持時間違規。

- 亞穩態: 一種觸發器輸出既非高電平也非低電平的狀態。當建立時間或保持時間被違反時會發生。時間圖形有助於可視化亞穩態的風險。

在硬體與軟體中的應用 🔌

時間圖形不僅限於硬體。它們也廣泛應用於軟體架構與協定設計中。

硬體設計

在硬體中,這些圖形用於驗證匯流排協定。例如,確認地址匯流排在讀取脈衝啟動前已穩定。它們確保記憶體存取時間與處理器時鐘速度匹配。它們也用於分析訊號轉換期間的電力消耗波峰。

軟體與協定

在軟體中,時序圖會映射 API 呼叫或訊息交換。它們顯示服務之間請求與回應的順序。這有助於識別分散式系統中的延遲問題。它們能釐清多執行緒環境中操作的順序。

常見的陷阱與錯誤 🛑

若未謹慎執行,建立或閱讀時序圖可能會導致錯誤。了解常見錯誤有助於提升準確性。

- 忽略低電平有效: 許多信號使用低電平有效的邏輯(反相)。一條訊號線下降至低電平可能表示該訊號處於有效狀態。務必檢查圖例或標籤。

- 假設瞬時轉換: 實際信號具有上升和下降時間。理想圖形顯示垂直線,但實際信號會呈斜坡。此斜坡會影響信號完整性。

- 忽略雜訊: 未達到最小寬度要求的短脈衝可能導致錯誤觸發。這些通常稱為雜訊。

- 誤解高阻態: 高阻態表示訊號已斷開。在圖形中,這看起來像虛線或特定符號。忽略此點可能導致匯流排競爭錯誤。

- 時鐘對齊錯誤: 假設所有時鐘都相位對齊,實際上並非如此。時鐘偏移可能導致資料被錯誤採樣。

圖形類型比較 📊

不同情境需要不同的視覺化方法。雖然時序圖功能強大,但並非唯一工具。

| 圖形類型 | 主要關注點 | 最適合用途 |

|---|---|---|

| 時序圖 | 時間與信號狀態 | 驗證時鐘/資料關係 |

| 狀態圖 | 系統狀態 | 定義邏輯流程與條件 |

| 順序圖 | 訊息順序 | 軟體互動與 API 呼叫 |

| 電路圖 | 物理連接 | 布線與元件佈局 |

| 波形檢視器 | 即時訊號 | 調試實際硬體行為 |

文件編寫的最佳實務 📝

為了讓時序圖對團隊和未來參考更具實用性,請遵循這些最佳實務。清晰的文件編寫能減少歧義,並加快調試速度。

- 標示所有項目: 每條訊號線都必須有明確的名稱。避免使用像 Sig1.

- 包含單位: 在軸上標示時間單位。我們是在觀察毫秒還是時鐘週期?

- 標記關鍵點: 明確標示建立時間與保持時間視窗。使用陰影或明顯的顏色來標記關鍵時序視窗。

- 保持整齊有序: 將相關的訊號分組。例如,所有控制訊號放在上方,資料訊號放在下方。

- 記錄假設: 記錄創建過程中所做的任何假設。例如,假設傳播延遲為零或特定負載條件。

- 使用一致的符號: 使用標準符號來表示上升沿、下降沿和高阻態。

建立圖表的逐步指南 🛠️

從零開始建立時序圖需要有結構化的方法。遵循以下步驟以確保完整性。

- 識別訊號: 列出所有參與互動的輸入和輸出。

- 確定順序: 定義事件的順序。是什麼觸發了這個過程?

- 設定時間尺度: 決定時間軸的細緻程度。

- 繪製時鐘: 如果是同步的,請先繪製時鐘訊號。它將成為圖表的基準。

- 加入資料: 將資料信號相對於時鐘邊緣繪製出來。

- 檢查約束條件: 根據繪製的信號驗證建立時間和保持時間。

- 檢視: 沿著時間軸走一遍,確保不存在邏輯上的缺口。

定時在除錯中的角色 🐞

當系統發生故障時,時序圖通常是工程師首先查看的地方。它們有助於區分問題是邏輯性的還是時序性的。如果邏輯正確但時序錯誤,系統會間歇性失敗。這通常比硬體邏輯錯誤更難重現。

除錯情境包括:

- 資料損壞: 在讀取期間信號發生變化。

- 錯過的中斷: 中斷信號太短而無法被偵測到。

- 匯流排競爭: 兩個裝置同時驅動匯流排。

- 時鐘域跨接: 信號在不同時鐘頻率之間移動,但未經過適當的同步。

理解資料寬度與對齊 📐

時序圖也用來呈現資料寬度。平行匯流排需要多條線路。每條線必須同步切換。錯位可能導致資料錯誤。圖表顯示了位元在一個時鐘週期內如何對齊。對於串列通訊,時序圖顯示位元流。它強調了位元週期和取樣點。

進階主題:抖動與雜訊 📉

現實世界的信號並非完美。抖動是指時鐘邊緣與理想位置的偏移。雜訊是信號電平的隨機波動。時序圖可透過在邊緣周圍顯示一條粗帶而非尖銳線條來表示抖動。這表示不確定性。設計人員必須確保系統能容忍這種不確定性。抖動帶與建立/保持時間視窗之間的間距即為安全餘量。

與測試套件的整合 🧪

時序圖不僅用於設計。它們還用來產生測試案例。自動化測試套件可檢查實際系統行為是否與圖表相符。如果測量到的時序偏離超出容許範圍,測試即失敗。這確保硬體或軟體在其整個生命周期中都符合規格。

關於系統可視化的結論 🎯

時序圖仍然是系統工程的基石。它們彌補了抽象邏輯與物理現實之間的差距。透過視覺化時間與信號的流動,工程師可以在故障發生前預測問題。它促進了硬體與軟體團隊之間的溝通。一張繪製良好的圖表所傳達的資訊,遠超過數頁文字。隨著系統變得更快、更複雜,對精確時序分析的需求也日益增加。掌握這些圖表能確保設計的穩健與可靠。

請記住,應優先考慮清晰度與準確性。避免做出假設。驗證每一處轉換。經過練習,閱讀與繪製這些圖表會成為設計過程中的直覺部分。它們是引導旅人穿越數位邏輯領域的地圖。