在數位電子與系統設計的世界中,時間不僅僅是一個維度;它是一個關鍵參數,決定了電路是否能正確運作,或會災難性地失敗。時序圖作為工程師用來溝通信號隨時間變化行為的視覺語言。無論你是設計微控制器介面、除錯記憶體匯流排,還是分析高速資料傳輸,理解這些圖表都是不可或缺的。

本指南探討時序圖的運作機制,將複雜的信號行為分解為易於理解的組成部分。我們將從基本定義出發,逐步深入進階分析技術,確保你具備精確解讀波形的工具。

🔍 什麼是時序圖?

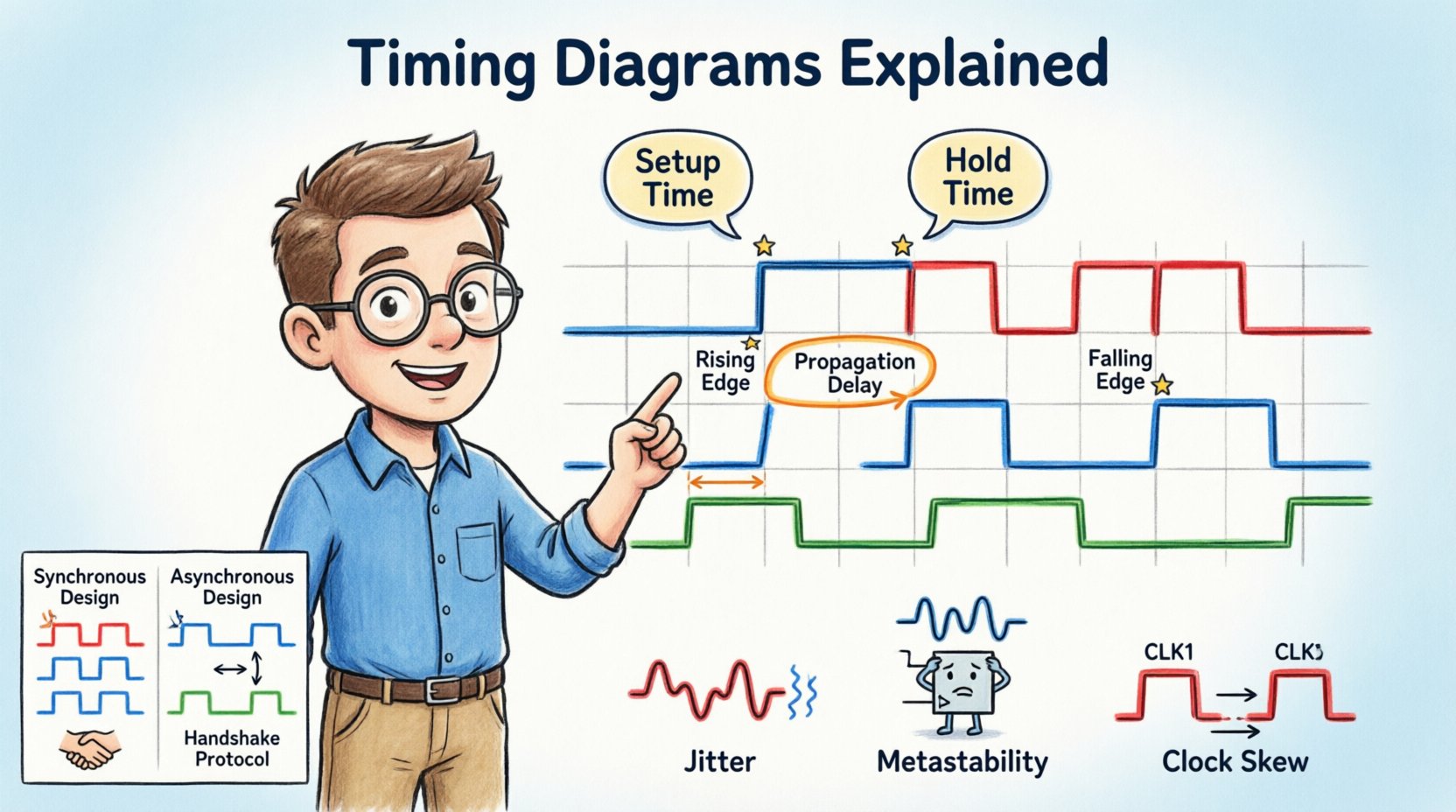

時序圖是數位系統中信號變化序列的圖形化表示。與顯示元件連接方式的電路圖不同,時序圖呈現的是何時這些連接狀態改變的時機。它沿著水平的時間軸標示信號活動,讓設計者能夠確認資料在時鐘邊緣前是否穩定,或控制信號是否在正確時刻被激活。

這些圖表對於以下用途至關重要:

- 驗證硬體與軟體的互動。

- 除錯通訊協定。

- 確保建立時間與保持時間的要求得以滿足。

- 記錄系統行為,以利未來維護。

若對時序缺乏清晰理解,即使邏輯正確的電路,仍可能因信號競速或亞穩態而失敗。

🛠️ 時序圖的核心元件

要有效閱讀時序圖,必須辨識其基本構成單元。每個元件都承載著關於數位系統狀態與流程的特定資訊。

1. 時間軸

水平線代表時間的推進。通常由左向右流動。在詳細的技術文件中,此軸可能標示具體的時間單位(奈秒、皮秒)或時鐘週期。

2. 訊號線

垂直線代表單獨的訊號,例如時鐘線、資料匯流排或控制線(如晶片選擇或讀寫)。每條線對應電路中的特定節點。

3. 邏輯電平

訊號通常處於兩種狀態之一:

- 高電平(邏輯1 / VCC):通常以訊號軌道頂端的線條表示。

- 低電平(邏輯0 / GND):以訊號軌道底端的線條表示。

某些系統使用主動低邏輯,其中訊號在電壓低時執行其功能。在圖表中,這通常以訊號名稱旁的圓圈或特定符號標示。

4. 遷移

遷移是指信號從高電平轉變為低電平或從低電平轉變為高電平的時刻。

- 上升沿:從低電平到高電平的轉變。對於觸發事件至關重要。

- 下降沿:從高電平到低電平的轉變。用於特定的控制序列。

- 邊沿觸發:信號僅在轉變期間被評估,而非穩定狀態期間。

⚙️ 關鍵時序參數

精確的數位設計依賴於量化信號之間的關係。以下參數是時序分析的基石。

1. 傳播延遲(tpd)

這是信號從邏輯閘或元件的輸入傳播到輸出所需的时间。沒有信號會瞬間改變;物理限制會導致延遲。

- 重要性:如果延遲過長,後續邏輯可能接收資料過晚,導致錯誤。

- 測量方式:從輸入轉變的50%電壓點測量至輸出轉變的50%電壓點。

2. 建立時間(tsu)

建立時間是指資料信號必須保持穩定的最短時間在時鐘邊沿到達之前。

- 情境:如果觸發器需要在時鐘觸發前5納秒就準備好資料,那麼這就是建立時間。

- 違反:如果資料在時鐘邊沿附近過於接近地改變,系統將無法正確捕捉該值。

3. 保持時間(th)

保持時間是指資料信號必須保持穩定的最短持續時間在時鐘邊沿到達後。

- 情境:觸發器需要在觸發後的一段短暫時間內「看見」資料,以穩固地鎖存它。

- 違規:如果資料在時鐘邊沿後立即改變,輸入可能無法正確鎖存。

4. 時鐘偏移

當時鐘信號在不同元件上以不同時間到達時,就會發生時鐘偏移。這通常是因為印刷電路板上的走線長度差異所致。

- 正偏移:時鐘在目的地較晚到達。

- 負偏移:時鐘在目的地較早到達。

5. 震盪

震盪是指信號的重要時刻在時間上與理想位置的短期變化。它會為時序分析增加不確定性。

📊 比較:同步設計與非同步設計

理解這兩種設計哲學之間的差異,對於正確解讀時序圖表至關重要。

| 特徵 | 同步時序 | 非同步時序 |

|---|---|---|

| 控制信號 | 使用全域時鐘 | 使用握手信號 |

| 可預測性 | 高度可預測 | 依負載而變 |

| 複雜度 | 需要時鐘分配 | 需要複雜的握手邏輯 |

| 功耗 | 可能較高(時鐘切換) | 通常較低(活動驅動) |

| 時序圖 | 與時鐘邊沿對齊 | 取決於前一狀態的完成 |

🧐 如何閱讀與分析時序圖

分析波形需要系統性的方法。遵循以下步驟,以確保不會遺漏關鍵細節。

步驟 1:識別時鐘

找出主要的時鐘信號。這通常是所有其他時序的參考。在同步系統中,每個資料轉換理應以該時鐘邊沿為參考。

步驟 2:檢查毛刺

在信號線上尋找短暫的、非預期的脈衝(毛刺)。這些可能導致邏輯閘的錯誤觸發。在乾淨的圖中,轉換應清晰,但實際的訊號捕捉通常會顯示雜訊。

步驟 3:驗證建立與保持時間視窗

在活躍的時鐘邊沿周圍畫出虛擬的垂直線,代表建立與保持時間視窗。確保資料信號在這些區域內穩定。

步驟 4:檢查控制信號

確保像晶片選擇(CS)或使能(EN)之類的控制信號在整個資料傳輸期間都保持有效。如果控制信號在資料仍在傳輸時下降,就會導致資料損壞。

步驟 5:測量間隔

計算特定事件之間的時間。例如,測量從「請求」信號到「回應」信號的延遲。這有助於根據規格驗證性能。

🚀 時序分析中的進階概念

隨著系統變得更快且更複雜,基本的時序圖逐漸演變為複雜的分析需求。

1. 靜態不穩定

當觸發器接收到違反建立或保持時間要求的輸入時,就會發生靜態不穩定。輸出不會明確地轉為 0 或 1,而是進入一個未定義的狀態,持續時間不可預測。

- 原因:通常發生在異步信號跨越時鐘域時。

- 緩解措施:使用同步鏈(串聯多個觸發器)來降低靜態不穩定的機率。

- 視覺表現:在時序圖中,這看起來像信號振盪,或花費異常長的時間才穩定下來。

2. 建立與保持時間預算

工程師會計算時序預算,以確保系統能在最高頻率下運作。這包括從時鐘週期中減去所有延遲(線路、邏輯閘、時鐘偏移)。

如果總延遲超過可用時間,則必須降低最大工作頻率。

3. 高速介面時序

像DDR記憶體或PCIe之類的介面需要極其精確的時序。這些圖表通常包括:

- 眼圖: 多個訊號轉換的疊加,以視覺化訊號品質。

- 佔空比失真: 確保高電平與低電平時間保持平衡。

- 相位對齊: 確保多個位元上的資料與時鐘訊號同步到達。

4. 電源管理狀態

現代裝置會進入低功耗模式。時序圖必須考慮啟動延遲。例如,向周邊設備提供電源的訊號必須在裝置準備好接收資料之前發生。

📝 文件編寫的最佳實務

清晰的文件編寫可防止開發與除錯過程中的錯誤。在建立或審查時序圖時,請遵守這些標準。

- 一致的縮放: 在相關圖表之間使用一致的時間尺度,以便於輕鬆比較。

- 清晰的標籤: 每個訊號都必須標示其功能與邏輯極性(例如,

RESET#表示低電平有效)。 - 縮放層級: 提供高階概覽以及關鍵轉換(如建立/保持時間窗)的放大視圖。

- 顏色編碼: 使用顏色區分不同的電壓域或時鐘來源(例如,紅色代表時鐘,藍色代表資料)。

- 版本控制: 時序需求會變更。確保圖表已版本化,以符合硬體版本。

🛠️ 常見陷阱與故障排除

即使經驗豐富的工程師也會遇到時序問題。以下是一些常見情境及其解決方法。

陷阱1:忽略走線延遲

PCB走線具有物理長度,會導致延遲。在高頻率下,幾英寸的導線可能等於一個時鐘週期。

- 解決方案: 在您的時序預算計算中考慮走線長度。

陷阱 2:浮動輸入

未連接的輸入端可能浮動至中間電壓,導致振盪。

- 解決方案: 確保所有輸入端都有明確的上拉或下拉電阻。

陷阱 3:競態條件

當兩個信號同時變更時,到達順序決定了結果。

- 解決方案: 使用同步邏輯或狀態機來排序事件。

陷阱 4:過衝與下衝

信號反射可能導致電壓超過電源軌(過衝)或低於地電位(下衝)。

- 解決方案: 實施適當的終端電阻和阻抗匹配。

🔗 實際應用

時序圖被應用於工程的各個領域。

1. 記憶體介面

DRAM 和 SDRAM 對讀/寫操作需要嚴格的時序序列。CAS 延遲與 RAS 到 CAS 的延遲是這些圖表中顯示的關鍵參數。

2. 微控制器通訊

I2C、SPI 和 UART 等協定依賴於時鐘線與資料線之間的特定時序關係。例如,在 I2C 中,時鐘為高電平期間資料線必須保持穩定。

3. 電源供應排序

複雜系統要求電源軌按特定順序啟動。時序圖確保核心電壓穩定後才施加 I/O 電壓。

🎯 重點總結

掌握時序圖需要耐心與細心。以下要點總結了有效設計與分析所需的關鍵知識。

- 時間至關重要: 數位邏輯依賴於信號之間精確的時間關係。

- 建立與保持: 這兩個是最常見的限制條件,決定了最大運作速度。

- 視覺驗證: 圖表讓您在硬體建構前就能察覺潛在衝突。

- 情境至關重要: 始終考慮影響信號時序的物理環境(PCB、溫度、電壓)。

- 標準化: 使用標準符號和表示法,以確保團隊之間的溝通清晰明確。

透過應用這些原則,您能確保數位系統具備強韌性、可靠性和高效能。能夠解讀並製作這些圖表是一項基本技能,可區分出能在現場正常運作的設計與會失敗的設計。

📈 展望未來

隨著技術的進步,時序限制變得更加嚴苛。現代系統以吉赫茲速度運作,納秒級的差異至關重要。從事尖端硬體開發的工程師必須持續學習信號完整性和時序收斂相關知識。

從分析現有的電路圖及其對應的時序圖開始。練習測量時間間隔並識別違反情況。隨著時間推移,這些模式將變得直覺,讓您能在問題實際出現前預測其發生。