在數位系統的架構中,資訊流動由時間所主導。時序圖不僅僅是一張圖紙;它是設計意圖與實際實現之間的合約。當訊號未能在精確的時間窗內對齊時,競爭條件便會出現,資料損毀發生,系統可靠性亦隨之崩潰。本指南提供了一套嚴謹的框架,用以驗證時序模型,確保每一項轉換、邊緣與約束都能反映硬體的實際運作狀況。

時序表達的準確性,正是功能原型與現場失效之間的差別。無論是定義通訊協定或規格化暫存器行為,時序圖的清晰度直接決定了驗證與實作階段的成功。本檢查清單列出了維持時序模型高保真度所必需的關鍵要素。

為何時序圖的準確性至關重要 🎯

時序圖在有限狀態機、匯流排協定與介面邏輯的實作過程中,是工程師的主要參考依據。它將抽象的邏輯轉化為物理矽片必須遵守的時間約束。這些模型中的不準確性,通常源自對非同步事件的過度簡化描述,或訊號狀態未明確定義。

時序文件中的錯誤會在整個開發生命週期中不斷擴散。時鐘邊緣定義不符,可能導致建立時間違規。重置極性不明確,則可能導致系統啟動至未定義狀態。在設計階段修正時序錯誤的成本,遠低於進行晶片重製或現場部署韌體修補的成本。

維持嚴格準確性的關鍵原因包括:

- 驗證一致性:模擬測試環境依賴這些圖表產生激勵訊號。若圖表有誤,測試環境將驗證出錯誤的行為。

- 實作一致性:硬體描述語言程式碼必須與時序規格相符。差異將導致合成警告與時序收斂失敗。

- 相容性: 在與外部元件介接時,時序餘量可確保不同系統之間的可靠通訊。

- 除錯效率: 當系統發生故障時,準確的時序圖可提供根本原因分析的基準。

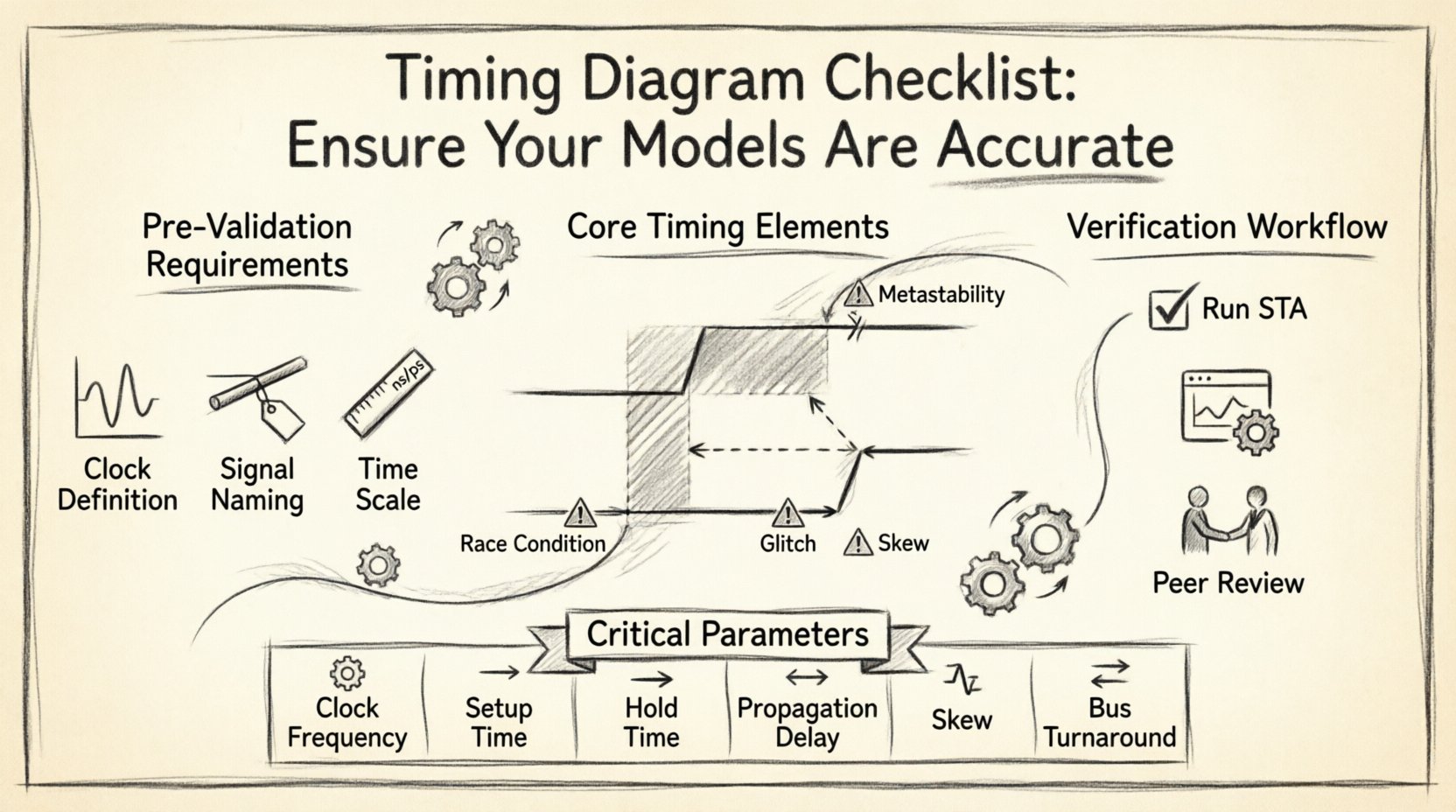

預驗證需求 ✅

在審查圖表本身之前,必須先建立訊號周圍的背景脈絡。沒有脈絡的圖表僅是一堆毫無意義的線條。在進入訊號層級檢查清單之前,請確保以下基礎要素均已明確定義。

1. 系統時鐘定義

每個同步系統都依賴時鐘來源。圖表必須明確指出頻率、相位關係與佔空比。此處的模糊性將導致時鐘域跨接問題。

- 時鐘頻率是否以赫茲為單位明確標示?

- 是否存在多個時鐘域?若是,是否已明確區分標示?

- 所有順序元件的時鐘邊緣是否已明確定義(上升沿或下降沿)?

2. 訊號命名規範

命名的一致性可避免程式碼實作時的誤解。訊號應遵循標準命名規範,以明確表示類型、方向與極性。

- 一致地使用主動高或主動低標示。

- 確保匯流排訊號邏輯分組(例如:DATA[7:0])。

- 避免使用如 Sig1 或 Ctrl 缺乏上下文。

3. 時間尺度與單位

橫軸代表時間。若無明確的單位,此圖表對時序分析將毫無用處。

- 請指定時間單位(ns、ps、µs、時鐘週期)。

- 確保刻度為線性,除非圖表明確標示某特定事件的放大視圖。

- 以規律間隔標示時間標記,以利測量。

核心時序元素檢查清單 📋

本節詳細說明必須驗證的特定信號特性。若未明確定義,每一項都可能成為潛在的失敗點。

1. 訊號狀態與電平

數位訊號存在離散狀態。圖表必須明確顯示何謂邏輯一、邏輯零,以及高阻抗狀態。

- 邏輯電平: 使用的是電壓電平還是邏輯狀態(0/1)?請確保文件中的一致性。

- 高阻抗狀態: 對於三態匯流排,圖表必須顯示轉換至高阻抗狀態的過程。這對於防止匯流排競爭至關重要。

- 未定義狀態: 若訊號可能進入浮動或未知狀態,必須予以標示。切勿假設預設值。

2. 轉換邊緣

訊號狀態改變的瞬間是數位邏輯中最關鍵的時刻。時序違規通常發生在這些邊緣。

- 上升沿: 明確標示從低電平到高電平的轉換。

- 下降沿: 明確標示從高電平到低電平的轉換。

- 上升率: 雖然經常被抽象化,但轉換的陡度可能影響時序餘量。若因負載電容導致轉換緩慢,請予以標示。

- 雜訊脈衝: 若訊號容易產生暫態雜訊脈衝,必須明確標示。若訊號雜訊較多,切勿畫出乾淨的線條。

3. 建立與保持時間

對於正反器與鎖存器,資料必須在時鐘有效邊緣前後保持穩定。這些限制在同步設計中不可妥協。

- 建立時間(tsu): 數據必須在時鐘邊沿之前保持穩定的最短時間。

- 保持時間 (th): 數據必須在時鐘邊沿之後保持穩定的最短時間。

- 違反邊界: 在圖中包含安全裕量,以考慮製程變異和溫度變化。

4. 延遲與延遲

信號傳播並非瞬間完成。延遲會在邏輯門和互連之間累積。

- 指定輸入與輸出之間的傳播延遲。

- 考慮路徑中的組合邏輯延遲。

- 說明延遲是最壞情況、典型情況還是最佳情況。

信號完整性與電平 🔌

信號完整性涵蓋信號在系統中傳輸時的品質。在時序圖中,這通常以波形的清晰度來表示。

1. 雜訊與抖動

現實中的信號會受到雜訊影響。顯示完美邊沿的時序圖在理論上雖有幫助,但實際上具有誤導性。

- 抖動: 信號邊沿時序的變化。高抖動會降低有效的時序裕量。

- 雜訊底層: 如果信號在接近雜訊閾值的情況下運作,圖中應反映不確定性範圍。

- 取樣視窗: 定義接收器取樣信號的時間視窗。此視窗必須能容納抖動。

2. 電源供應依賴性

信號時序會根據電壓水平而變化。電源波動可能導致時序漂移。

- 指定相關元件的運作電壓範圍。

- 說明在不同電壓條件下(例如低電壓運作)時序限制是否會改變。

- 在時序模型中考慮斷電與上電的順序。

表格:關鍵時序參數參考

| 參數 | 定義 | 錯誤的影響 | 驗證方法 |

|---|---|---|---|

| 時鐘頻率 | 每秒時鐘週期的速率 | 系統速度不匹配,資料遺失 | 頻率計,示波器 |

| 建立時間 | 資料必須在時鐘邊緣前保持穩定的時間 | 亞穩態,錯誤的資料捕獲 | 靜態時序分析 |

| 保持時間 | 資料必須在時鐘邊緣後保持穩定的時間 | 亞穩態,資料損壞 | 靜態時序分析 |

| 傳播延遲 | 信號從輸入傳送到輸出所花的時間 | 時序違規,競態條件 | 模擬波形 |

| 偏移 | 時鐘到不同暫存器的到達時間差異 | 時序餘量減少,時鐘域問題 | 時鐘樹分析 |

| 匯流排切換時間 | 從驅動器狀態切換到接收器狀態的時間 | 匯流排競爭,資料衝突 | 信號完整性模擬 |

時鐘域與同步 ⏲️

現代系統通常在多個時鐘域之間運作。跨越這些邊界會引入顯著的複雜性,這必須在時序圖中加以呈現。

1. 多時鐘情境

當信號從一個時鐘域跨越到另一個時鐘域時,必須定義時鐘之間的關係。

- 頻率比:其中一個時鐘是否為另一個時鐘的倍數?

- 相位關係:時鐘是否對齊,還是存在固定的相位偏移?

- 異步時鐘:如果時鐘彼此無關,圖示必須標示出需要同步邏輯(例如,同步器、FIFO)。

2. 靜態不穩定處理

當異步信號進入同步系統時,可能導致靜態不穩定。時序圖應考慮所需的恢復時間。

- 指定靜態不穩定的恢復時間。

- 標示多級同步器的使用。

- 定義應用可接受的失敗機率。

3. 時鐘門控

為了節省電力,當邏輯處於空閒狀態時,時鐘通常會被關閉。這會引入時序複雜性。

- 顯示時鐘門控的使能信號。

- 定義觸發門控時鐘所需的最小脈衝寬度。

- 確保門控邏輯不會引入毛刺。

狀態轉換與重置邏輯 🔄

邏輯行為由狀態轉換定義。時序圖必須準確反映系統在狀態之間的轉移方式以及其初始化方式。

1. 重置序列

每個數位系統都需要一個明確的起始狀態。重置信號對此至關重要。

- 有效電平:重置信號是高電平有效還是低電平有效?

- 脈衝寬度:重置信號必須保持有效的時間有多長,才能確保所有暫存器被清除?

- 釋放順序:如果存在多個重置信號,是否有一個特定的釋放順序?(例如,核心重置在I/O重置之前)。

- 異步與同步:重置是立即清除,還是等到下一個時鐘邊緣才清除?

2. 狀態機轉換

有限狀態機(FSM)定義了操作邏輯。時序圖應標示出狀態轉換的條件。

- 識別觸發狀態變化的輸入條件。

- 顯示與每個狀態相關的輸出持續時間。

- 標示任何非法狀態及其系統處理方式。

3. 握手協議

許多介面使用握手來管理資料流。這些信號的時序至關重要。

- 請求(REQ): 數據何時準備好可以發送?

- 確認(ACK): 接收端何時確認收到?

- 逾時: 如果握手未在特定時間內完成,會發生什麼情況?

驗證與交叉核對 🔍

圖表繪製完成後,必須經過嚴格的審查流程。這包括將圖表與模擬結果及物理限制進行比對。

1. 模擬波形比對

使用圖表中定義的時序約束執行模擬。將實際輸出波形與預期圖表進行比對。

- 信號邊沿是否如預期般與時鐘邊沿對齊?

- 模擬中是否滿足建立時間與保持時間?

- 資料值是否與預期序列相符?

2. 靜態時序分析(STA)

STA 工具在不執行模擬的情況下分析時序路徑。它們提供時序正確性的數學證明。

- 檢查 STA 引擎報告的時序違規情況。

- 審查關鍵路徑的餘量值。

- 確保圖表中的時序約束與分析工具所使用的約束檔案一致。

3. 同行審查

人工審查對於發現工具可能忽略的邏輯錯誤至關重要。

- 請第二位工程師審查圖表的清晰度與一致性。

- 檢查命名規範與單位的一致性。

- 確認圖表與架構規格相符。

常見的時序違規 🚫

即使有檢查清單,錯誤仍會發生。熟悉常見的陷阱有助於預防和故障排除。

1. 競爭條件

當一個信號的輸出取決於其他信號到達的順序時就會發生。

- 避免兩條信號以不同時序驅動同一個節點的邏輯。

- 確保反饋迴路被打破或正確同步。

- 檢查是否存在傳遞延遲差異極大的邏輯路徑進入同一個暫存器。

2. 靜態不穩定

當信號在時鐘邊沿附近過於接近地改變時,觸發器可能無法穩定為 0 或 1。

- 最小化異步輸入觸及取樣邊沿的機率。

- 對任何外部輸入都使用同步器。

- 針對最壞情況下的抖動和偏移進行設計。

3. 閃爍

由邏輯傳播延遲引起的意外脈衝。

- 確保組合邏輯不會直接輸入到敏感的控制線路。

- 使用時鐘門控邏輯,以防止閃爍訊號到達時鐘樹。

- 確認使能信號在時鐘邊沿前已穩定。

4. 時鐘偏移

時鐘在不同時間到達不同的暫存器。

- 最小化時鐘分配網絡中的偏移。

- 在建立時間和保持時間計算中考慮偏移。

- 使用緩衝時鐘樹以保持均勻性。

文件記錄與維護 📝

時序圖是一份活文件。隨著設計的演進,圖表必須更新以反映變更。

1. 版本控制

追蹤時序圖隨時間的變更。

- 在文件中包含修訂歷史表格。

- 與程式碼一同進行時序圖文件的版本控制。

- 記錄每次變更的原因(例如:「更新以反映新的時鐘頻率」)。

2. 上下文註解

在圖表中添加註解以解釋複雜行為。

- 使用文字方塊來解釋特定的時序窗口。

- 參考規格中相關的章節。

- 包含有關關鍵限制的警告。

3. 移交至實作

確保建構系統的團隊擁有正確版本的圖表。

- 以所有利害關係人都能存取的格式提供圖表。

- 與實作團隊進行走查會議。

- 收集實作團隊的反饋,以改善未來的圖表。

關於時序嚴謹性的最後想法 🛡️

建立精確的時序圖是一項需要細心關注與深入理解基礎技術的學問。僅僅畫線是不夠的;必須理解支配這些線條的物理與邏輯。遵循此檢查清單,可確保你的模型具備強韌性、可靠性,並準備好投入實作。

投入驗證時序圖的精力,將在減少除錯時間與提升系統品質方面帶來回報。在利潤微薄、成本高昂的產業中,精確性是你所擁有的最寶貴資產。請以應有的嚴肅態度對待每一條邊緣與每一段延遲。

請記住,圖表是真理的來源。若圖表有誤,設計便有誤。保持圖表的準確性,維持設計的功能性,並確保系統順利運行。