在數位電子與硬體工程領域,元件之間的通訊依賴於精確的協調。若無法清楚掌握信號狀態變化的時機,系統將會失敗。時序圖正是這種協調的藍圖。它以時間為軸,呈現信號之間的關係,揭示資料是否有效、穩定且準備就緒以供處理。本指南針對工程師與學生在分析這些關鍵視覺工具時所面臨的基本問題進行解答。

無論您是在設計微控制器介面、除錯通訊協定,還是研究數位邏輯,理解設計中的時間特性都是不可或缺的。本文探討時序圖的結構組成,解釋關鍵參數,並回答有關信號完整性與同步的常見問題。

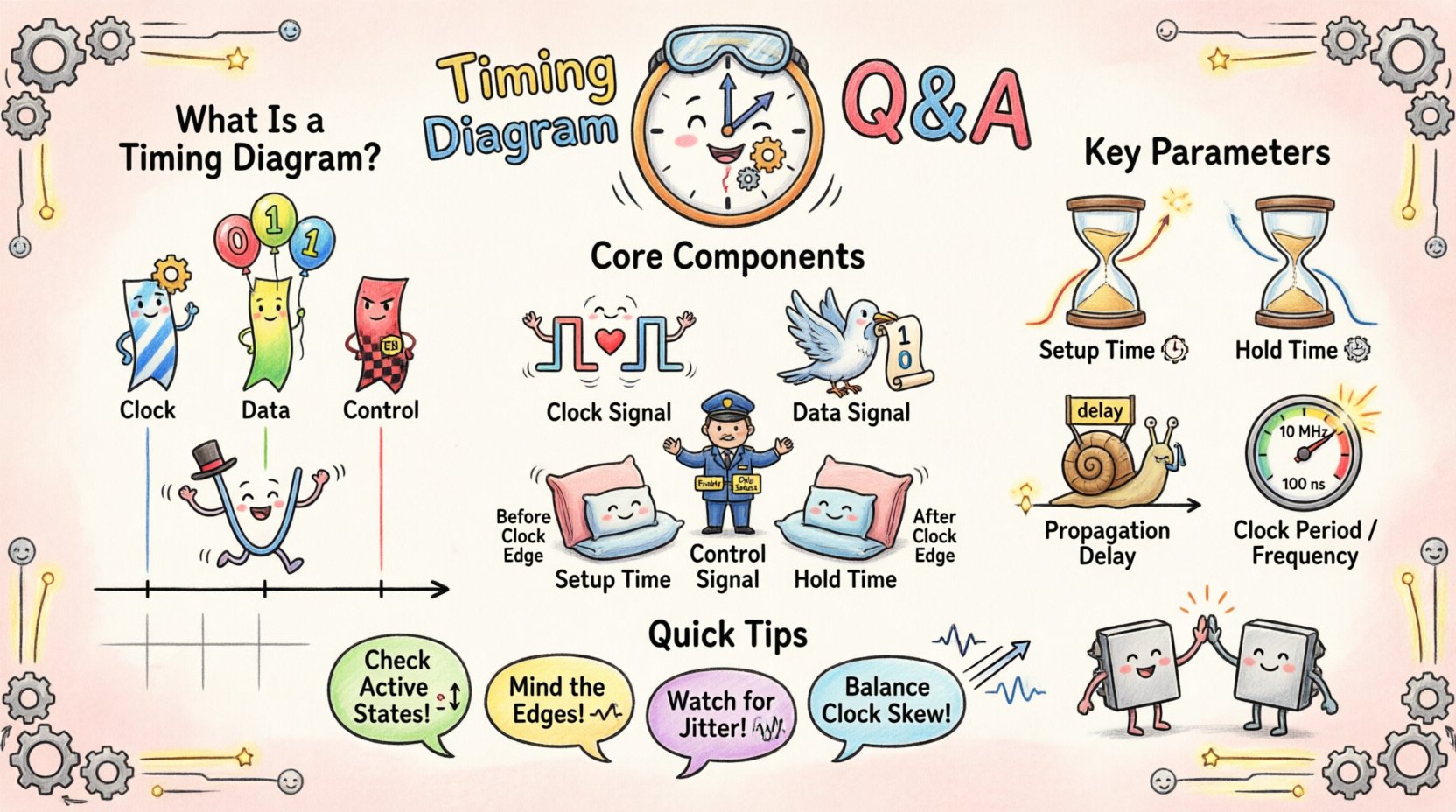

什麼是時序圖呢? 📊

時序圖是系統中事件序列的圖形化表示。它將信號電平繪製在水平的時間軸上。與僅顯示連接關係的邏輯圖不同,時序圖呈現的是行為。它讓您能夠觀察到某個信號是在另一個信號之前或之後轉為高電平或低電平。這種視覺背景對於確認接收端在下一個時鐘邊緣到來前,是否擁有足夠時間讀取資料至關重要。

主要特徵包括:

- 時間軸: 通常從左向右水平運行。

- 訊號線: 表示單獨導線或資料匯流排的水平線。

- 邏輯電平: 高(1)與低(0)狀態以明確的電壓平台表示。

- 邊緣: 垂直線,表示從一個狀態轉換到另一個狀態。

時序圖的核心元件 🧩

要有效閱讀這些圖表,必須辨識構成波形的標準元件。每個元件都在系統同步中扮演特定角色。

| 元件 | 描述 | 視覺指示 |

|---|---|---|

| 時鐘信號 | 為系統提供心跳信號。其他信號通常以此為基準進行取樣。 | 規律的方波模式 |

| 資料信號 | 傳輸實際的資訊內容。 | 根據輸入而產生不規則的轉換 |

| 控制信號 | 管理資料流(例如:使能、晶片選擇、寫入)。 | 高電平有效或低電平有效的脈衝 |

| 建立時間 | 資料必須在時鐘邊緣到來前保持穩定的時間長度。 | 邊緣之前的水平距離 |

| 保持時間 | 資料必須在時鐘邊緣後保持穩定的持續時間。 | 邊緣之後的水平距離 |

理解關鍵時序參數 ⚙️

時序參數定義了數位電路正確運作的限制條件。違反這些參數通常會導致不可預測的行為。以下是最重要的指標之定義與影響。

1. 建立時間 ⏳

建立時間是指資料信號在時鐘信號觸發邊緣之前必須保持穩定的最短時間。如果資料在時鐘邊緣附近變動過快,觸發器可能無法正確捕捉該值。這在高速設計中通常是最重要的限制條件,因為它決定了運作的最大頻率。

2. 保持時間 ⏳

保持時間是指資料信號在時鐘信號觸發邊緣之後必須保持穩定的最短時間。與建立時間不同,保持時間通常與時鐘頻率無關。它取決於觸發器的內部延遲以及資料路徑的外部傳播延遲。

3. 傳播延遲 ⏳

這是信號從元件輸入傳播到輸出所需時間。其值會因溫度、電壓和製造公差而異。在時序圖中,這表現為一個信號變化的時間點與另一個信號相應變化之間的延遲。

4. 時鐘週期與頻率 ⏳

時鐘週期是時鐘信號一個完整週期的持續時間。頻率是週期的倒數。週期越短,頻率越高,這雖然能實現更快的處理速度,但也縮小了信號穩定的時間窗口。

常見問題 ❓

工程師經常會遇到導致混淆的特定情境。以下是針對時序分析中最緊迫問題的詳細解答。

問:如果違反建立時間會發生什麼情況? 🛑

當未滿足建立時間要求時,觸發器會進入一種稱為 metastability。在此狀態下,輸出不會立即穩定到有效的邏輯高或低電平。相反,它可能會振盪,或在不可預測的時間內保持在中間電壓水平。這可能導致下游邏輯讀取到錯誤的值,進而引發系統錯誤或當機。在嚴重情況下, metastability 可能會在整個電路中傳播,造成難以調試的功能性失敗。

問:我該如何處理時鐘偏移? 🔄

時鐘偏移發生在時鐘信號到達不同元件的時間不一致時。這可能是由於路徑長度差異或負載差異所導致。為管理偏移,請採取以下措施:

- 路徑平衡: 確保時鐘走線具有相似的長度和寬度。

- 增加緩衝: 使用時鐘緩衝器以均勻驅動多個負載。

- 時序餘量: 設計系統時,應在建立時間和保持時間上留有足夠的餘量,以吸收微小的偏移變化。

問:同步與非同步時序之間的差異是什麼? ⚖️

在同步系統中,所有操作均由單一時鐘信號協調。這些系統的時序圖顯示規律且重複的時鐘邊沿。在非同步系統中,信號在沒有全域時鐘的情況下觸發動作。這些系統的時序圖顯示事件驅動的轉換,通常信號之間的間隔變化較大。非同步設計較難分析,但在特定低功耗應用中可能更具省電優勢。

問:抖動如何影響時序圖? 📉

抖動是指信號在時間上與理想位置的短期偏移。在時序圖中,這表現為時鐘信號的邊沿出現略微提前或延後的情況。過度的抖動會縮小有效資料捕捉窗口,實際上縮小了建立時間與保持時間的餘量,增加時序違規的風險。高速介面需要嚴格控制抖動以維持資料完整性。

問:我能否在沒有時鐘的情況下閱讀時序圖? 🕵️

可以,但需要採用不同的方法。非同步協定如I2C或UART並非總是使用共用的時鐘線。相反,它們依賴預設的傳輸速率或握手信號。在這些圖中,必須觀察脈衝寬度以及轉換之間的時間間隔,以推斷資料速率。例如,在UART中,起始位的持續時間定義了後續資料位的時序。

閱讀與解讀波形 🔍

解讀時序圖需要系統性的方法。隨意掃描線條往往會遺漏細節。遵循以下流程可確保準確分析。

- 識別參考訊號:找出時鐘訊號或主要控制訊號。其他所有時序均以此為參考。

- 檢查有效狀態:判斷訊號是高電平有效還是低電平有效。低電平脈衝可能代表「啟用」,而高電平脈衝則代表「禁用」。這通常在電路圖中以引腳名稱上的圓圈符號表示。

- 分析邊沿對齊:仔細觀察資料邊沿與時鐘邊沿的對齊位置。資料應在時鐘穩定時(例如低電平階段)變更,並在時鐘的活動邊沿期間保持穩定。

- 追蹤依賴關係:追蹤因果關係。若訊號A觸發訊號B,兩者之間應有明確的延遲,對應於傳播延遲。

- 驗證脈衝寬度:確保有效脈衝足夠寬,以便接收元件能檢測到。過窄的脈衝可能被當作雜訊過濾掉。

圖表解讀中的常見錯誤 ❌

即使經驗豐富的工程師若忽略特定細節,也可能誤解圖表。請避免這些常見陷阱。

- 忽略邏輯電平:假設所有訊號均為高電平有效而未經驗證。務必查閱資料手冊或電路圖。

- 忽略傳播延遲:假設訊號瞬間變更。實際元件具有有限的響應時間。

- 誤讀時間尺度:未注意到時間單位(納秒與微秒之分)。在慢速縮放下看似穩定的訊號,在快速縮放下可能顯示雜訊。

- 忽略電源狀態:當裝置進入休眠模式時,時序圖通常會改變。請確保您觀察的是活動時序序列。

精確分析的策略 🛠️

為確保您的時序分析具備穩健性,請採用這些策略。這些方法有助於維持一致性,並降低出錯的機率。

- 使用格線:將游標或標記與圖表上的格線對齊,以精確測量時間間隔。

- 記錄假設:在開始分析前,記下所假設的時鐘頻率與邏輯電平。這可避免後續產生混淆。

- 交叉核對:將時序圖與狀態機邏輯進行比對。每個狀態轉換都應對應一個相應的時序事件。

- 模擬變異:考慮最壞情況。若溫度上升導致延遲增加會如何?若電壓下降導致驅動力減弱又會如何?

- 專注於關鍵路徑:找出邏輯中的最長路徑。此路徑決定了系統的最大時鐘速度。應優先對這些特定路徑進行時序分析。

時序違規的影響 ⚠️

理解時序為何重要至關緊要。當發生時序違規時,電路的物理行為會改變。最常見的後果是資料損壞。寄存器可能在應捕捉‘0’時卻捕捉到‘1’。在通訊協定中,這會導致框架錯誤或封包遺失。在控制系統中,可能導致錯誤的致動器指令,進而可能造成物理損壞或安全隱患。

此外,時序違規可能導致間歇性故障。系統在室溫下可能運作完美,但在升溫時卻會失效。這是因為傳播延遲會隨溫度上升而增加。設計時保留足夠的時序餘量,可應對這些環境變化。

時序圖的最佳實務 📝

製作清晰且準確的時序圖是一項隨著練習而提升的技能。遵循以下指南,以產製他人容易理解的圖表。

- 標示所有項目:每條訊號線都應有明確的名稱。避免使用「訊號1」等泛稱標籤。

- 使用一致的尺度:除非需要針對特定事件進行放大,否則應在整個圖表中維持一致的時間尺度。

- 強調關鍵事件:使用不同顏色或較粗的線條標示設定與保持視窗。

- 包含註解:加入文字註解,以解釋複雜的互動或特定限制。

- 以資料手冊進行核對:務必將圖表參數與官方元件規格進行交叉核對。

進階考量:多時鐘域 🌐

現代系統通常使用多個時鐘域。例如,處理器可能以2 GHz運作,而記憶體控制器則以400 MHz運作。這些系統的時序圖會變得顯著複雜。您必須考慮:

- 跨時鐘取樣: 數據如何從一個頻率轉移到另一個頻率。

- FIFO緩衝區: 如何在異步時鐘之間同步數據流。

- 重置同步: 確保所有時域以協調的方式重置,以避免狀態不一致。

分析這些圖表時,請尋找同步邏輯,例如握手信號或同步鏈。這些組件專門設計用於安全地彌合不同時序域之間的差距。

結論:精確性至關重要 🔑

時序圖不僅僅是圖像;它們是系統正常運作的數學證明。它們定義了可靠性和性能的界限。透過理解核心組件、參數以及潛在的陷阱,您就能設計出在現實條件下正確運作的系統。對建立時間、保持時間和傳播延遲的關注,將功能性原型與可投入生產的產品區分開來。持續練習閱讀和創建這些圖表,將提升您的技術直覺,改善您的工程成果。

請記住,每一個邊沿都講述著資訊流動的故事。尊重資訊傳播所需的时间,您的設計將經得起時間的考驗。