En la arquitectura compleja de los sistemas digitales, comprender el momento preciso en que una señal cambia de estado es fundamental. Los diagramas de tiempo proporcionan una representación visual de cómo evolucionan las señales con el tiempo. Son herramientas esenciales para ingenieros, desarrolladores y diseñadores que necesitan verificar que los componentes interactúen correctamente. Sin estas ayudas visuales, depurar la comunicación asíncrona o verificar dominios de reloj se convierte en un juego de adivinanzas. Esta guía explora la mecánica, las ventajas y las aplicaciones de los diagramas de tiempo en el diseño de sistemas.

¿Qué es un diagrama de tiempo? ⚙️

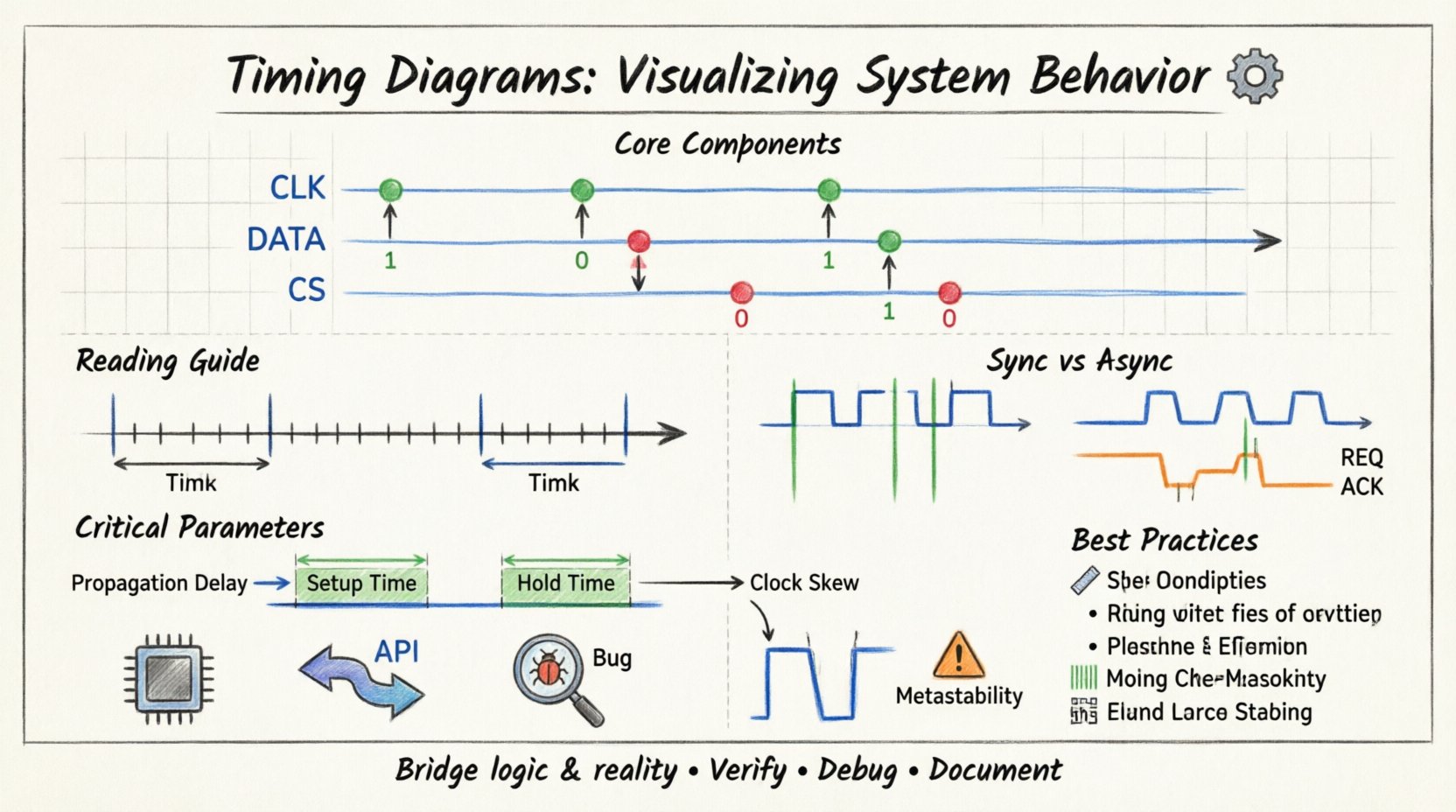

Un diagrama de tiempo es una gráfica que muestra el comportamiento de las señales durante un período. Representa el estado lógico de las señales en relación con una línea de tiempo. A diferencia de los esquemas de circuitos, que muestran conexiones físicas, los diagramas de tiempo se centran en la relación temporal entre eventos. Responden preguntas como: ¿La señal A cambia antes que la señal B? ¿Es lo suficientemente ancho el pulso del reloj? ¿Cuánto tiempo tarda en estabilizarse los datos?

Estos diagramas son fundamentales en:

- Verificación de protocolos de hardware

- Documentación de interacciones lógicas del software

- Depuración de condiciones de carrera

- Validación de la alineación entre reloj y datos

Componentes principales de un diagrama de tiempo 🧩

Para interpretar un diagrama de tiempo de forma efectiva, se debe comprender sus bloques de construcción. Cada diagrama consta de elementos específicos que transmiten información sobre el funcionamiento del sistema.

1. El eje del tiempo 📏

El eje horizontal representa el tiempo. Suele fluir de izquierda a derecha. La escala puede ser absoluta (nanosegundos, microsegundos) o relativa (ciclos de reloj). En los sistemas síncronos, el tiempo a menudo se divide en pasos discretos que corresponden a los bordes del reloj.

2. Líneas de señal 📡

Cada línea representa una señal específica, un cable o un bus de datos. Estas líneas se etiquetan con nombres comoCLK, DATA, CS (Selección de chip), oRST (Reinicio). La posición de la línea en sentido vertical separa las diferentes señales para evitar confusiones.

3. Niveles lógicos 🟢🔴

Las señales suelen existir en estados discretos. En la lógica digital, estos son alto (lógica 1) y bajo (lógica 0). Los diagramas de tiempo muestran las transiciones entre estos estados. Una transición de bajo a alto es un borde ascendente. Una transición de alto a bajo es un borde descendente.

4. Eventos y transiciones 🔄

Los eventos son momentos específicos en los que una señal cambia de estado. A menudo se marcan con líneas verticales o flechas. Los eventos importantes incluyen bordes del reloj, bloqueos de datos y señales de reconocimiento. La separación entre estos eventos indica la duración.

Lectura efectiva de diagramas de tiempo 👁️

Leer estos diagramas requiere un enfoque sistemático. Interpretar incorrectamente la secuencia de eventos puede provocar fallos en el diseño. Siga estos principios para asegurar la precisión.

- De izquierda a derecha: Siempre lea la cronología desde el principio (izquierda) hasta el final (derecha). Esto representa el flujo cronológico de las operaciones.

- Alineación vertical: Los eventos alineados verticalmente ocurren simultáneamente. Si dos señales cambian en la misma línea vertical exacta, son concurrentes.

- Duración: La longitud horizontal del estado de una señal indica cuánto tiempo permanece en ese estado. Un pulso ancho significa una duración más larga.

- Dependencias: Busque causas y efectos. El cambio de una señal suele desencadenar otro. El diagrama muestra la latencia entre estos desencadenadores.

Sistemas síncronos frente a asíncronos 🔄

Los diagramas de temporización difieren significativamente según si el sistema es síncrono o asíncrono. Comprender esta distinción es vital para un análisis preciso.

Sistemas síncronos ⏰

Estos sistemas dependen de una señal de reloj global. Todos los cambios de estado ocurren en bordes específicos del reloj (de subida o bajada). El diagrama mostrará un patrón de reloj regular. Los datos se muestrean solo cuando el reloj lo permite. Esto hace que el tiempo sea predecible, pero introduce restricciones como los tiempos de preparación y retención.

Sistemas asíncronos 🕰️

Estos sistemas no dependen de un reloj global. Los cambios de estado ocurren cuando cambian las señales de entrada. Los diagramas de temporización aquí tienen un aspecto menos regular. Se centran en protocolos de intercambio de señales. Una señal debe subir, luego la otra, y luego volver a bajar. Esto requiere un análisis cuidadoso de los retrasos para evitar condiciones de carrera.

Parámetros críticos en el análisis de temporización ⚙️

Más allá de simplemente dibujar líneas, los ingenieros analizan parámetros específicos para garantizar la fiabilidad. Estos parámetros definen la ventana en la que un sistema funciona correctamente.

- Retardo de propagación: El tiempo que tarda una señal en viajar desde la entrada hasta la salida a través de un componente. Este retardo se acumula a través de las puertas lógicas.

- Tiempo de preparación: El tiempo mínimo antes de un borde del reloj en que los datos deben estar estables. Si los datos cambian demasiado tarde, el flip-flop no puede capturarlos correctamente.

- Tiempo de retención: El tiempo mínimo después de un borde del reloj en que los datos deben permanecer estables. Si los datos cambian demasiado pronto, se pierde el valor actual.

- Desfase del reloj: La diferencia en el tiempo de llegada de la señal de reloj en diferentes componentes. Un alto desfase puede causar violaciones de tiempo de preparación o retención.

- Metastabilidad: Un estado en el que la salida de un flip-flop no es ni alta ni baja. Esto ocurre cuando se violan los tiempos de preparación o retención. Los diagramas de temporización ayudan a visualizar el riesgo de metastabilidad.

Aplicación en hardware y software 🔌

Los diagramas de temporización no se limitan al hardware. También se utilizan ampliamente en la arquitectura de software y en el diseño de protocolos.

Diseño de hardware

En hardware, estos diagramas validan los protocolos de bus. Por ejemplo, verificar que el bus de direcciones esté estable antes de que se active el pulso de lectura. Garantizan que los tiempos de acceso a memoria coincidan con la velocidad del reloj del procesador. También se utilizan para analizar los picos de consumo de energía durante las transiciones de señal.

Software y protocolos

En software, los diagramas de tiempo representan llamadas a la API o intercambios de mensajes. Muestran la secuencia de solicitudes y respuestas entre servicios. Esto ayuda a identificar problemas de latencia en sistemas distribuidos. Clarifican el orden de las operaciones en entornos multi-hilo.

Errores y trampas comunes 🛑

Crear o leer diagramas de tiempo puede conducir a errores si no se hace con cuidado. Ser consciente de los errores comunes ayuda a mejorar la precisión.

- Ignorar el nivel bajo activo:Muchas señales utilizan lógica de nivel bajo activo (invertida). Una línea que baja a bajo podría significar que la señal está activa. Siempre revise la leyenda o la etiqueta.

- Asumir transiciones instantáneas:Las señales reales tienen tiempos de subida y bajada. Los diagramas ideales muestran líneas verticales, pero las señales físicas tienen pendientes. Esta pendiente afecta la integridad de la señal.

- Descuidar los picos:Pulsos cortos que no cumplen con los requisitos mínimos de ancho pueden causar activaciones falsas. A menudo se les llama picos.

- Interpretar incorrectamente el estado de alta impedancia:Los estados de alta impedancia significan que una señal está desconectada. En los diagramas, esto se ve como una línea punteada o un símbolo específico. Ignorarlo puede provocar errores de contención de bus.

- Alineación incorrecta del reloj:Suponer que todos los relojes están alineados en fase cuando no lo están. El desfase puede causar que los datos se muestreen incorrectamente.

Comparación de tipos de diagramas 📊

Distintos contextos requieren diferentes métodos de visualización. Aunque los diagramas de tiempo son potentes, no son la única herramienta.

| Tipo de diagrama | Enfoque principal | Mejor utilizado para |

|---|---|---|

| Diagrama de tiempo | Tiempo y estados de señal | Verificación de relaciones entre reloj/datos |

| Diagrama de estado | Estados del sistema | Definición del flujo lógico y condiciones |

| Diagrama de secuencia | Orden de mensajes | Interacciones de software y llamadas a la API |

| Esquema de circuito | Conexiones físicas | Instalación de cables y disposición de componentes |

| Visor de Forma de Onda | Señales en Tiempo Real | Depuración del comportamiento real del hardware |

Mejores Prácticas para la Documentación 📝

Para que los diagramas de temporización sean útiles para los equipos y futuras referencias, siga estas mejores prácticas. Una documentación clara reduce la ambigüedad y acelera la depuración.

- Etiquete todo: Cada línea de señal debe tener un nombre claro. Evite etiquetas genéricas como Sig1.

- Incluya unidades: Especifique las unidades de tiempo en el eje. ¿Estamos viendo milisegundos o ciclos de reloj?

- Marque los puntos críticos: Destaque explícitamente las ventanas de configuración y retención. Use sombreado o colores distintos para marcar las ventanas críticas de temporización.

- Manténgalo organizado: Agrupe las señales relacionadas juntas. Por ejemplo, todas las señales de control en la parte superior, las señales de datos en la parte inferior.

- Documente las suposiciones: Anote cualquier suposición realizada durante la creación. Por ejemplo, suponga un retardo de propagación cero o condiciones de carga específicas.

- Use una notación consistente: Adhiera a símbolos estándar para bordes ascendentes, bordes descendentes y estados de alta impedancia.

Guía Paso a Paso para Crear un Diagrama 🛠️

Crear un diagrama de temporización desde cero requiere un enfoque estructurado. Siga estos pasos para asegurar la completitud.

- Identifique las señales: Liste todas las entradas y salidas involucradas en la interacción.

- Determine la secuencia: Defina el orden de los eventos. ¿Qué desencadena el proceso?

- Establezca la escala de tiempo: Decida sobre el grado de detalle del eje de tiempo.

- Dibuje el reloj: Si es síncrono, dibuje primero la señal de reloj. Esta fija el resto del diagrama.

- Agregue datos: Represente las señales de datos respecto a los bordes del reloj.

- Verifique las restricciones:Verifique los tiempos de establecimiento y retención frente a las señales dibujadas.

- Revisión:Recorra la línea de tiempo para asegurarse de que no existan brechas lógicas.

El papel del tiempo en la depuración 🐞

Cuando un sistema falla, los diagramas de tiempo suelen ser el primer lugar al que los ingenieros recurren. Ayudan a determinar si el problema es lógico o temporal. Si la lógica es correcta pero el tiempo está mal, el sistema falla de forma intermitente. Esto suele ser más difícil de reproducir que un error lógico grave.

Los escenarios de depuración incluyen:

- Corrupción de datos:Señales que cambian mientras se leen.

- Interrupciones perdidas:Una señal de interrupción demasiado corta para ser detectada.

- Contención de bus:Dos dispositivos que conducen el bus al mismo tiempo.

- Cruce de dominios de reloj:Señales que se mueven entre frecuencias de reloj diferentes sin una sincronización adecuada.

Comprender el ancho de datos y la alineación 📐

Los diagramas de tiempo también visualizan el ancho de datos. Los buses paralelos requieren múltiples líneas. Cada línea debe cambiar de forma sincronizada. La desalineación puede causar errores de datos. El diagrama muestra cómo se alinean los bits dentro de un ciclo de reloj. En la comunicación serial, el diagrama de tiempo muestra la secuencia de bits. Destaca el período de bit y el punto de muestreo.

Temas avanzados: Jitter y ruido 📉

Las señales del mundo real no son perfectas. El jitter es la desviación del borde del reloj respecto a su posición ideal. El ruido es una fluctuación aleatoria en el nivel de señal. Los diagramas de tiempo pueden representar el jitter mostrando una banda ancha alrededor del borde en lugar de una línea aguda. Esto indica incertidumbre. Los diseñadores deben asegurarse de que el sistema tolera esta incertidumbre. El margen entre la banda de jitter y la ventana de establecimiento/retención es el margen de seguridad.

Integración con conjuntos de pruebas 🧪

Los diagramas de tiempo no son solo para el diseño. Se utilizan para generar casos de prueba. Los conjuntos de pruebas automatizados pueden verificar si el comportamiento real del sistema coincide con el diagrama. Si el tiempo medido se desvía más allá de la tolerancia, la prueba falla. Esto garantiza que el hardware o el software cumpla con las especificaciones durante todo su ciclo de vida.

Conclusión sobre la visualización del sistema 🎯

Los diagramas de tiempo siguen siendo una piedra angular de la ingeniería de sistemas. Cerraran la brecha entre la lógica abstracta y la realidad física. Al visualizar el flujo del tiempo y las señales, los ingenieros pueden predecir fallas antes de que ocurran. Facilitan la comunicación entre los equipos de hardware y software. Un diagrama bien dibujado transmite más información que páginas de texto. A medida que los sistemas se vuelven más rápidos y complejos, la necesidad de un análisis de tiempo preciso aumenta. El dominio de estos diagramas garantiza diseños robustos y confiables.

Recuerde priorizar la claridad y la precisión. Evite suposiciones. Verifique cada transición. Con práctica, leer y crear estos diagramas se convierte en una parte intuitiva del proceso de diseño. Son el mapa que guía al viajero a través del paisaje de la lógica digital.