Los diagramas de tiempo son herramientas esenciales para visualizar el comportamiento de las señales digitales durante un período específico. En el campo de la electrónica digital y la ingeniería de computadoras, comprender cómo interactúan las señales es fundamental para la estabilidad y el rendimiento del sistema. Esta guía ofrece un examen detallado de la notación de diagramas de tiempo, asegurando que puedas leer, crear e interpretar formas de onda con precisión. Exploraremos los niveles de señal, los ejes temporales, las transiciones y los parámetros críticos de tiempo sin depender de herramientas de software específicas.

🔍 Comprendiendo los componentes principales de los diagramas de tiempo

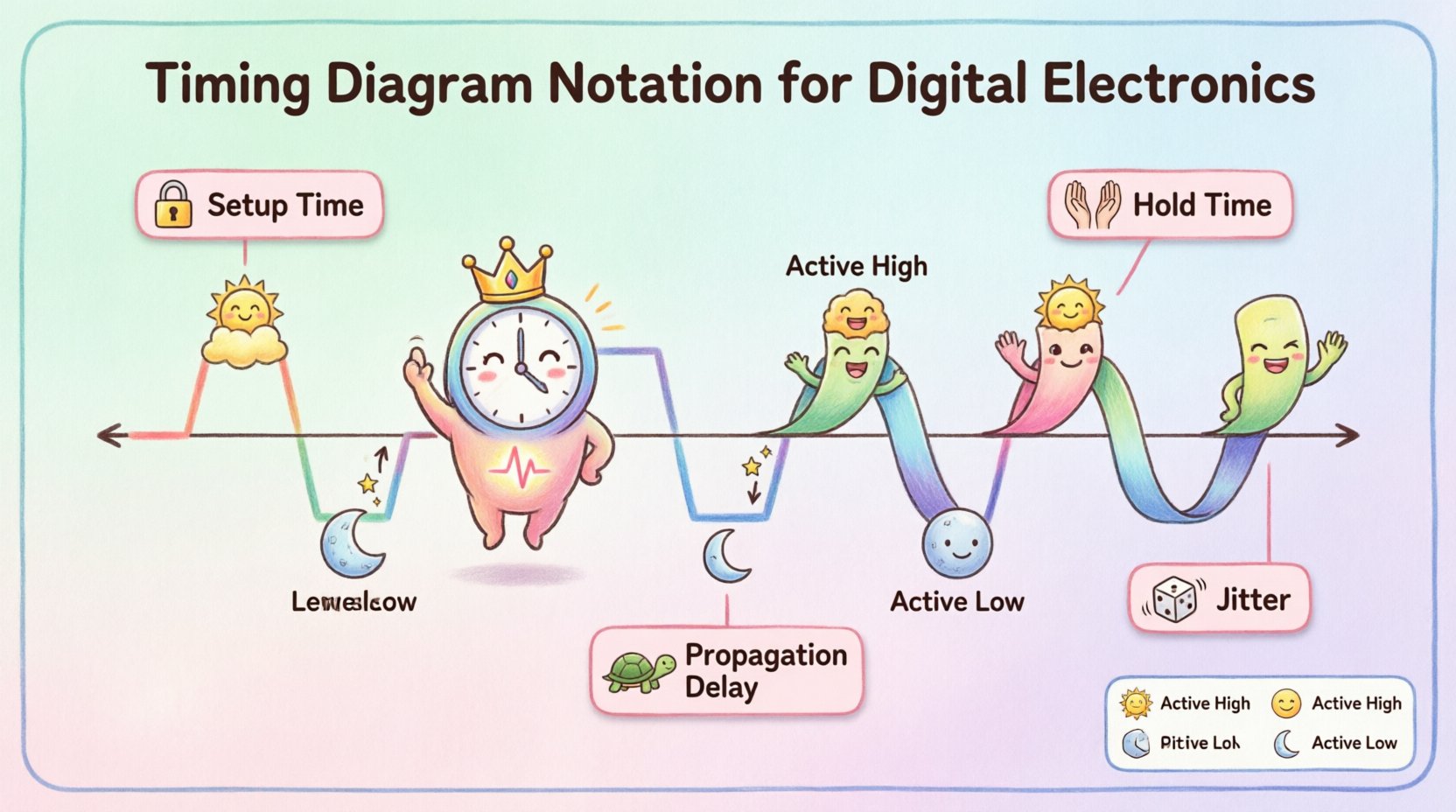

En su base, un diagrama de tiempo representa el estado lógico de las señales respecto al tiempo. Actúa como una plantilla para cómo los datos se mueven a través de un sistema. Para interpretar correctamente estos diagramas, uno debe comprender los ejes fundamentales y las representaciones de señal.

- Eje horizontal:Representa el tiempo. Este eje fluye de izquierda a derecha, indicando la secuencia de eventos.

- Eje vertical:Representa el estado lógico o el nivel de voltaje de una línea de señal específica.

- Líneas de señal:Cada línea horizontal corresponde a un cable específico, red o variable lógica dentro del circuito.

- Niveles lógicos:Las señales generalmente conmutan entre dos estados, comúnmente denominados Alto y Bajo.

Al analizar un diagrama de tiempo, el observador busca la relación entre los cambios en una señal y los cambios en otra. Esta relación determina si los datos se capturan correctamente o si ocurren errores. Una notación adecuada garantiza que estas relaciones sean claras y sin ambigüedades para los ingenieros que revisan el diseño.

⚡ Niveles y estados lógicos de señal

Los sistemas digitales operan según principios binarios, pero su representación física varía. La notación debe definir claramente qué constituye un uno lógico y un cero lógico. Interpretar incorrectamente estos niveles puede provocar fallas de diseño catastróficas.

Alto activo frente a Bajo activo

Las señales pueden estar activas cuando están en alto o cuando están en bajo. Este concepto es vital para las señales de control como reinicios o habilitaciones.

- Alto activo:La señal realiza su función cuando el voltaje está alto (lógica 1). Este es el estándar para la mayoría de las líneas de datos.

- Bajo activo:La señal realiza su función cuando el voltaje está bajo (lógica 0). Las señales de control suelen usar esta notación para reducir el ruido o cumplir con requisitos específicos de hardware.

- Indicadores de notación:Las señales activas en bajo suelen marcarse con una barra sobre el nombre o un círculo al final de la línea en los diagramas esquemáticos.

Niveles de voltaje lógico

Aunque los valores lógicos 0 y 1 son abstractos, el diagrama de tiempo representa voltajes físicos. La notación debería especificar idealmente los umbrales de voltaje.

- Lógico alto:Generalmente representado por un voltaje por encima de un umbral específico (por ejemplo, 3,3 V o 5 V).

- Lógico bajo:Generalmente representado por un voltaje por debajo de un umbral específico (por ejemplo, 0 V).

- Zona no definida: El área entre los umbrales alto y bajo donde el estado de la señal es indeterminado. Los diagramas deben evitar permanecer en esta zona.

⏱️ Eje del tiempo y sincronización

La representación del tiempo es el segundo aspecto más crítico de los diagramas de temporización. A diferencia del voltaje, el tiempo es continuo, pero las señales digitales cambian en momentos discretos. La notación debe manejar tanto eventos síncronos como asíncronos.

Señales de reloj

La mayoría de los sistemas digitales dependen de un reloj para sincronizar las operaciones. La señal de reloj es el latido del sistema.

- Período: El tiempo que tarda en completarse un ciclo completo del reloj.

- Frecuencia: El número de ciclos por segundo, generalmente medido en hercios.

- Ciclo de trabajo: El porcentaje del período durante el cual la señal está en alto.

- Notación: Las señales de reloj suelen dibujarse con un patrón de onda cuadrada.

Tiempo relativo frente a tiempo absoluto

Los diagramas de temporización pueden usar tiempo relativo o tiempo absoluto.

- Tiempo relativo: Las mediciones se toman desde un punto de referencia, como una arista específica del reloj. Esto es común en el análisis de tiempos de preparación y retención.

- Tiempo absoluto: Se asignan marcas de tiempo específicas a los eventos, útil para depurar protocolos de comunicación durante largos periodos.

Escala de tiempo

Elegir la escala de tiempo correcta es crucial para la claridad.

- Nanosegundos: Utilizado para lógica de alta velocidad donde las señales cambian rápidamente.

- Microsegundos: Utilizado para interacciones más lentas con periféricos.

- Milisegundos: Utilizado para la gestión de energía a nivel de sistema o eventos de baja frecuencia.

🔄 Transiciones de borde y notación

El momento en que una señal cambia de estado es tan importante como el estado mismo. La notación debe representar claramente cómo y cuándo ocurren estas transiciones.

Bordes ascendentes y descendentes

Las aristas representan la transición entre niveles lógicos.

- Arista de subida: La transición de Bajo a Alto. A menudo marcada con una línea vertical o una flecha apuntando hacia arriba.

- Arista de bajada: La transición de Alto a Bajo. A menudo marcada con una línea vertical o una flecha apuntando hacia abajo.

- Pendiente: En diagramas ideales, las aristas son verticales. En diagramas del mundo real, las aristas tienen una pendiente que representa el tiempo de subida o el tiempo de bajada.

Retardos de transición

Las señales no cambian instantáneamente. La notación debe tener en cuenta los retardos de propagación.

- Retardo de propagación: El tiempo que tarda un cambio en la entrada en producir un cambio en la salida.

- Notación: A menudo indicado por un espacio entre la transición de entrada y la transición de salida.

Glitches y peligros

Pueden ocurrir transiciones no deseadas debido a los retardos del circuito. A menudo se muestran como picos breves.

- Glitch: Un pulso corto que no debería estar allí. La notación puede usar líneas punteadas o colores distintos.

- Peligro: Una posibilidad de salida incorrecta debido a diferencias de tiempo.

📏 Parámetros críticos de tiempo

Ciertos parámetros definen la fiabilidad de una interfaz digital. Son las métricas que los ingenieros miden para garantizar la integridad de los datos.

| Parámetro | Descripción | Unidad |

|---|---|---|

| Tiempo de establecimiento | El tiempo en que los datos deben estar estables antes del borde del reloj. | Tiempo (ns) |

| Tiempo de retención | El tiempo en que los datos deben permanecer estables después del borde del reloj. | Tiempo (ns) |

| Retardo de propagación | Tiempo desde el cambio de entrada hasta el cambio de salida. | Tiempo (ns) |

| Reloj a Q | Tiempo desde el borde del reloj hasta el cambio de salida. | Tiempo (ns) |

| Jitter | Variación en el momento de un borde de señal. | Tiempo (ps/ns) |

Tiempo de configuración y tiempo de retención

Estas son las restricciones más críticas para los sistemas síncronos.

- Violación del tiempo de configuración: Si los datos cambian demasiado cerca del borde del reloj, el sistema podría no capturar el valor correcto.

- Violación del tiempo de retención: Si los datos cambian demasiado pronto después del borde del reloj, el sistema podría perder el valor.

- Notación: Normalmente se muestran como ventanas de tiempo alrededor del borde del reloj en las que la línea de datos no debe cambiar.

Retardo de propagación

Este retardo afecta la frecuencia máxima del sistema.

- Alto a Bajo:Tiempo que tarda una señal en pasar de Alto a Bajo.

- Bajo a Alto:Tiempo que tarda una señal en pasar de Bajo a Alto.

- Notación: A menudo se muestra como un espacio horizontal entre las formas de onda de entrada y salida.

🛠️ Señales de control y estados activos

Las señales de control gestionan el flujo de datos. Su notación debe indicar claramente cuándo están activas.

| Tipo de señal | Estado activo | Ejemplo de notación |

|---|---|---|

| Reiniciar | Activo bajo | Reset# o Reset_bar |

| Habilitar | Activo alto | Habilitar |

| Interrupción | Activo alto o bajo | IRQ o IRQ_bar |

| Selección de chip | Activo bajo | CS# |

Señales de reinicio

Las señales de reinicio inicializan el sistema. Pueden ser asíncronas o síncronas.

- Reinicio asíncrono:Toma efecto de inmediato, independientemente del reloj. La notación muestra que la línea de reinicio se activa en cualquier momento.

- Reinicio síncrono:Toma efecto solo en un borde del reloj. La notación muestra que la línea de reinicio está activa antes del borde del reloj.

Señales de habilitación

Las señales de habilitación permiten o bloquean operaciones.

- Habilitación alta:La operación ocurre cuando la señal está alta.

- Habilitación baja:La operación ocurre cuando la señal está baja.

📖 Lectura y análisis de formas de onda

Leer un diagrama de tiempos requiere un enfoque sistemático. Los ingenieros deben seguir pasos específicos para evitar malentendidos.

Análisis paso a paso

- Identifique el reloj:Localice la referencia principal de tiempo. Todos los eventos síncronos se relacionan con esta.

- Rastree el flujo de datos:Siga las líneas de datos desde la fuente hasta el destino.

- Verifique las ventanas de tiempo:Verifique los tiempos de preparación y retención frente al borde del reloj.

- Busque anomalías:Identifique interferencias, picos o transiciones inesperadas.

- Verifique los niveles lógicos:Asegúrese de que los estados activos coincidan con las especificaciones del componente.

Malentendidos comunes

- Asumiendo un cambio instantáneo:Las señales reales tienen tiempos de subida y bajada. Asumir bordes verticales puede ocultar violaciones de tiempo.

- Ignorando señales asíncronas:Las señales de control que no están relojadas pueden aparecer en cualquier momento y deben verificarse de forma independiente.

- Interpretación incorrecta de los estados activos:Confundir el activo alto con el activo bajo es una causa común de errores de diseño.

🚀 Consideraciones avanzadas de tiempo

A medida que los sistemas se vuelven más rápidos, el análisis de tiempo se vuelve más complejo. La notación avanzada aborda estos desafíos.

Metastabilidad

Cuando una señal cambia durante la ventana de preparación o retención, la salida puede entrar en un estado metastable.

- Definición:La señal se establece en un nivel de voltaje intermedio.

- Notación:A menudo se representa como un signo de interrogación o una región sombreada entre Alto y Bajo.

- Resolución:La señal finalmente se resuelve en Alto o Bajo, pero el tiempo es impredecible.

Desequilibrio de sincronización

Diferentes caminos pueden tardar cantidades diferentes de tiempo en alcanzar un destino.

- Desequilibrio de reloj:La señal de reloj llega a diferentes componentes en tiempos diferentes.

- Desequilibrio de datos:Las señales de datos llegan a destinos diferentes en tiempos diferentes.

- Notación:Mostrado como un desplazamiento horizontal entre los tiempos de llegada esperados y reales.

Jitter

El jitter es la desviación del borde de la señal respecto a su posición ideal.

- Jitter ciclo a ciclo:Variación entre un ciclo de reloj y el siguiente.

- Jitter de período:Variación en la duración total del ciclo de reloj.

- Notación:A menudo mostrado como una zona sombreada alrededor de la posición ideal del borde.

📝 Mejores prácticas para la documentación

Crear diagramas de tiempo claros garantiza que otros puedan entender tu diseño. Alinear con las mejores prácticas reduce la ambigüedad.

- Nombres consistentes:Utiliza nombres claros y únicos para todas las señales. Evita nombres genéricos como Señal1 o Señal2.

- Símbolos estándar:Utiliza notación estándar para bordes, niveles y retrasos para garantizar la compatibilidad con la industria.

- Escala de tiempo clara:Etiqueta el eje del tiempo explícitamente con unidades (ns, µs, ms).

- Agrupa señales relacionadas:Agrupa las señales que pertenecen al mismo protocolo o subsistema juntas.

- Destaca los tiempos críticos:Utiliza líneas en negrita o colores para resaltar las ventanas de setup y hold.

- Proporciona leyendas:Incluye una clave para cualquier símbolo personalizado o abreviatura utilizada en el diagrama.

🔚 Resumen de los puntos clave

La notación de diagramas de tiempo es una habilidad fundamental para cualquier persona que trabaje en diseño digital. Al comprender los componentes esenciales, los niveles de señal y los parámetros de tiempo, los ingenieros pueden garantizar un rendimiento robusto del sistema. Una notación adecuada elimina la ambigüedad y previene errores de diseño costosos. Recuerda centrarte en los tiempos de setup y hold, definir claramente los estados activos y tener en cuenta las características reales de las señales, como el retardo de propagación y el jitter. Seguir estas pautas dará como resultado una documentación clara y eficaz.

Cuando crees o revises estos diagramas, verifica siempre los niveles lógicos frente a las especificaciones del hardware. Asegúrate de que el eje del tiempo refleje la frecuencia de operación real del sistema. Por último, mantén la consistencia en tu estilo de notación en toda la documentación para facilitar la colaboración. Con práctica, interpretar y crear estos diagramas se convertirá en una parte natural del flujo de trabajo de diseño.

Notas finales sobre la implementación

Aunque esta guía cubre los aspectos teóricos y notacionales, la implementación práctica requiere atención a la capa física. La integridad de la señal, los márgenes de ruido y la entrega de energía influyen todos en el comportamiento de tiempo. Siempre verifica los diagramas de tiempo con las hojas de datos y los resultados de simulación para validar el diseño. El aprendizaje continuo y el cumplimiento de las normas de la industria mantendrán tus diseños confiables y eficientes.