En el mundo de la electrónica digital y el diseño de sistemas, el tiempo no es solo una dimensión; es un parámetro crítico que determina si un circuito funciona correctamente o falla catastróficamente.Diagramas de tiempoSirven como el lenguaje visual que los ingenieros utilizan para comunicar cómo se comportan las señales con el paso del tiempo. Ya sea que estés diseñando una interfaz de microcontrolador, depurando un bus de memoria o analizando la transmisión de datos de alta velocidad, comprender estos diagramas es imprescindible.

Esta guía explora la mecánica de los diagramas de tiempo, descomponiendo los comportamientos complejos de las señales en componentes comprensibles. Avanzaremos desde definiciones fundamentales hasta técnicas avanzadas de análisis, asegurándonos de que cuentes con las herramientas necesarias para interpretar las formas de onda con precisión.

🔍 ¿Qué es un Diagrama de Tiempo?

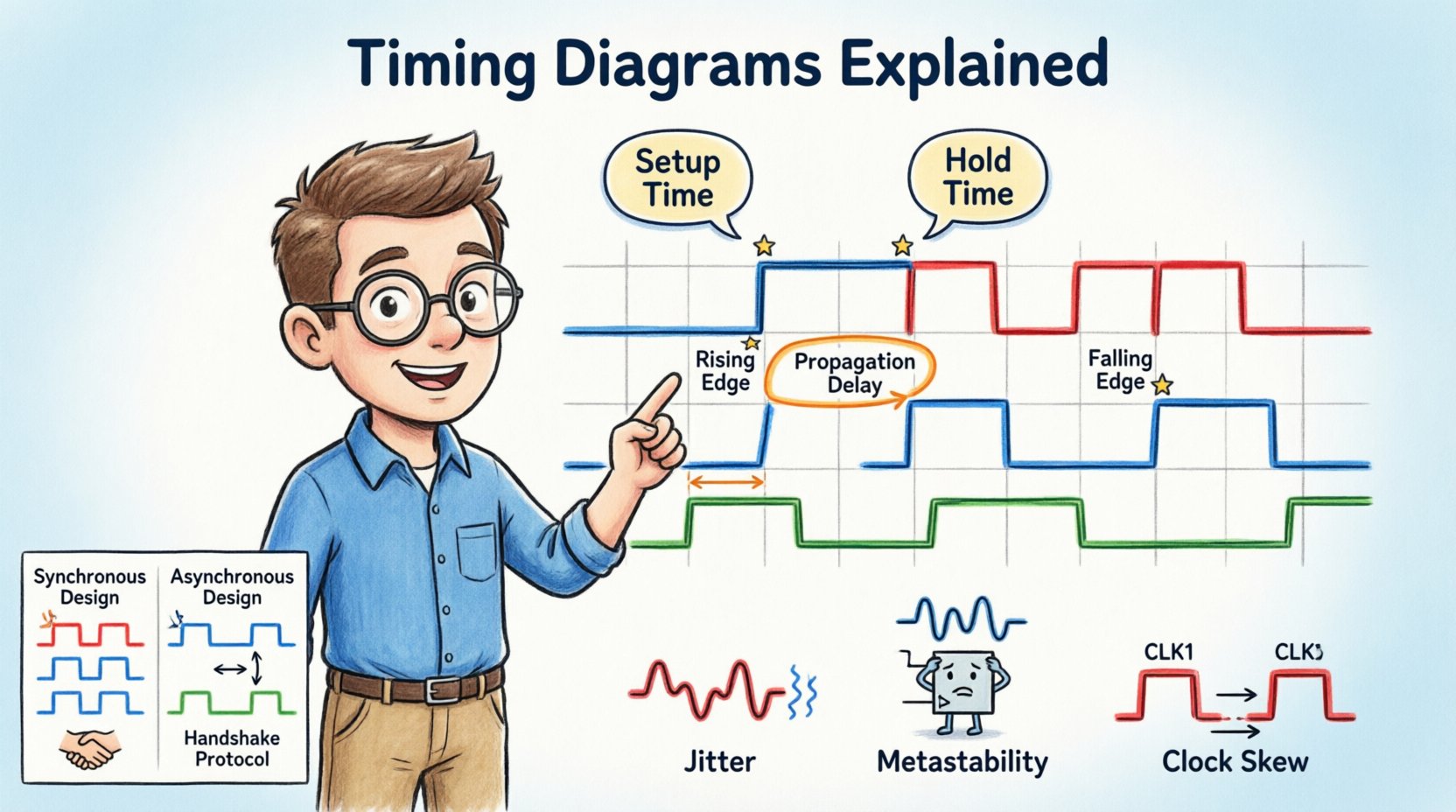

Un diagrama de tiempo es una representación gráfica de la secuencia de cambios de señal en un sistema digital. A diferencia de un esquema, que muestra cómo están conectados los componentes, un diagrama de tiempo ilustracuándocambian de estado esas conexiones. Representa la actividad de las señales a lo largo de un eje horizontal de tiempo, permitiendo a los diseñadores verificar que los datos estén estables antes de un borde de reloj o que las señales de control se activen en el momento adecuado.

Estos diagramas son esenciales para:

- Verificar las interacciones entre hardware y software.

- Depurar protocolos de comunicación.

- Asegurar que se cumplan los requisitos de tiempo de preparación y retención.

- Documentar el comportamiento del sistema para mantenimiento futuro.

Sin una comprensión clara del tiempo, incluso un circuito lógicamente correcto puede fallar debido a carreras de señales o metastabilidad.

🛠️ Componentes Fundamentales de un Diagrama de Tiempo

Para leer un diagrama de tiempo de forma efectiva, debes identificar sus bloques constructivos fundamentales. Cada elemento lleva información específica sobre el estado y el flujo del sistema digital.

1. El Eje del Tiempo

La línea horizontal representa la progresión del tiempo. Normalmente fluye de izquierda a derecha. En documentos técnicos detallados, este eje puede marcarse con unidades de tiempo específicas (nanosegundos, picosegundos) o ciclos de reloj.

2. Líneas de Señal

Las líneas verticales representan señales individuales, como líneas de reloj, buses de datos o líneas de control (como selección de chip o lectura/escritura). Cada línea corresponde a un nodo específico en el circuito.

3. Niveles Lógicos

Las señales normalmente existen en uno de dos estados:

- Alto (Lógica 1 / VCC):A menudo representado por una línea en la parte superior de la traza de la señal.

- Bajo (Lógica 0 / GND):Representado por una línea en la parte inferior de la traza de la señal.

Algunos sistemas utilizanLógica Activa Bajalógica, donde la señal realiza su función cuando el voltaje es bajo. En los diagramas, esto a menudo se indica mediante un círculo en el nombre de la señal o una notación específica.

4. Transiciones

Las transiciones son los momentos en los que una señal cambia de alto a bajo o de bajo a alto.

- Borde de subida:Transición de bajo a alto. Fundamental para activar eventos.

- Borde de bajada:Transición de alto a bajo. Utilizado para secuencias de control específicas.

- Activado por borde:La señal solo se evalúa durante la transición, no en el estado estable.

⚙️ Parámetros clave de temporización

Un diseño digital preciso depende de cuantificar la relación entre las señales. Los siguientes parámetros son la base del análisis de temporización.

1. Retardo de propagación (tpd)

Este es el tiempo que tarda una señal en viajar desde la entrada de una puerta lógica o componente hasta su salida. Ninguna señal cambia instantáneamente; las limitaciones físicas causan un retardo.

- Significación:Si el retardo es demasiado largo, la lógica posterior podría recibir los datos demasiado tarde, causando errores.

- Medición:Medido desde el punto de voltaje del 50% de la transición de entrada hasta el punto de voltaje del 50% de la transición de salida.

2. Tiempo de preparación (tsu)

El tiempo de preparación es la duración mínima durante la cual las señales de datos deben permanecer establesantesde que llegue un borde de reloj.

- Escenario:Si un flip-flop necesita que los datos estén listos 5 nanosegundos antes de que el reloj se active, ese es el tiempo de preparación.

- Violación:Si los datos cambian demasiado cerca del borde del reloj, el sistema no puede capturar el valor correctamente.

3. Tiempo de retención (th)

El tiempo de retención es la duración mínima durante la cual las señales de datos deben permanecer establesdespuésllega una transición de reloj.

- Escenario:El flip-flop necesita «ver» los datos durante un breve período después del disparo para capturarlos de forma segura.

- Violación:Si los datos cambian inmediatamente después de la transición del reloj, la entrada podría no capturarse correctamente.

4. Atraso de reloj

El atraso de reloj ocurre cuando la señal de reloj llega a diferentes componentes en tiempos distintos. Esto suele deberse a diferencias en la longitud de las trazas en una placa de circuito impreso.

- Atraso positivo:El reloj llega más tarde en el destino.

- Atraso negativo:El reloj llega antes en el destino.

5. Jitter

El jitter es la variación a corto plazo de los instantes significativos de una señal respecto a sus posiciones ideales en el tiempo. Añade incertidumbre al análisis de temporización.

📊 Comparación: Diseño síncrono frente a diseño asíncrono

Comprender la diferencia entre estas dos filosofías de diseño es fundamental para interpretar correctamente los diagramas de temporización.

| Característica | Temporización síncrona | Temporización asíncrona |

|---|---|---|

| Señal de control | Utiliza un reloj global | Utiliza señales de intercambio de mensajes |

| Previsibilidad | Altamente predecible | Variable según la carga |

| Complejidad | Requiere distribución de reloj | Requiere lógica de intercambio de mensajes compleja |

| Consumo de energía | Puede ser alto (conmutación del reloj) | A menudo más bajo (controlado por actividad) |

| Diagrama de temporización | Alineado con los bordes del reloj | Dependiente de la finalización del estado anterior |

🧐 Cómo leer y analizar diagramas de temporización

Analizar una onda requiere un enfoque sistemático. Siga estos pasos para asegurarse de no omitir detalles críticos.

Paso 1: Identificar el reloj

Localice la señal principal de reloj. Esta suele ser la referencia para todos los demás tiempos. En sistemas síncronos, cada transición de datos debería referirse idealmente a este borde del reloj.

Paso 2: Verificar la presencia de picos

Busque pulsos cortos e intencionales (picos) en las líneas de señal. Estos pueden causar activaciones falsas en puertas lógicas. En un diagrama limpio, las transiciones deben ser limpias, aunque la captura en el mundo real a menudo muestra ruido.

Paso 3: Verificar las ventanas de setup y hold

Dibuje líneas verticales imaginarias que representen las ventanas de setup y hold alrededor del borde activo del reloj. Asegúrese de que la señal de datos sea estable dentro de estas zonas.

Paso 4: Verificar las señales de control

Asegúrese de que las señales de control como Chip Select (CS) o Enable (EN) estén activas durante toda la duración de la transferencia de datos. Si una señal de control se desactiva mientras aún se envían datos, se produce corrupción.

Paso 5: Medir intervalos

Calcule el tiempo entre eventos específicos. Por ejemplo, mida la latencia desde la señal de “Solicitud” hasta la señal de “Respuesta”. Esto ayuda a validar el rendimiento frente a las especificaciones.

🚀 Conceptos avanzados en el análisis de temporización

A medida que los sistemas se vuelven más rápidos y complejos, los diagramas de temporización básicos evolucionan hacia requisitos de análisis sofisticados.

1. Metastabilidad

La metastabilidad ocurre cuando un flip-flop recibe una entrada que viola los requisitos de tiempo de setup o hold. En lugar de resolverse claramente a un 0 o un 1, la salida entra en un estado indefinido durante una duración impredecible.

- Causa:Sucede con frecuencia cuando señales asíncronas cruzan dominios de reloj.

- Mitigación:Utilice cadenas de sincronización (varios flip-flops en serie) para reducir la probabilidad de metastabilidad.

- Visual:En un diagrama de temporización, esto se ve como una señal que oscila o tarda un tiempo anormalmente largo en estabilizarse.

2. Presupuestos de tiempo de setup y hold

Los ingenieros calculan un presupuesto de temporización para asegurarse de que el sistema funcione a la frecuencia máxima. Esto implica restar todos los retrasos (alambre, puerta, desfase de reloj) al período del reloj.

Si el retardo total excede el tiempo disponible, la frecuencia máxima de operación debe reducirse.

3. Temporización de interfaz de alta velocidad

Interfaces como la memoria DDR o PCIe requieren una temporización extremadamente precisa. Estos diagramas a menudo incluyen:

- Diagramas de ojo: Una superposición de muchas transiciones de señal para visualizar la calidad de la señal.

- Distorsión de ciclo de trabajo: Asegurando que los tiempos alto y bajo estén equilibrados.

- Alineación de fase: Asegurando que los datos y la señal de reloj lleguen sincronizados a través de múltiples bits.

4. Estados de gestión de energía

Los dispositivos modernos entran en modos de bajo consumo. Los diagramas de temporización deben tener en cuenta la latencia de activación. Por ejemplo, una señal que activa la alimentación a un periférico debe ocurrir antes de que el dispositivo esté listo para recibir datos.

📝 Mejores prácticas para la documentación

Una documentación clara previene errores durante el desarrollo y la depuración. Adhiera a estas normas al crear o revisar diagramas de temporización.

- Escalado consistente: Utilice escalas de tiempo consistentes en diagramas relacionados para permitir una comparación fácil.

- Etiquetas claras: Cada señal debe etiquetarse con su función y polaridad lógica (por ejemplo,

RESET#para activo bajo). - Niveles de zoom: Proporcione una vista general de alto nivel y una vista ampliada de las transiciones críticas (como las ventanas de establecimiento/retención).

- Codificación por colores: Utilice colores para distinguir entre diferentes dominios de voltaje o fuentes de reloj (por ejemplo, rojo para reloj, azul para datos).

- Control de versiones: Los requisitos de temporización cambian. Asegúrese de que los diagramas estén versionados para coincidir con la revisión del hardware.

🛠️ Errores comunes y solución de problemas

Incluso los ingenieros con experiencia enfrentan problemas de temporización. Aquí tiene escenarios comunes y cómo abordarlos.

Error 1: Ignorar el retardo de traza

Las trazas de la PCB tienen longitud física, lo que introduce retardo. A frecuencias altas, unos pocos centímetros de cable pueden equivaler a un ciclo de reloj.

- Solución: Tenga en cuenta la longitud de la traza en sus cálculos de presupuesto de tiempo.

Pitfall 2: Entradas flotantes

Las entradas no conectadas pueden flotar hacia un voltaje intermedio, causando oscilación.

- Solución: Asegúrese de que todas las entradas tengan resistores de tirar definidos hacia arriba o hacia abajo.

Pitfall 3: Condiciones de carrera

Cuando dos señales cambian simultáneamente, el orden de llegada determina el resultado.

- Solución: Utilice lógica de sincronización o máquinas de estado para secuenciar eventos.

Pitfall 4: Sobrepico y subpico

Las reflexiones de señal pueden causar que los voltajes excedan las líneas de alimentación (sobrepico) o caigan por debajo del nivel de tierra (subpico).

- Solución: Implemente resistores de terminación adecuados y coincidencia de impedancia.

🔗 Aplicaciones del mundo real

Los diagramas de temporización se aplican en diversos campos de la ingeniería.

1. Interfaces de memoria

La DRAM y la SDRAM requieren secuencias de temporización estrictas para operaciones de lectura/escritura. La latencia de CAS y el retardo de RAS a CAS son parámetros críticos visualizados en estos diagramas.

2. Comunicación de microcontroladores

Protocolos como I2C, SPI y UART dependen de relaciones de temporización específicas entre las líneas de reloj y datos. Por ejemplo, en I2C, la línea de datos debe permanecer estable mientras el reloj está en alto.

3. Secuenciación de fuentes de alimentación

Los sistemas complejos requieren que las líneas de alimentación se enciendan en un orden específico. Los diagramas de temporización aseguran que el voltaje del núcleo esté estable antes de aplicar el voltaje de I/O.

🎯 Resumen de los puntos clave

Dominar los diagramas de temporización requiere paciencia y atención al detalle. Los siguientes puntos resumen el conocimiento esencial para un diseño y análisis efectivos.

- El tiempo es crítico:La lógica digital depende de relaciones temporales precisas entre las señales.

- Preparación y retención: Estas son las dos restricciones más comunes que determinan la velocidad máxima de operación.

- Verificación visual: Los diagramas le permiten ver posibles conflictos antes de que se construya el hardware.

- El contexto importa: Siempre considere el entorno físico (PCB, temperatura, voltaje) que afecta el tiempo de señal.

- Estandarización:Utilice símbolos y notación estándar para garantizar la claridad en la comunicación entre equipos.

Al aplicar estos principios, asegura que sus sistemas digitales sean robustos, confiables y eficientes. La capacidad de interpretar y crear estos diagramas es una habilidad fundamental que diferencia los diseños funcionales de aquellos que fallan en el campo.

📈 Avanzando

A medida que la tecnología avanza, las restricciones de tiempo se vuelven más estrictas. Los sistemas modernos operan a velocidades de gigahercios donde los nanosegundos importan enormemente. El aprendizaje continuo sobre la integridad de la señal y el cierre de tiempos es necesario para los ingenieros que trabajan en hardware de vanguardia.

Comience analizando esquemas existentes y sus diagramas de tiempo correspondientes. Practique la medición de intervalos e identificación de violaciones. Con el tiempo, los patrones se volverán intuitivos, permitiéndole predecir problemas antes de que se manifiesten físicamente.