Comprender el flujo de señales a lo largo del tiempo es fundamental en electrónica digital. Para los ingenieros de pregrado, dominar la interpretación de diagramas de tiempo no es solo un ejercicio académico; es una habilidad crítica para diseñar sistemas confiables. Estas representaciones visuales muestran el comportamiento de las señales a lo largo de un eje temporal, revelando relaciones entre ciclos de reloj, validez de datos y señales de control. Sin una comprensión sólida de estas técnicas, incluso circuitos simples pueden fallar en condiciones del mundo real.

Esta guía cubre los principios fundamentales necesarios para leer, crear y analizar diagramas de tiempo de manera efectiva. Exploraremos la mecánica del diseño síncrono y asíncrono, la importancia de los tiempos de establecimiento y retención, y cómo evitar los errores comunes que provocan fallas en los circuitos. Al final de este artículo, tendrás una base sólida para abordar problemas complejos de lógica digital.

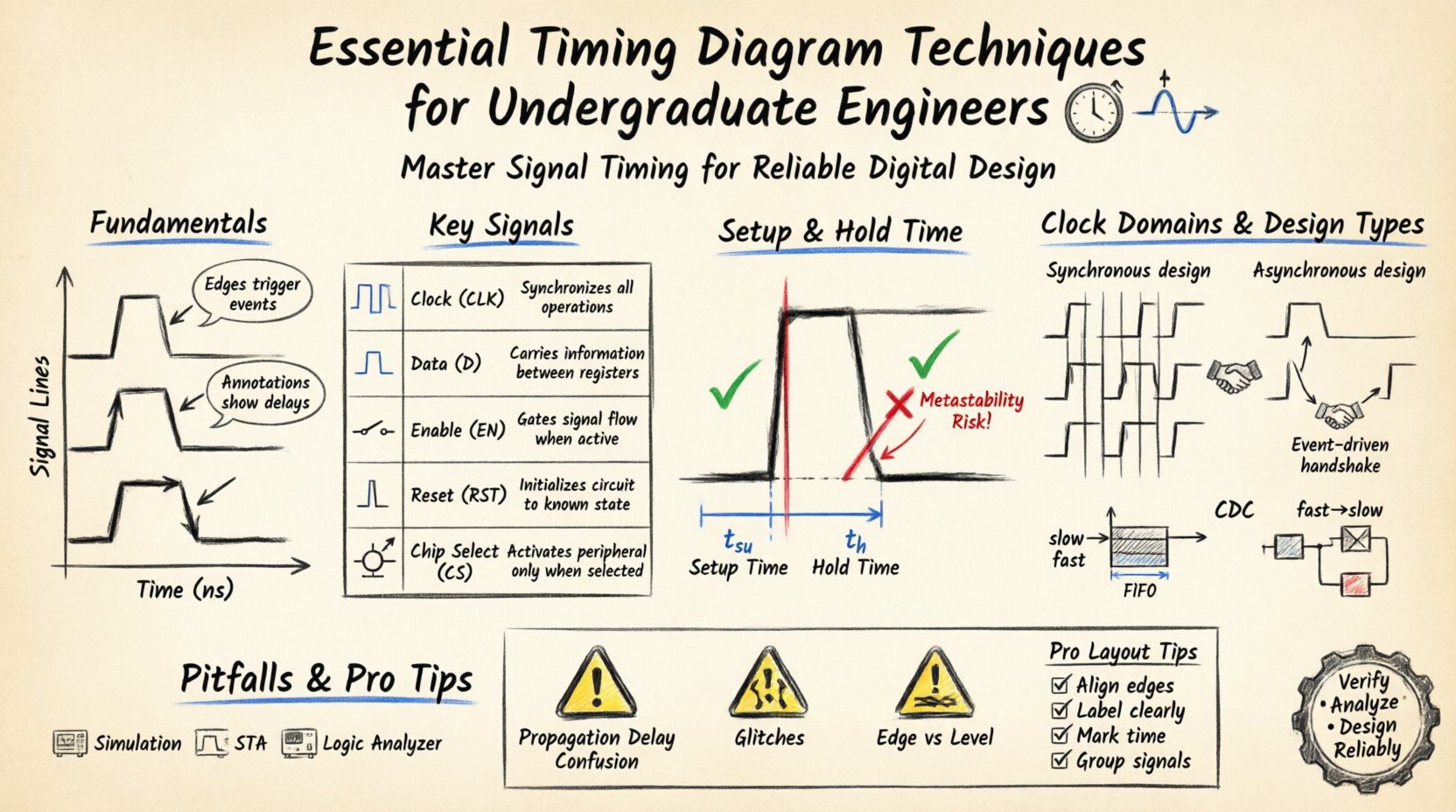

1. Fundamentos de los diagramas de tiempo 📐

Un diagrama de tiempo es una representación gráfica de señales a lo largo del tiempo. Permite a los ingenieros visualizar el estado de diversas líneas en un circuito digital. A diferencia de los diagramas lógicos que muestran conectividad, los diagramas de tiempo muestran el comportamiento. Son esenciales para depurar, verificar diseños y comunicar interacciones entre señales en módulos de hardware.

Componentes clave de un diagrama de tiempo

- Eje del tiempo (eje X):Representa la progresión del tiempo. Normalmente se marca en nanosegundos (ns) o ciclos de reloj.

- Líneas de señal (eje Y):Líneas horizontales que representan cables individuales o buses. Cada línea corresponde a un nombre de señal específico.

- Niveles lógicos:Las señales son generalmente binarias, representadas como Alta (1) o Baja (0). A veces, aparecen estados de ‘Alta-Z’ (alta impedancia) en diseños de bus.

- Transiciones (edges):Las transiciones verticales indican un cambio de estado. Las transiciones ascendentes (de Baja a Alta) y descendentes (de Alta a Baja) son críticas para activar eventos.

- Anotaciones:Las etiquetas de texto indican a menudo retrasos, tiempos específicos o condiciones que afectan a la señal.

¿Por qué el tiempo importa en la lógica digital

Los sistemas digitales dependen de una sincronización precisa. Si una señal llega demasiado temprano o demasiado tarde respecto a un borde de reloj, el sistema puede interpretar incorrectamente los datos. Los diagramas de tiempo hacen visibles estas restricciones. Ayudan a responder preguntas como:

- ¿La data está estable antes del borde del reloj?

- ¿Cuánto tiempo tarda una señal en propagarse a través de una puerta?

- ¿Dos relojes de dominios diferentes se interfieren entre sí?

2. Señales y componentes clave ⚡

Antes de analizar formas de onda complejas, debes reconocer las señales estándar utilizadas en ingeniería digital. Estas señales determinan cómo se mueve la data y cuándo se considera válida.

Tipos comunes de señales

| Nombre de la señal | Función | Comportamiento típico |

|---|---|---|

| Reloj (CLK) | Fuente de sincronización | Pulsando regularmente entre 0 y 1 |

| Datos (D) | Portador de información | Cambia de estado según la entrada o la lógica |

| Habilitar (EN) | Activa un módulo | Alto para permitir la operación, bajo para deshabilitar |

| Reiniciar (RST) | Inicializa el estado | Pulso activo bajo o activo alto al inicio |

| Seleccionar chip (CS) | Selecciona un dispositivo | Activo bajo para direccionar un componente específico |

Comprender el estado activo de las señales de control es crucial. Algunas señales son activas alto, lo que significa que funcionan cuando el voltaje es alto. Otras son activas bajo, indicadas por una barra sobre el nombre (por ejemplo, /REINICIAR o RST_N), lo que significa que funcionan cuando el voltaje es bajo.

3. Análisis de tiempo de preparación y retención 🕒

Uno de los aspectos más críticos del análisis de temporización implica los tiempos de preparación y retención. Estos parámetros definen la ventana en la que los datos deben permanecer estables respecto a una transición de reloj. Violar estas restricciones conduce a corrupción de datos o metastabilidad.

Tiempo de preparación (tsu)

El tiempo de preparación es la duración mínima durante la cual los datos deben permanecer establesantesque llegue la transición activa del reloj. Si los datos cambian demasiado cerca de la transición del reloj, el flip-flop podría no capturar el valor correcto.

- Requisito:Los datos deben permanecer estables durante tsuantes de la transición ascendente.

- Consecuencia de la violación: El registro puede capturar datos incorrectos o entrar en un estado indefinido.

Tiempo de retención (th)

El tiempo de retención es la duración mínima durante la cual los datos deben permanecer establesdespuésla transición activa del reloj. El flip-flop necesita un momento para capturar el valor antes de que llegue nuevo dato.

- Requisito:Los datos deben permanecer estables durante thdespués de la transición ascendente.

- Consecuencia de la violación:Similar a las violaciones de configuración, esto causa errores de datos o metastabilidad.

Visualización de los tiempos de configuración y retención

Al leer un diagrama de tiempos, observe la señal de datos respecto a la transición del reloj. La línea de datos debe ser plana y sin cambios durante la ventana de configuración (antes) y la ventana de retención (después). Si la línea de datos cambia dentro de estas ventanas, es probable que el diseño tenga errores.

4. Cruce de dominios de reloj ⏱️

En sistemas complejos, diferentes partes del circuito pueden operar a velocidades o frecuencias de reloj distintas. El movimiento de datos entre estos dominios de reloj distintos se conoce como cruce de dominios de reloj (CDC). Este proceso introduce desafíos significativos de tiempo.

Tipos de dominios de reloj

- Misma frecuencia, misma fase:Diseño síncrono. Se aplica un análisis de tiempo simple.

- Misma frecuencia, fase diferente:Requiere comprobaciones de alineación de fase.

- Frecuencias diferentes:Requiere técnicas de sincronización como acuerdos de mano o búferes FIFO.

Manejo del CDC en diagramas de tiempo

Al analizar diagramas con múltiples dominios de reloj, asegúrese de distinguir claramente las líneas de reloj. Los datos que cruzan desde un dominio lento a uno rápido pueden ser riesgosos si no se gestionan. Por el contrario, el cruce de rápido a lento puede provocar pérdida de datos si el receptor muestrea demasiado rápido.

- Protocolos de acuerdo de mano:Utilice señales de válido/listo para confirmar la finalización de la transferencia de datos.

- Búferes FIFO:Desacople las tasas de producción y consumo.

- Sincronizadores:Utilice flip-flops de múltiples etapas para reducir el riesgo de metastabilidad.

5. Diseño síncrono frente al asíncrono 🔄

La arquitectura del diseño determina cómo se ven los diagramas de tiempo. Comprender la diferencia ayuda a predecir el comportamiento de las señales.

Diseño síncrono

La mayoría de la lógica digital es síncrona. Todos los cambios de estado ocurren en el borde de una señal de reloj central.

- Previsibilidad:Más fácil de analizar porque el tiempo está controlado.

- Diagramas de tiempo:Patrones regulares, tipo cuadrícula. Los cambios de datos se alinean con los bordes del reloj.

- Limitaciones:El desajuste de reloj puede convertirse en un problema en diseños grandes.

Diseño asíncrono

Los cambios de estado ocurren según la llegada de señales, no según un reloj global. Esto es común en protocolos de intercambio de señales y en el manejo de interrupciones.

- Flexibilidad:Puede ser más rápido para tareas específicas, ya que espera únicamente los datos.

- Diagramas de tiempo:Irregular. Las señales dependen de eventos anteriores, no de intervalos de tiempo fijos.

- Riesgos:Prono a condiciones de carrera y peligros si no se diseña con cuidado.

6. Trampas comunes y errores ❌

Incluso los ingenieros con experiencia cometen errores al interpretar o crear diagramas de tiempo. Ser consciente de estos errores comunes puede ahorrar mucho tiempo en depuración.

1. Ignorar el retardo de propagación

Las señales no cambian de forma instantánea. Las puertas tienen un retardo de propagación. Si dibuja un diagrama asumiendo cambios inmediatos, su simulación no coincidirá con la realidad.

- Solución:Siempre incluya valores de retardo entre las transiciones lógicas en sus diagramas.

2. Interpretar incorrectamente las señales activas en bajo

Una señal etiquetada/CSestá en bajo cuando está activa. Si asume que está en alto, su lógica estará invertida.

- Corrección:Revise la hoja de datos o el esquemático para determinar los estados activos. Busque círculos en las puertas lógicas.

3. Ignorar los picos

Los picos son pulsos cortos e involuntarios. Pueden ocurrir cuando las señales viajan por caminos diferentes con retardos variables.

- Corrección:Utilice lógica libre de riesgos o agregue etapas de filtrado en el diseño.

4. Confundir borde frente a nivel

Algunos circuitos se activan en el borde ascendente, otros en el borde descendente, y otros en el nivel mismo.

- Corrección:Verifique la condición de activación en la especificación del componente.

7. Lectura y creación de diagramas profesionales 📝

La comunicación clara es vital en ingeniería. Un diagrama de temporización bien dibujado transmite información compleja a simple vista. Aquí tiene las mejores prácticas para crearlos.

Mejores prácticas para el diseño

- Alinear bordes:Asegúrese de que las señales relacionadas cambien en intervalos consistentes.

- Etiquetar claramente:Utilice nombres de señales, no solo líneas genéricas.

- Marcar el tiempo:Indique la duración de los ciclos o retardos específicos.

- Agrupar señales:Organice las señales relacionadas (como las líneas de bus de datos) juntas.

Proceso paso a paso de creación

- Identificar relojes:Dibuje primero las líneas de reloj. Son la columna vertebral del temporizado.

- Agregar señales de control:Coloque las líneas de habilitación, reinicio y selección de chip.

- Representar datos:Agregue las líneas de datos según el flujo lógico.

- Anotar:Agregue notas sobre tiempos de establecimiento/retención o retardos específicos.

- Revisión:Verifique las violaciones y la coherencia lógica.

8. Análisis de escenarios del mundo real 🔍

Consideremos un escenario que implica una operación de lectura de memoria. Esta es una tarea común para los ingenieros que trabajan con microcontroladores.

Ciclo de lectura de memoria

En una lectura de memoria, el procesador envía una dirección, activa una orden de lectura y espera los datos.

- Bus de direcciones:Válida antes del borde del reloj.

- Seleccionar chip:Pasa a bajo para activar la memoria.

- Comando de lectura:Pasa a bajo para iniciar la transferencia.

- Bus de datos:Permanece en estado de alta impedancia hasta que la memoria lo active.

- Temporalización:Los datos deben estar estables antes de que el procesador los muestree.

Consideraciones sobre la integridad de la señal

A medida que aumenta la frecuencia, la integridad de la señal se convierte en un factor clave. Las reflexiones, el acoplamiento cruzado y el ruido pueden distorsionar las formas de onda. Los diagramas de temporalización en diseños de alta velocidad deben tener en cuenta estos problemas de capa física.

- Tasa de subida:Qué tan rápido cambia la señal. Demasiado rápido causa ruido; demasiado lento causa errores de temporización.

- Niveles de voltaje:Asegúrese de que los umbrales lógicos se cumplan ante variaciones de temperatura y voltaje.

9. Conceptos avanzados de temporalización 🧠

Para quienes buscan profundizar sus conocimientos, varios conceptos avanzados amplían el análisis de temporalización básico.

Metastabilidad

La metastabilidad ocurre cuando un flip-flop no puede establecerse en un estado estable de 0 o 1 dentro del tiempo requerido. Esto suele ocurrir cuando los datos cambian demasiado cerca del borde del reloj.

- Probabilidad:Es un evento probabilístico, no determinista.

- Mitigación:Utilice cadenas de sincronización (varios flip-flops en serie) para reducir la probabilidad a casi cero.

Alineación de reloj

La alineación de reloj es la diferencia en los tiempos de llegada de la señal de reloj en diferentes partes del circuito. Una alineación positiva (llega más tarde) puede ayudar al tiempo de establecimiento, pero perjudica el tiempo de retención. Una alineación negativa hace lo contrario.

- Impacto en el diseño:La alineación debe tenerse en cuenta en los presupuestos de tiempo.

- Medición:Utilice osciloscopios o herramientas de simulación para medir la alineación.

Jitter

El jitter es la desviación del borde del reloj respecto a su posición ideal. Reduce los márgenes efectivos de establecimiento y retención.

- Tipos:Jitter de período, jitter ciclo a ciclo y jitter aleatorio.

- Impacto:Un alto jitter limita la frecuencia máxima de operación de un sistema.

10. Herramientas y metodologías 🛠️

Aunque el análisis manual es educativo, la ingeniería moderna depende de herramientas. Sin embargo, comprender la teoría subyacente es lo que te permite usar estas herramientas de forma efectiva.

Software de simulación

Los lenguajes de descripción de hardware (HDL) permiten la simulación. Estas herramientas generan diagramas de tiempo automáticamente a partir del código. Debes entender la salida para verificar la corrección del código.

Análisis estático de tiempo (STA)

Las herramientas de STA verifican matemáticamente que todas las rutas cumplan con los requisitos de tiempo sin simulación. Verifican violaciones de establecimiento y retención en todas las condiciones (temperatura, voltaje).

Depuración con analizadores lógicos

Los depuradores de hardware capturan señales reales de una placa. Muestran diagramas de tiempo que coinciden con la realidad, ayudando a identificar problemas de capa física que la simulación podría pasar por alto.

Conclusión 🏁

Los diagramas de tiempo son el lenguaje del comportamiento de las señales digitales. Cerraron la brecha entre la lógica abstracta y la realidad física. Para los ingenieros de pregrado, invertir tiempo en dominar estas técnicas rinde dividendos a lo largo de toda tu carrera. Ya sea que estés diseñando un contador simple o un procesador complejo, la capacidad de leer y analizar las restricciones de tiempo es imprescindible.

Al centrarse en los tiempos de establecimiento y retención, comprender los dominios de reloj y evitar los errores comunes, construyes una base sólida. Recuerda siempre verificar los estados activos y tener en cuenta los retardos de propagación. A medida que avances, encontrarás escenarios más complejos, pero los principios fundamentales permanecen iguales. Sigue practicando el análisis de diagramas, y tus diseños se volverán más confiables y eficientes.

Sigue perfeccionando tus habilidades estudiando hojas de datos y examinando formas de onda de circuitos del mundo real. El campo de la ingeniería digital evoluciona rápidamente, pero los fundamentos del análisis de tiempo permanecen constantes.