En el mundo complejo de la ingeniería embebida, el tiempo es todo. Un microcontrolador podría funcionar perfectamente en simulación pero fallar catastróficamente en el hardware debido a unos pocos nanosegundos de retraso. Es aquí donde el diagrama de temporización se convierte en una herramienta indispensable. Estas representaciones visuales muestran el comportamiento de las señales con el paso del tiempo, proporcionando una imagen clara de cómo interactúan los componentes dentro de un sistema digital. Ya sea que estés depurando un fallo de comunicación o diseñando una nueva interfaz de periférico, comprender cómo leer y crear diagramas de temporización es fundamental.

Esta guía cubre los mecanismos esenciales de la temporización de señales, desde las definiciones básicas hasta las interacciones complejas de protocolos. Exploraremos cómo interpretar formas de onda, construir diagramas precisos a partir de datos de medición e identificar los errores comunes que provocan inestabilidad del sistema. Al dominar estas herramientas visuales, adquirirás la capacidad de predecir el comportamiento del sistema y validar diseños antes de que siquiera salgan de la mesa de trabajo.

🔍 Comprender los fundamentos de la temporización de señales

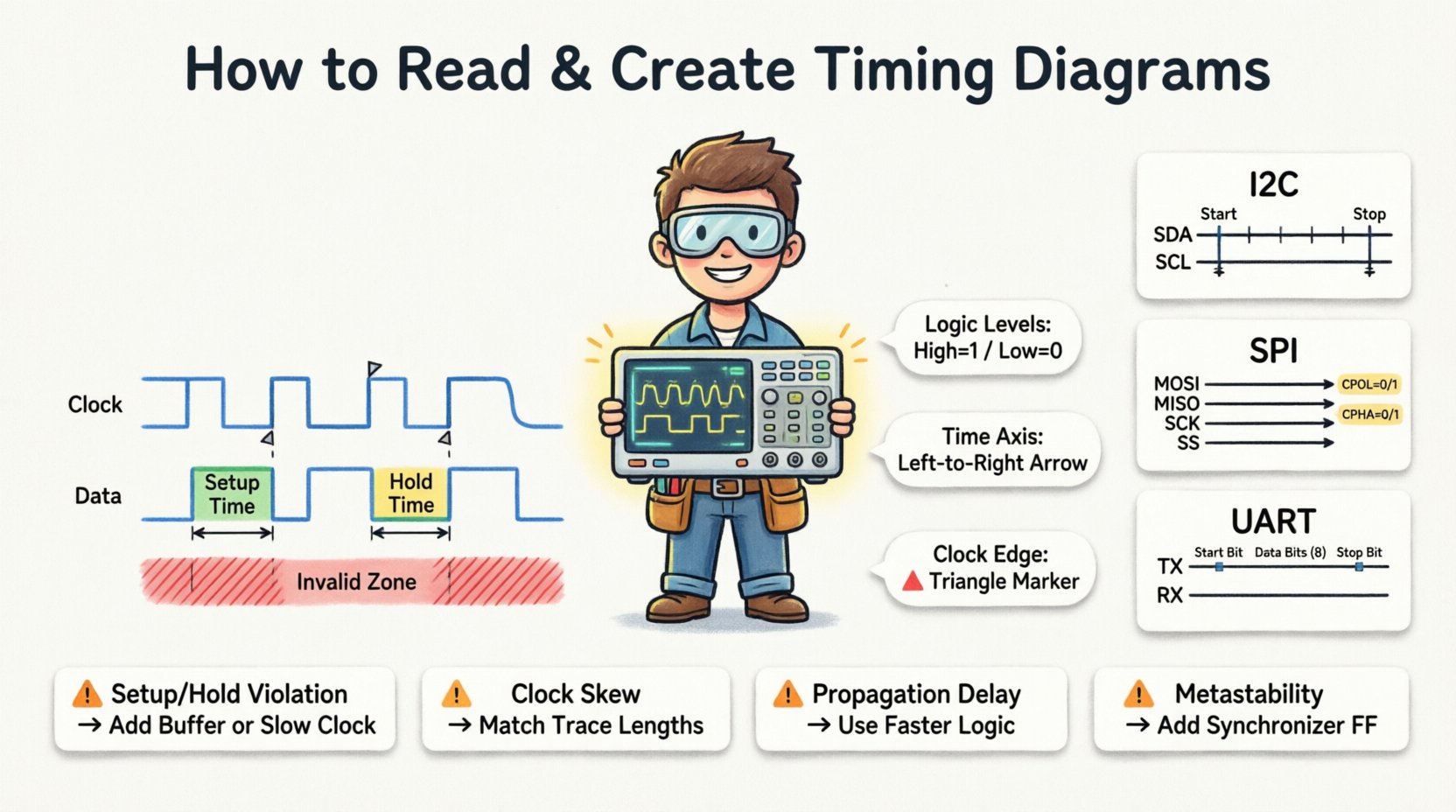

Un diagrama de temporización no es meramente un dibujo; es una representación matemática de estados lógicos respecto a un eje de tiempo. En los sistemas embebidos, principalmente tratamos con niveles lógicos digitales, que son binarios: Alto (1) y Bajo (0). Sin embargo, es en las transiciones entre estos niveles donde reside la complejidad.

- Niveles lógicos:La mayoría de los sistemas embebidos operan con umbrales de voltaje específicos. Por ejemplo, un sistema de 3.3V define Alto como cualquier valor por encima de 2,0V y Bajo como cualquier valor por debajo de 0,8V.

- Eje de tiempo:El tiempo fluye de izquierda a derecha. La separación horizontal representa la duración de estados específicos o el retraso entre eventos.

- Trazados de señal: Cada línea horizontal representa un cable o red específico. Varias líneas apiladas verticalmente permiten comparar las relaciones entre señales.

Al analizar un sistema, estás buscando causalidad. ¿La señal de reloj desencadena el cambio de datos? ¿La señal de habilitación debe estar activa antes de que los datos sean válidos? Los diagramas de temporización responden a estas preguntas de forma visual.

🛠️ Componentes clave de un diagrama de temporización

Para interpretar correctamente un diagrama, debes reconocer los elementos estándar utilizados para indicar el comportamiento de la señal. Estos componentes definen las reglas de interacción para el hardware.

| Componente | Descripción | Indicador visual |

|---|---|---|

| Nombre de la señal | Identifica el cable o red específico | Etiqueta de texto a la izquierda |

| Nivel lógico | Estado Alto (1) o Bajo (0) | Línea horizontal plana en la parte superior o inferior |

| Borde de transición | Cambio de Alto a Bajo o viceversa | Línea vertical que conecta niveles |

| Borde de reloj | Punto de disparo para la lógica síncrona | Línea punteada o marcador triangular |

| Zona inválida | Región donde no se puede leer los datos | Área sombreada o rayada |

Comprender estos componentes te permite descomponer interacciones complejas. Por ejemplo, un área sombreada suele indicar un requisito de tiempo de configuración o retención en el que el dispositivo receptor no puede capturar los datos de forma confiable.

👁️ Cómo leer un diagrama de tiempos paso a paso

Leer un diagrama de tiempos requiere un enfoque sistemático. En esencia, estás traduciendo un patrón visual en una secuencia de eventos. Sigue este proceso para asegurar precisión.

1. Identifica la fuente del reloj

La mayoría de los sistemas embebidos son síncronos, lo que significa que una señal de reloj determina el ritmo de las operaciones. Localiza la traza del reloj. Normalmente presenta una onda cuadrada regular y periódica.

- Verifica la frecuencia. ¿Es de 1 MHz o 100 MHz? Esto determina la velocidad de todo el sistema.

- Identifica el tipo de borde. ¿El dispositivo se activa en el borde ascendente (Bajo a Alto) o en el borde descendente (Alto a Bajo)?

2. Mapea las ventanas de validez de los datos

Los datos solo son válidos durante ventanas específicas respecto al reloj. Busca la relación entre el borde del reloj y la línea de datos.

- Tiempo de configuración: Los datos deben permanecer estables durante un período determinado antes de el borde del reloj.

- Tiempo de retención: Los datos deben permanecer estables durante un período determinado después de el borde del reloj.

Si los datos cambian durante estas ventanas, se produce una violación de tiempo, lo que puede provocar metastabilidad o captura incorrecta de datos.

3. Analiza las señales de control

Las señales de control como Chip Select (CS), Habilitar (EN) o Reiniciar (RST) determinan cuándo puede ocurrir la comunicación.

- ¿El Chip Select está activo en bajo o en alto?

- ¿La señal de Habilitar debe activarse antes de que el reloj comience a conmutar?

- ¿Existen eventos asíncronos que sobrescriban la lógica del reloj?

4. Verifica los mecanismos de handshaking

Muchos protocolos utilizan handshaking para gestionar el control de flujo. Busca señales de Confirmación (ACK) o Listo (RDY).

- ¿El emisor espera una señal antes de transmitir el siguiente byte?

- ¿Existen condiciones de tiempo de espera representadas en el diagrama?

📐 Cómo crear diagramas de tiempos precisos

Crear un diagrama de tiempos es tan importante como leerlo. Sirve como especificación para los ingenieros de hardware y como guía de verificación para los desarrolladores de software. Puedes generarlos a partir de requisitos, herramientas de medición o datos de simulación.

Paso 1: Definir los requisitos del protocolo

Antes de dibujar, reúne las especificaciones. Estas generalmente provienen de la hoja de datos del componente con el que estás interactuando.

- Extrae las frecuencias mínima y máxima del reloj.

- Anota los niveles de voltaje para lógica Alta y Baja.

- Registra las restricciones de tiempo de preparación y retención.

Paso 2: Capturar los datos de las señales

Utiliza herramientas de hardware para capturar el comportamiento del mundo real. Esto asegura que tu diagrama refleje la realidad en lugar de ideales teóricos.

- Osciloscopios:Ideal para la integridad de señales analógicas y los niveles de voltaje.

- Analizadores lógicos:Óptimo para transiciones de estado digital y temporización de múltiples canales.

- Modelos de simulación:Bueno para verificar la lógica antes de que el hardware esté disponible.

Paso 3: Graficar las formas de onda

Dibuja las señales en orden cronológico. Asegúrate de que la escala de tiempo sea consistente en todos los canales.

- Utiliza líneas rectas para los niveles lógicos.

- Utiliza líneas diagonales para las transiciones, para indicar los tiempos de subida y bajada.

- Etiqueta los puntos críticos, como el borde del reloj y el cambio de datos.

Paso 4: Anotar las restricciones críticas

Las anotaciones proporcionan contexto que las imágenes por sí solas no pueden transmitir.

- Marca explícitamente las ventanas de tiempo de preparación y retención.

- Indica la duración de estados específicos del protocolo (por ejemplo, Bit de inicio, Bit de parada).

- Resalta cualquier latencia o retraso conocido en la ruta de la señal.

🌐 Diagramas de tiempos en protocolos embebidos comunes

Diferentes protocolos de comunicación tienen características de temporización distintas. Comprender estas sutilezas es vital para la integración.

1. Circuito inter-integrado (I2C)

I2C es un bus serial síncrono de dos hilos. Utiliza SDA (Datos) y SCL (Reloj).

- Condición de inicio: SDA cambia de Alto a Bajo mientras SCL está en Alto.

- Condición de parada: SDA cambia de bajo a alto mientras SCL está en alto.

- Transferencia de datos: Los datos son válidos cuando SCL está en alto; los cambios ocurren cuando SCL está en bajo.

- ACK/NACK: El receptor baja SDA durante el noveno pulso de reloj para reconocer la recepción.

2. Interfaz periférica serial (SPI)

SPI es una bus síncrona de cuatro hilos que ofrece velocidades más altas que I2C.

- Líneas: MOSI (salida maestra), MISO (entrada maestra), SCK (reloj), SS (selección de esclavo).

- CPOL: La polaridad del reloj determina el estado de reposo (alto o bajo).

- CPHA: La fase del reloj determina cuándo se muestrea el dato (primer o segundo borde).

- Selección de chip: Debe activarse (activo) antes de que comience a conmutar el reloj.

3. Transmisor-receptor asíncrono universal (UART)

UART es asíncrono, lo que significa que no existe una señal de reloj compartida. El tiempo depende de las tasas de baudios.

- Bit de inicio: Baja la línea para indicar el comienzo de un marco.

- Bits de datos: Se transmiten primero los bits menos significativos, normalmente 8 bits.

- Bit de parada: Sube la línea para indicar el final de un marco.

- Paridad: Bit opcional para verificación de errores.

| Característica | I2C | SPI | UART |

|---|---|---|---|

| Reloj | Síncrono (compartido) | Síncrono (compartido) | Asíncrono (sin reloj) |

| Alambres | 2 (SDA, SCL) | 4+ (MOSI, MISO, SCK, SS) | 2 (TX, RX) |

| Dirección | Sí (dirección por byte) | No (basado en conexiones) | No |

| Velocidad máxima | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ Violaciones de temporización comunes y depuración

Incluso con un diseño cuidadoso, pueden ocurrir violaciones de temporización. Estas son a menudo la causa raíz de errores intermitentes que son difíciles de reproducir.

1. Violaciones de tiempo de preparación y retención

Esto ocurre cuando los datos llegan demasiado temprano o demasiado tarde en relación con el borde del reloj.

- Síntoma:Corrupción de datos o errores aleatorios en la captura del analizador lógico.

- Solución:Disminuya la velocidad del reloj o optimice las longitudes de las trazas del PCB.

2. Desviación de reloj

La desviación de reloj ocurre cuando la señal de reloj llega a diferentes componentes en tiempos distintos.

- Síntoma:Condiciones de carrera en las que un flip-flop captura datos antes de que otro esté listo.

- Solución:Ajuste las longitudes de las trazas o use una red dedicada de distribución de reloj.

3. Retardo de propagación

Las señales tardan tiempo en viajar a través de los cables y puertas. Las trazas largas añaden un retardo significativo.

- Síntoma:Problemas de integridad de señal o reflexiones en líneas de alta velocidad.

- Solución:Utilice resistores de terminación y mantenga las trazas lo más cortas posible.

4. Metastabilidad

Cuando las señales asíncronas cruzan dominios de reloj, el flip-flop receptor puede entrar en un estado metastable.

- Síntoma:Cuelgues del sistema o reinicios aleatorios.

- Solución:Utilice cadenas de sincronización (dos o más flip-flops en serie) para resolver la señal.

📝 Mejores prácticas para la documentación

Crear diagramas de temporización para la documentación garantiza que los desarrolladores futuros puedan entender el sistema sin necesidad de deshacer el hardware.

- Consistencia:Utilice símbolos y estilos de línea estándar en todos los diagramas del proyecto.

- Escala:Asegúrese de que el eje del tiempo sea lineal y claramente etiquetado con unidades (ns, µs, ms).

- Referencia:Enlace siempre el diagrama con la sección específica de la hoja de datos o el estándar del protocolo.

- Claridad:Evite el desorden. Si una señal es estática, muéstrelo como una línea plana en lugar de ruido de conmutación.

- Gestión de versiones:Actualice los diagramas cada vez que cambie significativamente el hardware o el firmware.

🔗 Reflexiones finales sobre la integridad de señal

Los diagramas de temporización cierran la brecha entre la lógica abstracta y la realidad física. Permiten a los ingenieros visualizar las restricciones invisibles de la electrónica digital. Al aprender a leerlos, puedes solucionar problemas complejos de hardware. Al aprender a crearlos, puedes diseñar sistemas robustos que funcionen de forma confiable en todas las condiciones.

El proceso requiere paciencia y atención al detalle. Cada borde, cada retardo y cada nivel de voltaje importa. A medida que los sistemas embebidos se vuelven más rápidos y complejos, la dependencia de diagramas de temporización precisos solo aumentará. Trátelos como especificaciones críticas, más que como documentación opcional.

Comience analizando las hojas de datos de los componentes que utiliza. Busque las especificaciones de temporización. Luego, intente dibujar los diagramas basándose en esos números. Compare sus dibujos con mediciones reales de sus herramientas. Este ciclo de predicción y verificación construye la intuición necesaria para el diseño de alto nivel de sistemas embebidos.

Recuerde que un diagrama es una herramienta de comunicación. Debe transmitir la información necesaria a otro ingeniero con la menor ambigüedad posible. Los diagramas de temporización claros y precisos reducen el tiempo de desarrollo y evitan revisiones costosas del hardware. Invierta el tiempo para dominar esta habilidad, y le traerá beneficios a lo largo de toda su carrera de ingeniería.