Comprender el comportamiento de los circuitos digitales requiere más que simplemente conocer las puertas lógicas. Exige una comprensión de cómo cambian las señales con el tiempo. Los diagramas de tiempo proporcionan el lenguaje visual para este análisis temporal. Representan el estado de diversas señales en relación con un reloj o un evento específico. Para los estudiantes de informática, dominar este concepto es esencial para diseñar sistemas confiables.

Esta guía explora la mecánica, las técnicas de lectura y los parámetros críticos involucrados en los diagramas de tiempo. Cubriremos todo, desde las transiciones básicas de señales hasta violaciones complejas de tiempo de preparación y retención. Al final de esta visión general, tendrás una base sólida para analizar las interacciones digitales.

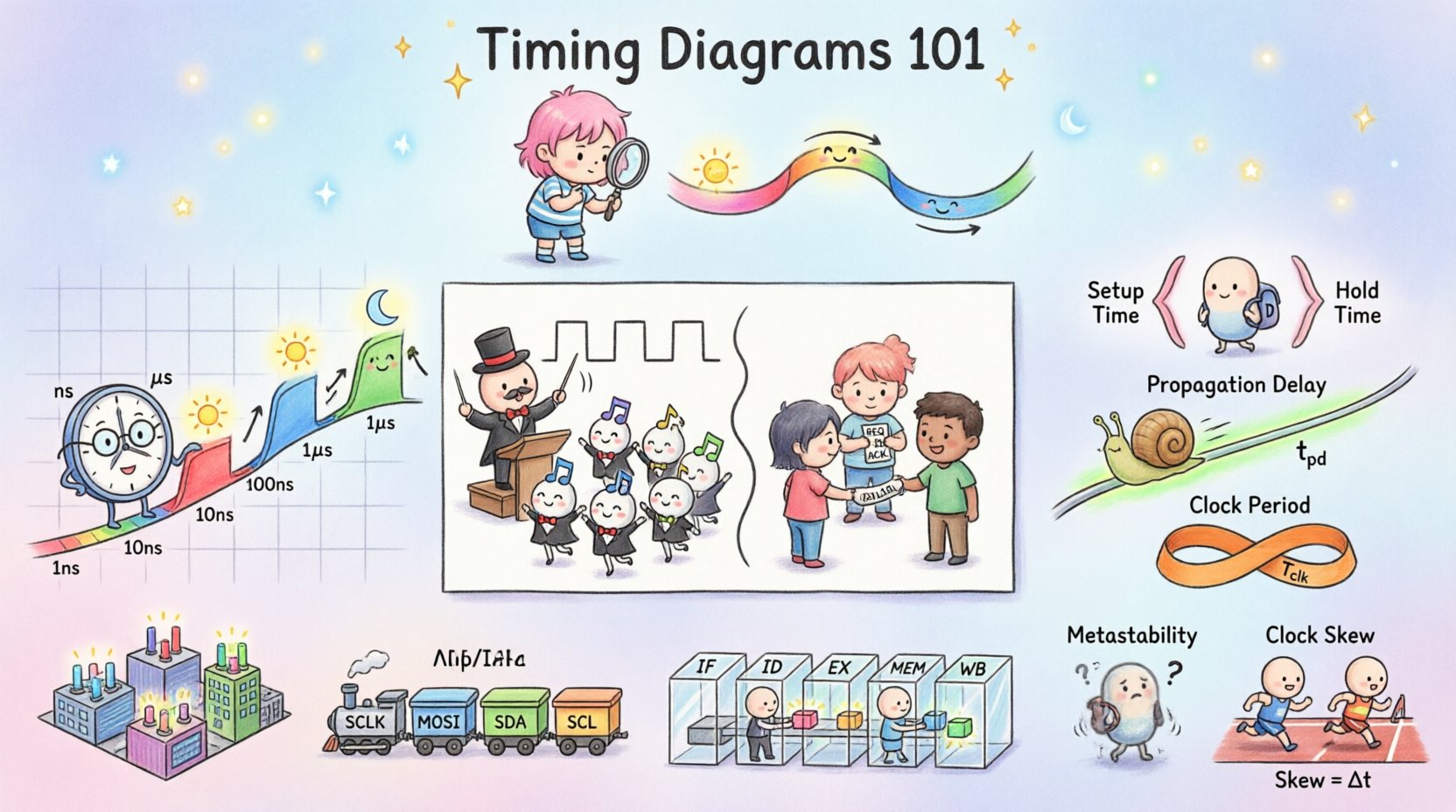

¿Qué es un diagrama de tiempo? ⏱️

Un diagrama de tiempo es una representación gráfica de la relación entre dos o más señales a lo largo del tiempo. Actúa como una línea de tiempo para los eventos digitales. Cada señal se representa como una línea horizontal. La posición vertical indica el nivel lógico o estado. El eje horizontal representa el paso del tiempo.

Estos diagramas son vitales para verificar que un sistema digital funcione correctamente. Ayudan a los ingenieros a predecir cómo se mueve la data a través de registros, buses y memoria. Sin ellos, depurar problemas de hardware se vuelve casi imposible. Cerraron la brecha entre la lógica abstracta y la realidad física.

Componentes principales de las señales digitales 📡

Antes de adentrarnos en los diagramas, uno debe comprender las señales mismas. Los sistemas digitales dependen de niveles de voltaje para representar datos binarios. Estos niveles no siempre son estáticos; pasan de un estado a otro.

- Nivel lógico alto (1):Normalmente representa un voltaje cercano a la fuente de alimentación.

- Nivel lógico bajo (0):Normalmente representa un voltaje cercano a tierra.

- Transiciones (edges): Los puntos de transición entre alto y bajo. Las transiciones ascendentes van de bajo a alto. Las transiciones descendentes van de alto a bajo.

- Estado estable: El período en el que una señal permanece constante.

- Margen de ruido: La tolerancia que tiene una señal antes de ser malinterpretada.

Los diagramas de tiempo visualizan estas transiciones. Muestran exactamente cuándo cambia una señal y cuánto tiempo permanece en ese estado. Esta precisión es crucial para garantizar la integridad de los datos.

Comprender el eje del tiempo ⏳

El eje horizontal es la columna vertebral de cualquier diagrama de tiempo. Representa la progresión del tiempo. En el diseño digital, este eje suele estar sincronizado con una señal de reloj. El reloj actúa como el latido del sistema.

Las unidades en el eje del tiempo varían según la velocidad del circuito. Las unidades comunes incluyen:

- Segundos (s):Utilizados para sistemas muy lentos.

- Milisegundos (ms):10^-3 segundos.

- Microsegundos (µs):10^-6 segundos.

- Nanosegundos (ns):10^-9 segundos. Estándar para los procesadores modernos.

- Picosegundos (ps):10^-12 segundos. Requerido para interfaces de alta velocidad.

Al leer un diagrama, busca las marcas de escala. Indican la duración de cada ciclo. Esto ayuda a calcular los retardos de propagación y a asegurar que las señales lleguen dentro de la ventana requerida.

Sistemas síncronos frente a asíncronos 🔄

Los sistemas digitales generalmente se dividen en dos categorías según cómo manejan el tiempo. Comprender esta diferencia es clave para dibujar diagramas precisos.

1. Sistemas síncronos

En los diseños síncronos, todos los cambios de estado ocurren respecto a una señal de reloj global. El diagrama de tiempos mostrará una onda de reloj periódica. Cada flip-flop se actualiza en el borde activo de este reloj.

- Ventajas:Comportamiento predecible. Más fácil de verificar.

- Desafíos:El desfase del reloj puede causar problemas si las señales llegan en tiempos diferentes.

- Característica del diagrama:Las líneas verticales a menudo se alinean con los bordes del reloj para mostrar los momentos de captura.

2. Sistemas asíncronos

Los diseños asíncronos no dependen de un reloj global. En su lugar, utilizan protocolos de intercambio de señales o señales locales para desencadenar acciones. Los diagramas de tiempo aquí son más irregulares.

- Ventajas:Menor consumo de energía en algunos casos. Tiempos de respuesta promedio más rápidos.

- Desafíos:Complejo de verificar. Propenso a condiciones de carrera.

- Característica del diagrama:Las señales se activan mutuamente sin un ritmo fijo.

Parámetros críticos de tiempo 📏

Mediciones específicas definen la fiabilidad de un diagrama de tiempo. Estos parámetros determinan si un circuito funcionará correctamente bajo todas las condiciones.

| Parámetro | Descripción | Significación |

|---|---|---|

| Retardo de propagación | Tiempo que tarda una señal en viajar desde la entrada hasta la salida. | Limita la frecuencia máxima de operación. |

| Tiempo de preparación | Los datos deben permanecer estables antes del borde del reloj. | Asegura que el bloqueo capture el valor correcto. |

| Tiempo de retención | Los datos deben permanecer estables después del borde del reloj. | Evita que el bloqueo lea un valor que está cambiando. |

| Período del reloj | Duración de un ciclo completo de la señal de reloj. | Define la velocidad del sistema. |

| Ciclo de trabajo | Porcentaje del período en que la señal está en alto. | Afecta el consumo de energía y los márgenes de tiempo. |

Análisis profundo: Tiempos de preparación y retención

Los tiempos de preparación y retención son las restricciones más críticas para la lógica secuencial. Si se violan, el sistema puede entrar en un estado metastable donde la salida es indefinida.

Violación del tiempo de preparación: Esto ocurre cuando los datos cambian demasiado cerca del borde del reloj. El circuito no tiene suficiente tiempo para prepararse para la captura. El resultado suele ser un error lógico.

Violación del tiempo de retención: Esto ocurre cuando los datos cambian demasiado pronto después del borde del reloj. El circuito todavía está tratando de capturar el valor anterior. Esto suele ser más difícil de corregir porque depende de la disposición física.

Lectura y análisis de diagramas 🔍

Analizar un diagrama de tiempos requiere un enfoque sistemático. Siga estos pasos para interpretar los datos visuales con precisión.

- Identifique el reloj: Encuentre la señal periódica. Este es su punto de referencia.

- Localice los bordes activos: Determine si el sistema se activa en bordes ascendentes o descendentes.

- Rastree las dependencias de las señales: Observe cómo los cambios en una señal afectan a otras.

- Verifique los picos: Busque pulsos cortos que podrían ser ruido o transiciones no deseadas.

- Verifique las restricciones: Asegúrese de que los tiempos de preparación y retención se respeten para todos los registros.

Considere un escenario simple de transferencia de datos. Una CPU envía datos a la memoria. El diagrama de tiempos mostrará primero la estabilización de las líneas de dirección, seguidas por las líneas de datos y finalmente la señal de escritura. Cada paso debe ocurrir dentro de una ventana específica.

Violaciones comunes y su impacto ⚠️

Incluso los ingenieros con experiencia enfrentan problemas de temporización. Comprender las violaciones comunes ayuda en la resolución de problemas.

1. Metastabilidad

Cuando una señal viola el tiempo de setup o hold, la salida del flip-flop puede oscilar antes de estabilizarse. Este estado se denomina metastabilidad. Puede propagarse a través del sistema, causando un comportamiento impredecible. A menudo se utilizan circuitos de sincronización para mitigar este riesgo.

2. Desfase

El desfase de reloj ocurre cuando la señal de reloj llega a diferentes componentes en tiempos distintos. Esto puede reducir el margen de temporización efectivo. Un desfase positivo proporciona más tiempo de setup pero menos tiempo de hold. Un desfase negativo hace lo contrario.

3. Condiciones de carrera

Las condiciones de carrera ocurren cuando la salida depende de la secuencia de eventos. Si dos señales cambian simultáneamente, el orden de su procesamiento determina el estado final. Los diagramas de temporización ayudan a visualizar estas secuencias para prevenir las carreras.

Aplicación en arquitectura de computadoras 🖥️

Los diagramas de temporización no son solo herramientas teóricas. Se utilizan ampliamente en arquitecturas del mundo real.

Interfaces de memoria

La DRAM y la SRAM tienen requisitos estrictos de temporización. El controlador de memoria debe esperar retardos específicos antes de leer o escribir. Los diagramas de temporización definen las secuencias de la línea de comandos. Garantizan que la banca de memoria esté lista antes de acceder a los datos.

Protocolos de bus

Protocolos como I2C, SPI y UART dependen de la temporización para la comunicación. La línea de reloj en SPI sincroniza la transferencia de datos. En UART, la temporización se basa en las tasas de baudios. El receptor debe muestrear la línea de datos en el centro exacto del período del bit. Un diagrama de temporización muestra la alineación del bit de inicio, los bits de datos y el bit de parada.

Etapas de pipeline

Las CPUs modernas utilizan el pipeline para ejecutar múltiples instrucciones a la vez. Cada etapa debe completarse dentro de un ciclo de reloj. Los diagramas de temporización representan el flujo de datos a través de las etapas de fetch, decode, execute y write-back. Ayudan a identificar cuellos de botella donde una etapa espera a otra.

Mejores prácticas para la documentación 📝

Crear diagramas de temporización claros garantiza que otros ingenieros puedan entender tu diseño. Sigue estas pautas para una documentación efectiva.

- Utiliza escalas consistentes:Asegúrate de que el eje del tiempo sea uniforme en todo el documento.

- Etiqueta claramente:Nombra cada señal. Evita etiquetas genéricas como «Señal 1».

- Destaca las restricciones:Utiliza corchetes o regiones sombreadas para mostrar las ventanas de setup y hold.

- Agrupa señales relacionadas:Mantén las señales de control juntas y las señales de datos juntas.

- Incluye anotaciones:Agrega notas que expliquen transiciones complejas o comportamientos especiales.

Consideraciones avanzadas 🔬

A medida que los sistemas se vuelven más rápidos, el análisis de temporización se vuelve más complejo. Varios factores añaden capas de dificultad.

1. Ruido de la fuente de alimentación

Las fluctuaciones de voltaje pueden desplazar los niveles umbral de las puertas lógicas. Esto cambia efectivamente el retardo de propagación. Los diagramas de tiempo deben tener en cuenta los escenarios de voltaje más desfavorables.

2. Variaciones de temperatura

Los componentes electrónicos se comportan de manera diferente a diferentes temperaturas. Las altas temperaturas aumentan la resistencia y el retardo. Las bajas temperaturas pueden afectar la capacitancia. Los diseñadores deben verificar el tiempo de funcionamiento en todo el rango de temperatura de operación.

3. Integridad de la señal

Los trazos largos en una placa de circuito actúan como líneas de transmisión. Las reflexiones y el crosstalk pueden distorsionar las señales. Los diagramas de tiempo deben incluir diagramas de ojo o métricas de calidad de señal para enlaces de alta velocidad.

Conclusión sobre el análisis de tiempo 🎯

Los diagramas de tiempo son el mapa para navegar la lógica digital. Traducen estados binarios abstractos en eventos físicos de tiempo. Para un estudiante de ciencias de la computación, dominar la lectura y creación de estos diagramas es una competencia fundamental.

Al comprender los ciclos de reloj, los retardos de propagación y las restricciones de configuración, puedes diseñar sistemas robustos y eficientes. La capacidad de visualizar el flujo de señales evita errores costosos en el diseño de hardware. A medida que avanza la tecnología, los principios permanecen iguales. El tiempo es la variable constante.

Enfócate en los fundamentos. Practica la lectura de diagramas existentes. Dibuja los tuyos para cada nuevo circuito que construyas. Esta disciplina te servirá muy bien en tu carrera técnica.