Los sistemas digitales dependen de una sincronización precisa para funcionar correctamente. Sin un tiempo exacto, la corrupción de datos, los fallos del sistema y los fallos de seguridad se vuelven inevitables. Un diagrama de tiempo proporciona una representación visual de cómo cambian las señales con el tiempo, ofreciendo una visión clara de las relaciones entre los ciclos de reloj, la validez de los datos y las señales de control. Esta guía explora el papel crítico de los diagramas de tiempo en diversos sectores, detallando ejemplos prácticos y soluciones técnicas para desafíos comunes.

🔍 Comprendiendo los fundamentos

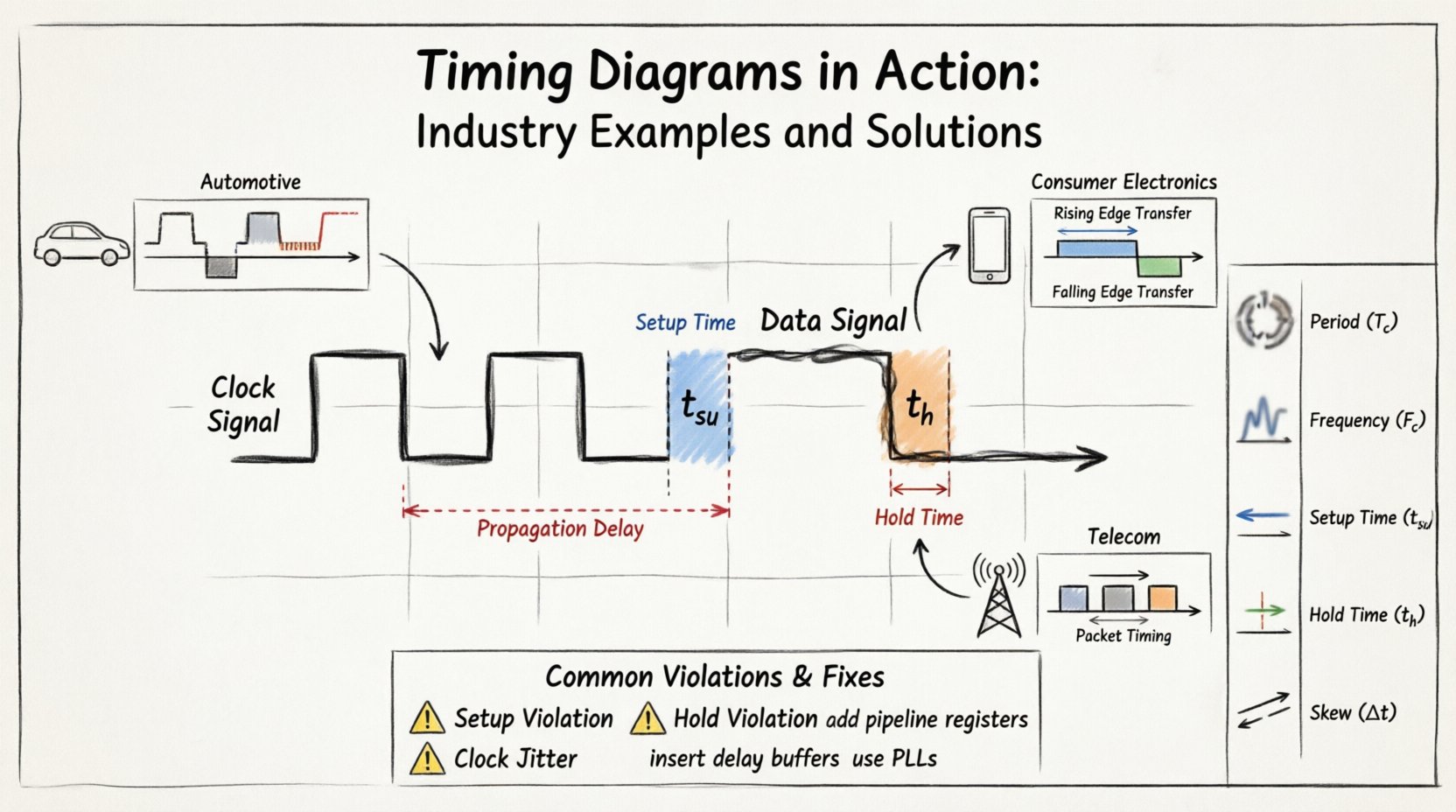

Antes de adentrarnos en aplicaciones específicas, es esencial comprender los componentes principales de un diagrama de tiempo. Estos diagramas representan el comportamiento de las señales respecto a un reloj de referencia. No son meros dibujos; son restricciones matemáticas que determinan el comportamiento del hardware.

- Bordes de señal: La transición de bajo a alto (borde ascendente) o de alto a bajo (borde descendente) desencadena cambios de estado en la lógica secuencial.

- Período del reloj: La duración entre dos bordes consecutivos del mismo polaridad define el tiempo disponible para que la lógica se estabilice.

- Retardo de propagación: El tiempo que tarda una señal en viajar desde un pin de entrada hasta un pin de salida a través de puertas lógicas.

- Tiempo de preparación y tiempo de retención: Restricciones críticas que garantizan que los datos estén estables antes y después del borde del reloj.

Cuando se violan estos parámetros, el circuito puede entrar en un estado metastable, lo que provoca un comportamiento impredecible. Los ingenieros utilizan diagramas de tiempo para verificar que la implementación física de un diseño cumpla con estos requisitos lógicos.

🚗 Electrónica automotriz: Tiempo crítico para la seguridad

La industria automotriz exige el más alto nivel de fiabilidad. Los vehículos contienen decenas de Unidades de Control Electrónicas (ECUs) que se comunican a través de buses como CAN (Red de Área de Control), LIN (Red de Interconexión Local) y FlexRay. El análisis de tiempo aquí no se trata solo de velocidad; se trata de determinismo y seguridad.

1. Arbitraje en el bus CAN

El bus CAN permite que múltiples nodos se comuniquen en un solo cable. El diagrama de tiempo para el arbitraje CAN revela cómo se determina la prioridad durante la contención del bus.

- Dominante frente a Receptivo: Los niveles lógicos se representan mediante estados de voltaje. Un bit dominante (0) anula a un bit receptivo (1).

- Sincronización: Los nodos se sincronizan con el bit de inicio de trama utilizando segmentos de sincronización.

- Punto de muestreo: Los datos se muestrean en un porcentaje específico del tiempo de bit para evitar el ruido.

Si el punto de muestreo está demasiado cerca del borde, el ruido puede causar errores de bit. Si es demasiado tarde, los datos pueden no estar estables. Los diagramas de tiempo ayudan a los ingenieros a establecer correctamente el punto de muestreo, típicamente alrededor del 80 % del tiempo de bit.

2. Muestreo de ADC en fusión de sensores

Los vehículos modernos utilizan múltiples sensores (radar, lidar, cámaras) para crear una percepción del entorno. Los convertidores analógico-digital (ADC) deben muestrear las señales a intervalos precisos para evitar el solapamiento.

- Jitter del reloj: Las variaciones en el tiempo del borde del reloj introducen ruido en la señal digitalizada.

- Latencia: El tiempo desde la entrada del sensor hasta la salida de datos procesados debe minimizarse para el control en tiempo real.

- Entrelazado:Varios ADCs suelen trabajar en paralelo. Los diagramas de tiempo aseguran que sus fases estén alineadas para evitar huecos en los datos.

📱 Electrónica de consumo: Interfaces de alta velocidad

Los dispositivos de consumo priorizan el rendimiento y la eficiencia energética. Las interfaces como la memoria DDR y los enlaces de visualización requieren ventanas de tiempo ajustadas para lograr un ancho de banda alto sin aumentar el consumo de energía.

1. Interfases de memoria DDR

La memoria de doble tasa de datos (DDR) transfiere datos en ambos bordes, ascendente y descendente, del reloj. Esto duplica la tasa de datos efectiva, pero reduce a la mitad la ventana de tiempo para la estabilidad de los datos.

| Parámetro | Definición | Impacto de la violación |

|---|---|---|

| Tiempo de preparación | Tiempo durante el cual los datos deben estar estables antes del borde del reloj | Transferencia de datos perdida, bloqueo del sistema |

| Tiempo de retención | Tiempo durante el cual los datos deben permanecer estables después del borde del reloj | Datos corruptos, cambios de bits |

| Atraso del reloj | Diferencia en el tiempo de llegada del reloj a diferentes chips | Margen de tiempo reducido, inestabilidad |

| Ciclo de trabajo | Relación entre el tiempo alto y el período total | Rendimiento desequilibrado, aumento de jitter |

En DDR4 y DDR5, el bus de comandos y direcciones suele funcionar a una frecuencia más baja que el bus de datos. Los diagramas de tiempo deben tener en cuenta las señales de pulso de sincronización de origen (DQS) que acompañan a los datos para indicar las ventanas válidas.

2. Interfaces de visualización (MIPI DSI)

Los dispositivos móviles utilizan la Interfaz Serial de Visualización MIPI (DSI) para conectar el procesador con la pantalla. Esta interfaz utiliza canales diferenciales de alta velocidad.

- Modo de comando de bajo consumo (LP):Modo de bajo consumo para enviar comandos, que depende de un tiempo estricto para las secuencias de activación.

- Modo de datos de alta velocidad (HS):Transmisión de alta velocidad en la que la recuperación del reloj se realiza a partir de la corriente de datos.

- Tiempo de giro:El tiempo necesario para cambiar del modo de transmisión al modo de recepción en el mismo canal.

La desalineación en estos diagramas de tiempo provoca artefactos en la pantalla, parpadeo o una pérdida total de la salida de vídeo.

📡 Telecomunicaciones: Latencia y ancho de banda

En telecomunicaciones, el tiempo es sinónimo de latencia. Los tiempos de entrega de paquetes y la sincronización en redes distribuidas son críticos para servicios como 5G y el comercio de alta frecuencia.

1. Señalización PCIe

El estándar Peripheral Component Interconnect Express (PCIe) se utiliza ampliamente para conectar componentes de alta velocidad. Utiliza canales en serie con relojes integrados o relojes de sincronización de origen.

- Ajuste de ecualización:La integridad de la señal se degrada con la distancia. Los diagramas de tiempo muestran cómo los filtros de ecualización compensan las pérdidas.

- Entrenamiento de enlace:Una secuencia de estados temporizados para establecer la velocidad del enlace y el ancho de canal.

- Control de flujo:Ventanas de tiempo para el control de flujo basado en créditos evita desbordamientos de búfer.

2. Físicas de Ethernet

Ethernet estándar depende de un reloj compartido o recuperación de reloj. Ethernet de Gigabit y superiores utilizan codificación 8b/10b para garantizar transiciones suficientes para la recuperación del reloj.

- Períodos de inactividad:Ventanas de tiempo definidas en las que no se envía datos para mantener la sincronización.

- Delimitador de inicio de trama:Un patrón específico de bits que marca el inicio de un paquete, requiriendo un tiempo de detección preciso.

- Espacio entre paquetes:Un retraso obligatorio entre paquetes para permitir que el hardware se reinicie.

⚠️ Violaciones de tiempo comunes y soluciones

Aunque se diseñe con cuidado, ocurren violaciones de tiempo. Identificar la causa raíz requiere analizar el diagrama de tiempo para ver dónde las señales se desvían de las expectativas.

1. Violaciones de tiempo de preparación

Ocurre cuando los datos llegan demasiado tarde para ser capturados por el borde del reloj.

- Causas:Profundidad excesiva de lógica, retrasos largos en los cables o desfase de reloj.

- Soluciones:

- Insertar registros de pipeline para romper caminos largos.

- Optimizar la síntesis de lógica para reducir el número de puertas.

- Ajustar la frecuencia del reloj para proporcionar más tiempo.

2. Violaciones de tiempo de retención

Ocurre cuando los datos cambian demasiado rápido después del borde del reloj, sobrescribiendo el valor capturado.

- Causas:Retardos en caminos cortos, desfase de reloj donde el reloj de captura llega demasiado tarde.

- Soluciones:

- Inserte buffers de retardo en la ruta de datos.

- Utilice técnicas de retemporización para equilibrar las rutas.

- Asegúrese de que la red de distribución de reloj tenga un desfase mínimo.

3. Desfase y jitter de reloj

El desfase es la diferencia en el tiempo de llegada de la señal de reloj en diferentes registros. El jitter es la variación a corto plazo del borde del reloj.

- Impacto:Reduce el margen de tiempo efectivo disponible para los datos.

- Soluciones:

- Utilice generadores de reloj de bajo jitter.

- Diseñe árboles de reloj equilibrados con trazados de longitud igual.

- Implemente lazos de enganche de fase (PLLs) para limpiar las señales de reloj.

✅ Mejores prácticas para la implementación

Lograr un tiempo de funcionamiento robusto requiere un enfoque sistemático durante todo el ciclo de vida del diseño. La documentación y la verificación son tan importantes como el circuito mismo.

1. Defina las restricciones de tiempo desde el inicio

No espere hasta la fase de implementación para definir los requisitos de tiempo. Documente las frecuencias de reloj, los retardos de entrada y los retardos de salida en la especificación del diseño. Esto asegura que todos los interesados entiendan los límites del sistema.

2. Utilice el análisis de tiempo estático

Las herramientas de análisis de tiempo estático (STA) calculan las rutas de retardo peor caso sin simular cada combinación de entrada. Este método es eficiente y cubre todos los estados posibles, asegurando que no se pierdan violaciones de tiempo.

3. Valide con simulación

Aunque STA es potente, la simulación dinámica proporciona una visión del comportamiento de las señales bajo condiciones específicas. Utilice la simulación para verificar rutas críticas, especialmente aquellas que involucran lógica asíncrona o máquinas de estado complejas.

4. Consideraciones de diseño físico

La disposición física del chip o placa afecta directamente el tiempo.

- Longitud de los cables:Los cables más largos introducen mayor capacitancia y resistencia, aumentando el retardo.

- Acoplamiento cruzado:Las señales vecinas pueden inducir ruido, causando transiciones falsas.

- Ruido de la fuente de alimentación:Las caídas de voltaje pueden ralentizar las velocidades de conmutación de las puertas.

🛠️ Solución de problemas en escenarios del mundo real

Cuando un sistema no cumple con los tiempos, es necesario un proceso estructurado de depuración. Los siguientes pasos describen un enfoque lógico para resolver problemas de temporización.

- Paso 1: Identifique la ruta.Localice la ruta específica de registro a registro que causa el fallo. Consulte el informe de temporización para el margen más negativo.

- Paso 2: Analice las formas de onda.Utilice un visualizador de diagramas de temporización para inspeccionar las transiciones reales de la señal. Compárelas con los valores esperados.

- Paso 3: Verifique el reloj.Verifique la calidad de la señal de reloj. Busque jitter, distorsión en el ciclo de trabajo o picos.

- Paso 4: Revise las restricciones.Asegúrese de que las restricciones en el archivo de diseño coincidan con la realidad física del hardware.

- Paso 5: Itere.Realice cambios en la lógica o en el diseño, y luego vuelva a ejecutar el análisis de temporización.

📊 Resumen de los parámetros de temporización

Para facilitar la consulta rápida, aquí tiene un resumen de los parámetros de temporización clave utilizados en diversas industrias.

| Parámetro | Símbolo | Unidad típica | Descripción |

|---|---|---|---|

| Período | Tc | ns | Tiempo entre bordes consecutivos del reloj |

| Frecuencia | Fc | Hz | Inversa del período |

| Tiempo de preparación | tsu | ns | Estabilidad de datos requerida antes del borde del reloj |

| Tiempo de retención | th | ns | Estabilidad de datos requerida después del borde del reloj |

| Retardo de propagación | tpd | ns | Tiempo que tarda la señal en atravesar la lógica |

| Desfase | Δt | ps | Diferencia de tiempo de llegada del reloj |

🔄 Gestión de diseños asíncronos

No todos los sistemas funcionan con un único reloj. Los diseños asíncronos implican datos que cruzan entre dominios de reloj diferentes. Esto introduce el riesgo de metastabilidad, donde un flip-flop entra en un estado indefinido.

- Cadenas de sincronización:Utilice un sincronizador de múltiples etapas (típicamente dos flip-flops) para permitir que la señal se estabilice antes de ser utilizada.

- Protocolos de intercambio de señales:Implemente mecanismos de solicitud-acknowledgment para asegurar que el receptor esté listo antes de enviar los datos.

- Búferes FIFO:Utilice estructuras de memoria primero en entrar, primero en salir para desacoplar las velocidades del productor y el consumidor.

Los diagramas de tiempo para diseños asíncronos muestran la relación entre los dos relojes independientes. La clave está en asegurar que la ruta de datos tenga suficiente tiempo para estabilizarse antes de que el reloj receptor la muestree.

🌟 Reflexiones finales

Los diagramas de tiempo son la columna vertebral de la verificación de sistemas digitales. Cerraran la brecha entre la lógica abstracta y la realidad física. Al comprender los matices del tiempo de preparación, el tiempo de retención, el desfase del reloj y el jitter, los ingenieros pueden diseñar sistemas que sean robustos, eficientes y confiables.

Ya sea en sistemas de seguridad automotriz, dispositivos para el consumidor o infraestructura de telecomunicaciones, los principios permanecen iguales. La precisión en el tiempo conduce a la precisión en el rendimiento. La supervisión continua y el cumplimiento de las mejores prácticas aseguran que los diseños permanezcan funcionales durante toda su vida útil. A medida que la tecnología avanza y las velocidades aumentan, la importancia del análisis detallado del tiempo solo crecerá.

Para los equipos que buscan mejorar la calidad de su diseño, invertir tiempo en diagramas de temporización precisos y flujos de verificación es esencial. Reduce el riesgo, disminuye los costos de depuración y garantiza que el producto final cumpla con sus especificaciones. Con las herramientas y metodologías adecuadas, los desafíos de temporización se convierten en restricciones manejables en lugar de obstáculos.