Los sistemas digitales dependen de una sincronización precisa para funcionar correctamente. Cuando las señales llegan en el momento incorrecto, ocurren fallas lógicas, lo que conduce a un comportamiento impredecible. Comprender cómo analizar y corregir estos problemas es esencial para cualquier persona que estudie lógica digital, ingeniería de computadoras o electrónica. Esta guía cubre los conceptos fundamentales y los pasos prácticos para identificar y resolver los problemas de sincronización encontrados en circuitos secuenciales y en la transmisión de datos.

Comprendiendo las señales de reloj y sus bordes ⏱️

En el corazón de la mayoría de los diseños digitales se encuentra la señal de reloj. Esta onda periódica determina cuándo se muestrea la data y cuándo ocurren los cambios de estado. La solución de problemas a menudo comienza con la verificación de la integridad de esta señal fundamental.

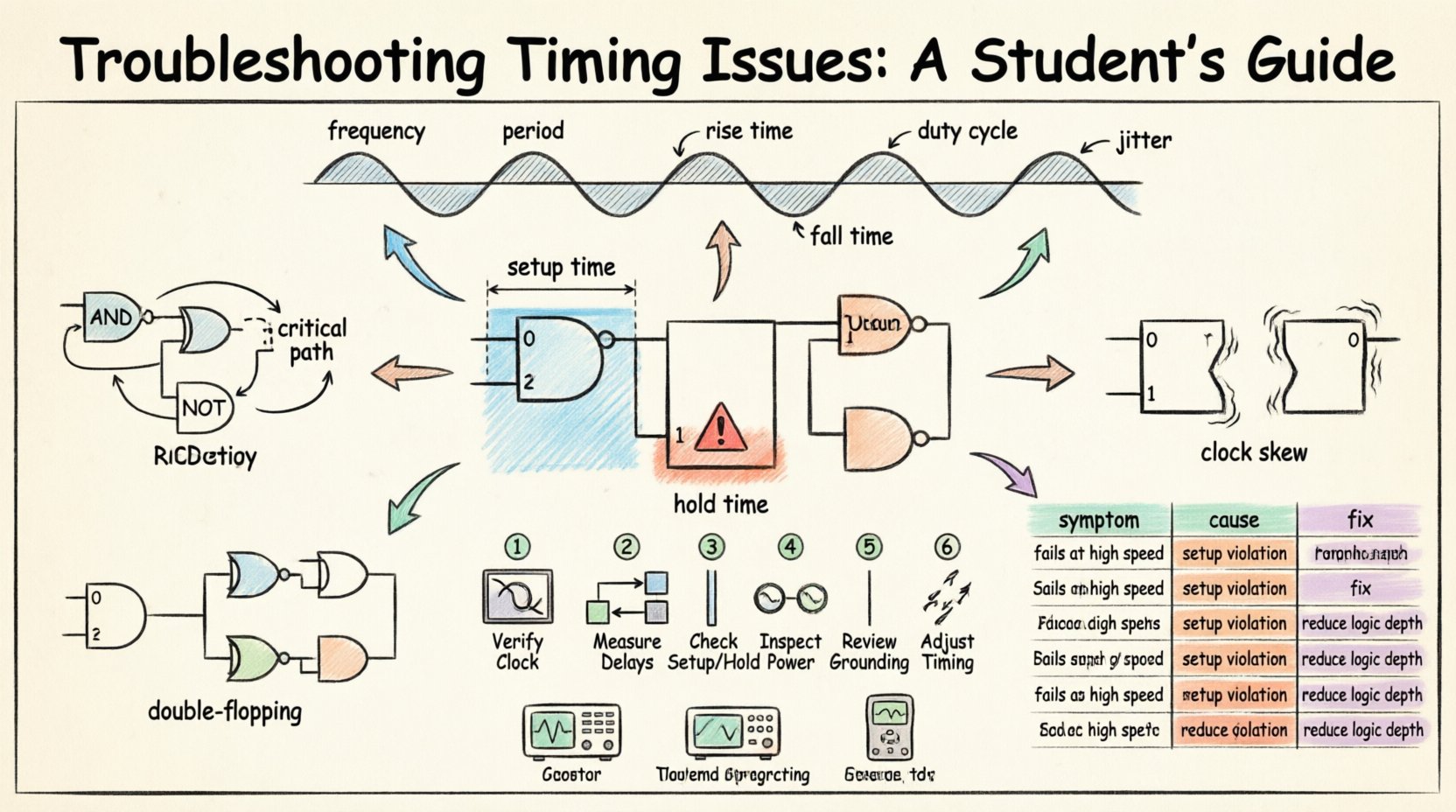

- Frecuencia y período: La frecuencia del reloj determina la velocidad de operación. El período es la duración del tiempo de un ciclo completo. Si el circuito requiere un reloj de 100 MHz, el período es de 10 nanosegundos. Cualquier desviación aquí afecta a toda la lógica posterior.

- Tiempo de subida y bajada: Una onda cuadrada perfecta es teórica. Las señales reales tienen tiempos de subida y bajada finitos. Si la transición es demasiado lenta, la señal puede pasar demasiado tiempo en la región de voltaje indefinida, causando múltiples conmutaciones o errores lógicos.

- Ciclo de trabajo: Este es la relación entre el tiempo que la señal está alta respecto al período total. Un ciclo de trabajo del 50% es el estándar, pero algunos diseños requieren ciclos asimétricos. Las desviaciones pueden distorsionar los márgenes de tiempo para los requisitos de establecimiento o retención.

Al inspeccionar un circuito, utilice un osciloscopio o un analizador lógico para observar la forma de onda del reloj. Busque picos de ruido, sobrepasamientos o jitter excesivo. El jitter se refiere a la desviación del borde del reloj respecto a su posición ideal en el tiempo. Un jitter alto reduce el margen de tiempo efectivo disponible para que la data se establezca.

Violaciones de tiempo de establecimiento y retención ⚠️

Estas son las violaciones de tiempo más comunes encontradas en el diseño de lógica secuencial. Los flip-flops y los latch tienen requisitos específicos sobre cuándo la data debe estar estable respecto al borde del reloj.

Tiempo de establecimiento

El tiempo de establecimiento es la cantidad mínima de tiempo antes del borde del reloj en que la data debe estar estable. Si la data cambia demasiado cerca del borde del reloj, el flip-flop puede no capturar el valor correcto.

- La restricción: El retardo de propagación de la lógica combinacional que alimenta el flip-flop debe ser menor que el período del reloj menos el tiempo de establecimiento.

- El síntoma: El sistema podría funcionar a frecuencias más bajas, pero fallar cuando aumenta la velocidad. A menudo ocurren errores aleatorios de bits en la salida.

- La solución: Reduzca la profundidad de la lógica entre registros, aumente el período del reloj o utilice componentes más rápidos.

Tiempo de retención

El tiempo de retención es la cantidad mínima de tiempo después del borde del reloj en que la data debe permanecer estable. Si la data cambia demasiado pronto después del borde del reloj, el flip-flop puede perder el valor capturado.

- La restricción: El retardo de propagación de la lógica combinacional debe ser mayor que el tiempo de retención del flip-flop de destino.

- El síntoma: Las violaciones de retención a menudo ocurren independientemente de la frecuencia. Esto se debe a que el retardo es absoluto, no relativo al período.

- La solución: Agregue buffers de retardo en la ruta de datos para ralentizar la señal, o rediseñe la lógica para reducir el retardo.

Es crucial distinguir entre estos dos. Las violaciones de establecimiento dependen de la frecuencia, mientras que las violaciones de retención dependen de la ruta. Un error común es intentar corregir una violación de retención ralentizando el reloj; esto no funcionará y podría empeorar la situación.

Retardos de propagación y análisis de ruta 📉

Las señales no viajan instantáneamente. Cada cable, compuerta y componente introduce un retardo. Analizar estos retardos es fundamental para garantizar que los datos lleguen a tiempo.

- Retardo de lógica combinacional: Este es el tiempo que tarda una señal en pasar por compuertas como AND, OR y NOT. Las cadenas largas de compuertas generan una latencia significativa.

- Retardo de interconexión: En una placa física, los cables tienen capacitancia y resistencia. Las trazas más largas introducen más retardo. Esto a menudo se modela como una red RC.

- Retardo de pin a pin: El tiempo desde una entrada de reloj hasta una salida de datos en un componente. Esto generalmente se especifica en las hojas de datos.

Al depurar, traza la ruta crítica. Esta es la ruta con mayor retardo entre dos elementos secuenciales. Si la ruta crítica excede el período del reloj, el diseño fallará. Para encontrarla, calcula la suma de los retardos de todas las rutas posibles e identifica el máximo.

Desviación de reloj y jitter 📶

Incluso si la fuente de reloj es perfecta, la señal podría llegar a diferentes componentes en tiempos distintos. Este fenómeno se conoce como desviación.

- Desviación de reloj: Esto ocurre cuando la señal de reloj recorre distancias diferentes para llegar a diferentes flip-flops. La desviación positiva retrasa el reloj de captura, aliviando el tiempo de setup pero estrechando el tiempo de hold. La desviación negativa estrecha el tiempo de setup pero alivia el tiempo de hold.

- Jitter de reloj: Variaciones a corto plazo en el tiempo de borde del reloj. El jitter reduce el presupuesto de tiempo disponible para la configuración de datos.

- Deriva: Cambios lentos en la frecuencia del reloj con el tiempo debido a fluctuaciones de temperatura o alimentación.

La desviación a menudo se gestiona mediante la síntesis del árbol de reloj en diseños complejos. En proyectos estudiantiles, generalmente se minimiza ruteando las trazas de reloj de forma equilibrada y manteniéndolas cortas. Si se sospecha de desviación, mida el reloj en múltiples puntos del circuito simultáneamente.

Metastabilidad e entradas asíncronas 🌀

Cuando los datos cambian al mismo tiempo que el borde del reloj, un flip-flop entra en un estado metastable. No se establece inmediatamente en 0 o 1, sino que permanece en un nivel de voltaje intermedio.

- El riesgo:La metastabilidad puede propagarse a través del sistema, causando errores lógicos que son difíciles de reproducir.

- Señales asíncronas:Las entradas de interruptores externos o puertos de comunicación a menudo no se alinean con el reloj interno. Estas deben ser sincronizadas.

- Doble flip-flop:Una técnica común para resolver la metastabilidad es pasar la señal a través de dos flip-flops en serie. El primero captura el estado metastable, y el segundo lo resuelve durante el siguiente ciclo.

Trate siempre las entradas asíncronas como posibles fuentes de metastabilidad. No las conecte directamente a lógica que requiera un tiempo estricto. Utilice circuitos de sincronización para garantizar una transferencia segura de datos entre dominios de reloj diferentes.

Una metodología paso a paso para la depuración 🛠️

Cuando surge un problema de temporización, siga un enfoque estructurado para aislar la causa. Cambios aleatorios tienen pocas probabilidades de dar resultados.

- Verifique el reloj: Verifique la frecuencia, el ciclo de trabajo y la amplitud. Asegúrese de que la señal sea estable y limpia.

- Mida los retardos:Utilice un analizador lógico para capturar las formas de onda de entrada y salida. Mida el retardo de propagación real de la ruta.

- Verifique el tiempo de establecimiento y retención:Calcule si la ruta cumple con las restricciones de tiempo de establecimiento y retención basándose en los retardos medidos.

- Inspeccione la alimentación:Las caídas de voltaje pueden ralentizar las puertas. Asegúrese de que la fuente de alimentación sea estable y proporcione corriente suficiente.

- Revise la conexión a tierra:Una mala conexión a tierra puede introducir ruido que simula errores de temporización. Verifique la presencia de bucles de tierra y caminos de retorno compartidos.

- Ajuste el tiempo:Si el diseño es flexible, ajuste la frecuencia del reloj o agregue búferes para equilibrar la ruta.

La documentación es clave durante este proceso. Registre las formas de onda y las mediciones. Estos datos ayudan a comparar el comportamiento esperado con el rendimiento real.

Tabla de referencia de errores comunes 📊

Utilice esta tabla como referencia rápida para diagnosticar síntomas específicos.

| Síntoma observado | Causa probable | Acción recomendada |

|---|---|---|

| El sistema falla a alta velocidad | Violación del tiempo de establecimiento | Reduzca la profundidad lógica o aumente el período del reloj |

| El sistema falla a baja velocidad | Violación del tiempo de retención | Agregue búferes de retardo a la ruta de datos |

| Cambios aleatorios de bits | Ruido de señal o jitter | Verifique el blindaje y la estabilidad de la fuente de alimentación |

| La salida se queda colgada o se reinicia | Metastabilidad | Implemente cadenas de sincronización |

| Comportamiento inconsistente | Atraso del reloj | Equilibrar las longitudes de las trazas del reloj |

| Ninguna salida en absoluto | El reloj no está habilitado | Verifique la distribución del reloj y las señales de habilitación |

Herramientas e instrumentación 📏

Aunque las herramientas de simulación son útiles, la verificación física a menudo requiere hardware específico. Comprender cómo usar correctamente estos instrumentos forma parte del conjunto de habilidades de resolución de problemas.

- Osciloscopio:Esencial para ver los niveles de voltaje y la forma de la señal. Use sondas de alta impedancia para evitar cargar el circuito.

- Analizador lógico:Más adecuado para señales digitales. Captura el estado lógico (0 o 1) con el tiempo. Puede dispararse con patrones específicos para aislar errores.

- Contador de frecuencia:Utilizado para verificar la frecuencia exacta de la fuente de reloj si no hay disponible un osciloscopio.

Asegúrese de que las sondas estén correctamente compensadas. Una sonda no compensada puede distorsionar la forma de la señal, lo que lleva a conclusiones erróneas sobre los tiempos de subida y los retrasos.

Consideraciones finales sobre la integridad de la señal 🔒

Los problemas de temporización a menudo son síntomas de problemas más amplios de integridad de la señal. A medida que los circuitos se vuelven más rápidos, las propiedades físicas de la placa son más importantes.

- Crosstalk:Las señales en cables adyacentes pueden interferirse entre sí. Mantenga separadas las líneas de alta velocidad de las líneas sensibles.

- Ajuste de impedancia:Si la impedancia de la traza no coincide con la del conductor o el receptor, se producen reflexiones. Estas reflexiones pueden parecer retrasos de temporización.

- Efectos térmicos:A medida que los componentes se calientan, sus características eléctricas cambian. Esto puede alterar los tiempos de propagación y provocar fallas de temporización bajo carga.

Diseñar para la temporización requiere una visión integral. No se trata solo de puertas lógicas; se trata del medio físico a través del cual viajan las señales. Al adherirse a estos principios, los estudiantes pueden construir sistemas robustos que funcionen de forma confiable bajo diversas condiciones.

La práctica regular con hardware real ayuda a internalizar estos conceptos. La teoría proporciona el marco, pero la depuración práctica desarrolla la intuición necesaria para resolver eficientemente problemas complejos de temporización.