Dans le monde complexe de l’électronique numérique et de la conception de systèmes, la communication entre les composants repose fortement sur des relations temporelles précises. Un diagramme de temporisation sert de langage visuel pour décrire ces relations. Il s’agit d’une représentation graphique qui montre comment les signaux évoluent dans le temps. Sans cet outil, le débogage des interactions matérielles ou la vérification du comportement logique serait presque impossible. Ce guide explore les éléments essentiels, les paramètres et les stratégies de lecture nécessaires pour interpréter efficacement ces diagrammes.

Qu’est-ce qu’un diagramme de temporisation ? 📐

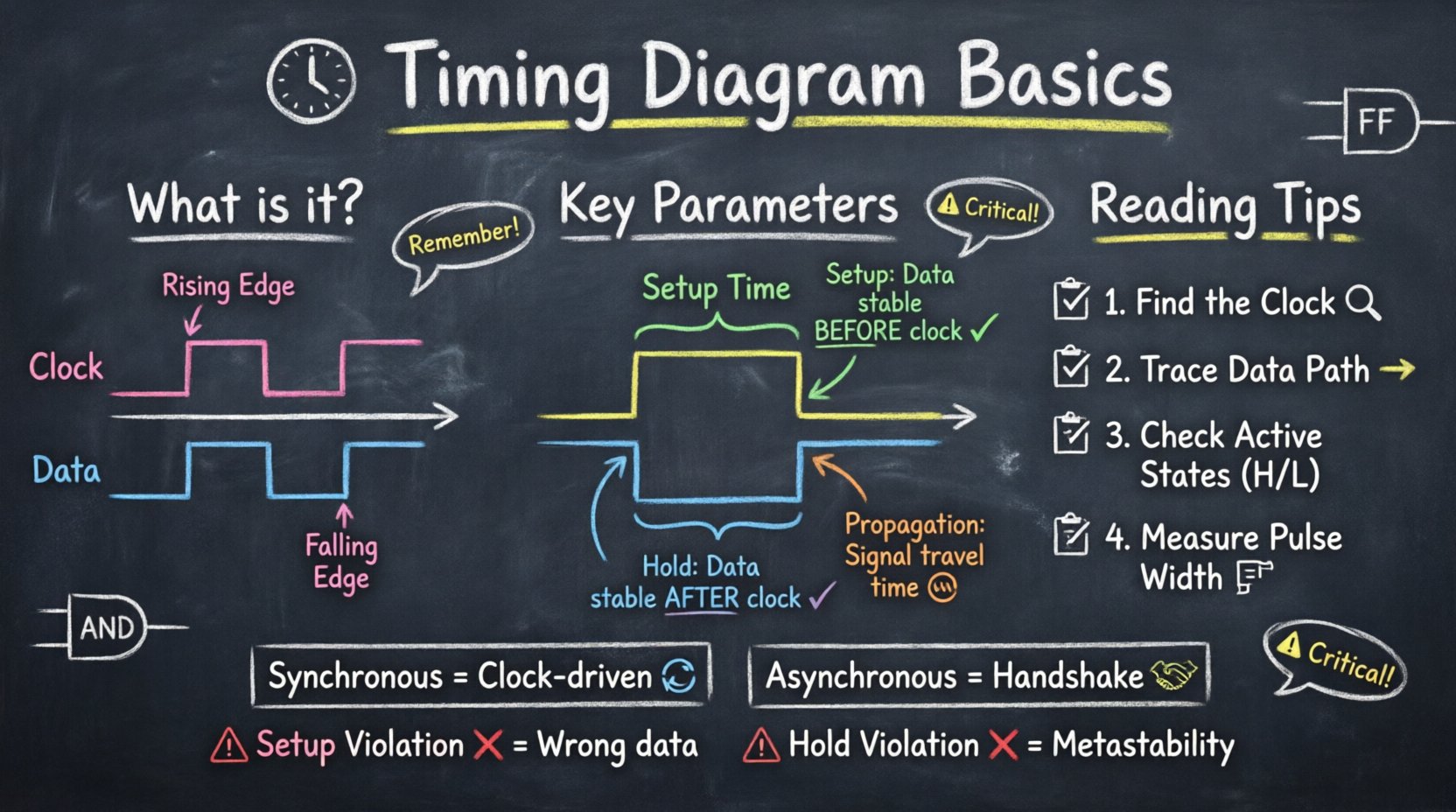

Un diagramme de temporisation est un type spécifique de graphique utilisé pour illustrer la relation entre deux ou plusieurs signaux sur une période définie. Contrairement à un tableau d’états logiques, qui liste les états dans une grille, un diagramme de temporisation représente ces états sur un axe horizontal du temps. Cette approche visuelle permet aux ingénieurs de voir la séquence des événements, la durée des impulsions et la synchronisation entre différentes parties d’un circuit.

Ces diagrammes sont essentiels dans plusieurs contextes :

- Conception matérielle : Vérifier que les données sont stables avant l’arrivée d’une frontière d’horloge.

- Analyse de protocole : Comprendre les normes de communication telles que I²C, SPI ou UART.

- Vérification du système : S’assurer que les machines d’état passent correctement d’un état à un autre sans conditions de course.

- Débogage : Identifier les violations de setup ou de hold qui provoquent des défaillances du système.

En visualisant le temporisation, les concepteurs peuvent prédire le comportement d’un système sous charge, garantissant fiabilité et performance.

Éléments fondamentaux d’un diagramme de temporisation 🎯

Pour lire un diagramme de temporisation, il faut d’abord comprendre ses éléments de base. Chaque diagramme se compose de signaux, de temps et de transitions. Le disposition de ces éléments raconte une histoire sur le comportement électrique du système.

Signaux et lignes

Chaque ligne horizontale représente un signal spécifique. Il peut s’agir d’un signal d’horloge, d’une ligne de données, d’un bus d’adresses ou d’un drapeau de contrôle. Les signaux sont généralement étiquetés au début de la ligne ou dans une légende. La position verticale de la ligne ne représente pas les niveaux de tension ; plutôt, la position verticale par rapport à la ligne de référence indique les états logiques.

L’axe du temps

L’axe horizontal représente le temps. Il s’écoule de gauche à droite. Dans de nombreux diagrammes, les intervalles de temps sont marqués par des lignes pointillées verticales. Ces repères correspondent souvent aux cycles d’horloge. Il est important de noter que l’échelle du temps n’est pas toujours linéaire. Parfois, des moments précis sont agrandis pour montrer des détails en microseconde ou en nanoseconde, tandis que d’autres parties montrent un comportement à grande échelle.

Niveaux logiques

Les signaux basculent généralement entre deux états : Haut et Bas. Ces états correspondent respectivement au binaire 1 et 0. Dans certains contextes, le niveau Bas peut représenter un état actif (actif bas), tandis que le niveau Haut représente l’état actif (actif haut). Comprendre l’état actif est crucial pour interpréter les signaux de contrôle tels que Reset ou Chip Select.

Transitions et fronts

Les lignes verticales reliant les niveaux logiques représentent des transitions. Il existe deux types principaux de fronts :

- Front montant : Une transition du Bas au Haut.

- Front descendant : Une transition du Haut au Bas.

Ces fronts déclenchent souvent des actions dans les circuits numériques. Par exemple, un registre peut mettre à jour ses données précisément au moment où le signal d’horloge monte.

Paramètres de temporisation critiques ⚙️

Comprendre les lignes statiques n’est que la moitié de la bataille. Les paramètres dynamiques définissent les contraintes dans lesquelles le système doit fonctionner. Violation de ces paramètres entraîne une corruption des données ou des plantages du système.

Temps de préparation

Le temps de préparation est la durée minimale avant une transition d’horloge pendant laquelle un signal de données doit être stable et valide. Si les données changent trop près de la transition d’horloge, le circuit récepteur ne dispose peut-être pas de temps suffisant pour enregistrer correctement la valeur. Ce paramètre est strictement appliqué dans les systèmes synchrones.

Temps de maintien

Le temps de maintien est la durée minimale après une transition d’horloge pendant laquelle le signal de données doit rester stable. Même après que l’horloge a déclenché la capture, les données ne peuvent pas changer immédiatement. Si elles changent trop rapidement, le verrou interne ou la bascule pourrait entrer dans un état instable.

Retard de propagation

Le retard de propagation est le temps nécessaire à un signal pour voyager depuis l’entrée d’un composant jusqu’à sa sortie. Cela découle des propriétés physiques du circuit. Lorsque plusieurs composants sont en cascade, ces retards s’accumulent, ce qui affecte la fréquence maximale de fonctionnement du système.

Cycle d’horloge et fréquence

Le cycle d’horloge est la durée d’une période complète du signal d’horloge. La fréquence est l’inverse de cette période, mesurée en hertz (Hz). Le budget de temporisation d’un système est souvent défini par la période d’horloge. Si la somme de tous les retards de propagation dépasse la période d’horloge, le système ne fonctionnera pas correctement.

| Paramètre | Définition | Conséquence de la violation |

|---|---|---|

| Temps de préparation | Temps pendant lequel les données doivent être stables avant la transition d’horloge | Données manquantes ou capture incorrecte |

| Temps de maintien | Temps pendant lequel les données doivent être stables après la transition d’horloge | Métastabilité ou corruption des données |

| Retard de propagation | Temps nécessaire au signal pour traverser la logique | Fréquence maximale réduite ou erreur de temporisation |

| Désynchronisation | Différence de temps d’arrivée du signal d’horloge | Marge de temporisation réduite |

| Jitter | Variations à court terme du timing du signal | Fonctionnement instable à haute vitesse |

Lecture et analyse des signaux 📖

Interpréter un diagramme de temporisation nécessite une approche systématique. Se précipiter sur les informations visuelles peut entraîner une mauvaise interprétation du comportement du système. Suivez ces étapes pour analyser un diagramme avec précision.

- Identifiez l’horloge : Localisez le signal périodique qui commande le système. Il sert généralement de référence pour toutes les autres actions.

- Suivez le chemin des données : Suivez les lignes de signal depuis la source jusqu’à la destination. Notez où les données sont générées et où elles sont consommées.

- Vérifiez les états actifs : Déterminez si les signaux sont actifs à haut ou à bas niveau. Un signal bas peut signifier « Activer », tandis qu’un signal haut peut signifier « Désactiver ».

- Mesurez les durées : Examinez la largeur des impulsions. L’impulsion est-elle assez large pour être détectée ? Est-elle trop étroite pour être un bogue ?

- Vérifiez les séquences : Assurez-vous que les signaux de contrôle changent dans le bon ordre. Par exemple, un signal de réinitialisation doit être activé avant que le système ne commence à traiter.

Lors de l’analyse de diagrammes complexes, il est utile de diviser le chronogramme en cycles discrets. Analysez une période d’horloge à la fois pour comprendre les transitions d’état.

Systèmes synchrones vs. asynchrones 🔄

Les diagrammes temporels diffèrent considérablement selon que le système est synchrone ou asynchrone. Comprendre cette distinction est essentiel pour une interprétation correcte.

Systèmes synchrones

Dans un système synchrone, toutes les opérations sont synchronisées par une horloge globale. Chaque changement d’état se produit par rapport à une transition d’horloge. Cela rend l’analyse du temps plus prévisible. Vous pouvez calculer la vitesse maximale du système en additionnant les délais du chemin le plus long entre deux registres. Les diagrammes temporels sont ici très réguliers, les événements s’alignant verticalement avec les transitions d’horloge.

Systèmes asynchrones

Les systèmes asynchrones ne dépendent pas d’une horloge globale. Ils utilisent plutôt des protocoles d’échange de mains où les signaux changent d’état en fonction de la disponibilité de l’étape précédente. Les diagrammes temporels de ces systèmes apparaissent moins réguliers. Les événements sont déclenchés par des transitions spécifiques de signaux plutôt que par une impulsion périodique. L’analyse de ces systèmes exige une attention particulière aux dépendances entre les signaux.

Problèmes et violations courants de temporisation ⚠️

Même avec une conception soigneuse, des problèmes de temporisation peuvent survenir. Ces problèmes se manifestent souvent par des défaillances intermittentes difficiles à reproduire. Les reconnaître dans un diagramme temporel est une compétence clé pour le dépannage.

Violations de préparation

Une violation de préparation se produit lorsque les données arrivent trop tard par rapport à l’arête d’horloge. Visuellement, cela apparaît comme une transition de données qui se produit après que l’arête d’horloge a déjà passé. Le résultat est souvent que le composant récepteur capte une valeur incorrecte ou la valeur précédente.

Violations de maintien

Une violation de maintien se produit lorsque les données changent trop tôt après l’arête d’horloge. Cela signifie que les nouvelles données écrasent les anciennes avant que le composant n’ait terminé de les capturer. Cela est particulièrement dangereux car cela peut entraîner une métastabilité, où la tension de sortie flotte entre les niveaux haut et bas.

Désynchronisation et jitter

La désynchronisation d’horloge se produit lorsque le signal d’horloge arrive à différents composants à des moments différents. Si la désynchronisation est trop importante, la fenêtre de temps effective pour la préparation et le maintien est réduite. Le jitter désigne l’instabilité du timing des arêtes d’horloge. Un jitter élevé rend difficile la garantie des marges de temps, ce qui nécessite des vitesses d’horloge plus lentes.

Meilleures pratiques pour l’intégrité du signal 🛡️

Pour assurer des performances robustes, les ingénieurs doivent respecter les meilleures pratiques lors de la conception et de l’analyse du temps. Ces directives aident à minimiser les risques et à améliorer la stabilité du système.

- Minimisez les longueurs des pistes : Les pistes plus longues augmentent le délai de propagation et la sensibilité au bruit. Maintenez les chemins de signal aussi courts que possible.

- Corrélez les impédances : Assurez-vous que l’impédance de la ligne de transmission correspond à celle du conducteur et du récepteur pour éviter les réflexions.

- Utilisez des plans de masse :Un plan de masse solide fournit un chemin de retour à faible impédance, réduisant le bruit et les interférences.

- Tenez compte de la température :Les composants électroniques se comportent différemment à différentes températures. Les marges de conception doivent tenir compte des conditions thermiques les plus défavorables.

- Simulez tôt :Utilisez des outils de simulation pour modéliser le comportement temporel avant la fabrication de prototypes physiques. Cela permet de détecter les violations dès les premières étapes du cycle de conception.

Application au débogage matériel 🔍

Les diagrammes temporels ne servent pas seulement à la conception ; ce sont des outils essentiels pour le débogage. Lorsqu’un système échoue, les ingénieurs utilisent des oscilloscopes ou des analyseurs logiques pour capturer les formes d’onde réelles des signaux. Ces traces capturées sont ensuite comparées au diagramme temporel attendu.

Si la forme d’onde réelle s’écarte du diagramme, cette différence indique la cause racine. Par exemple, si une ligne de données est bruitée pendant la fenêtre de capture, cela indique un problème d’alimentation ou une interférence électromagnétique. Si le front de l’horloge est incliné au lieu d’être net, cela suggère un problème de puissance du conducteur.

En corrélant les données visuelles de l’oscilloscope avec les exigences logiques du diagramme temporel, les ingénieurs peuvent localiser les défauts avec précision. Ce processus transforme les contraintes temporelles abstraites en preuves physiques concrètes.

Résumé des concepts clés 💡

Maîtriser les bases des diagrammes temporels est fondamental pour travailler avec les systèmes numériques. Cela implique de comprendre la relation entre les signaux, le temps et les états logiques. En portant une attention particulière aux paramètres tels que le temps de préparation, le temps de maintien et le délai de propagation, les concepteurs peuvent créer des systèmes qui fonctionnent de manière fiable à haute vitesse.

La capacité à lire et interpréter ces diagrammes permet une communication efficace entre les équipes matérielles et logicielles. Elle comble l’écart entre la logique théorique et la réalité physique. Que vous conceviez un circuit de contrôle simple ou un microprocesseur complexe, l’analyse temporelle reste un pilier du succès ingénierie.

N’oubliez jamais de vérifier vos états actifs, de respecter les limites de l’horloge et de tenir compte des contraintes physiques. Avec de la pratique, l’interprétation de ces représentations visuelles devient naturelle, vous permettant de diagnostiquer les problèmes et d’optimiser les performances avec confiance.