Dans le monde de l’électronique numérique et de la conception de systèmes, le temps n’est pas seulement une dimension ; c’est un paramètre critique qui détermine si un circuit fonctionne correctement ou échoue de manière catastrophique.Les diagrammes de temporisationservent de langage visuel que les ingénieurs utilisent pour communiquer le comportement des signaux au fil du temps. Que vous conceviez une interface de microcontrôleur, débogiez un bus mémoire ou analysiez une transmission de données à haute vitesse, comprendre ces diagrammes est indispensable.

Ce guide explore les mécanismes des diagrammes de temporisation, en décomposant les comportements complexes des signaux en éléments compréhensibles. Nous passerons des définitions fondamentales aux techniques avancées d’analyse, afin de vous fournir les outils nécessaires pour interpréter les formes d’onde avec précision.

🔍 Qu’est-ce qu’un diagramme de temporisation ?

Un diagramme de temporisation est une représentation graphique de la séquence des changements de signal dans un système numérique. Contrairement à un schéma, qui montre comment les composants sont connectés, un diagramme de temporisation illustrequandces connexions changent d’état. Il cartographie l’activité des signaux le long d’un axe horizontal du temps, permettant aux concepteurs de vérifier que les données sont stables avant une transition d’horloge ou que les signaux de contrôle sont activés au moment approprié.

Ces diagrammes sont essentiels pour :

- Vérifier les interactions entre matériel et logiciel.

- Déboguer les protocoles de communication.

- Assurer que les exigences de temps de préparation et de maintien sont respectées.

- Documenter le comportement du système pour une maintenance future.

Sans une compréhension claire du temporisation, même un circuit logiquement correct peut échouer en raison de courses de signaux ou de métastabilité.

🛠️ Composants fondamentaux d’un diagramme de temporisation

Pour lire efficacement un diagramme de temporisation, vous devez identifier ses blocs de construction fondamentaux. Chaque élément porte des informations spécifiques concernant l’état et le flux du système numérique.

1. L’axe du temps

La ligne horizontale représente l’évolution du temps. Elle s’écoule généralement de gauche à droite. Dans les documents techniques détaillés, cet axe peut être marqué avec des unités de temps spécifiques (nanosecondes, picosecondes) ou des cycles d’horloge.

2. Les lignes de signal

Les lignes verticales représentent des signaux individuels, tels que les lignes d’horloge, les bus de données ou les lignes de contrôle (comme la sélection de puce ou lecture/écriture). Chaque ligne correspond à un nœud spécifique du circuit.

3. Niveaux logiques

Les signaux existent généralement dans l’un des deux états suivants :

- Haut (Logique 1 / VCC) :Souvent représenté par une ligne en haut de la piste du signal.

- Bas (Logique 0 / Masse) :Représenté par une ligne en bas de la piste du signal.

Certains systèmes utilisentlogique active basselogique, où le signal effectue sa fonction lorsque la tension est basse. Dans les diagrammes, cela est souvent indiqué par un cercle à l’identifiant du signal ou par une notation spécifique.

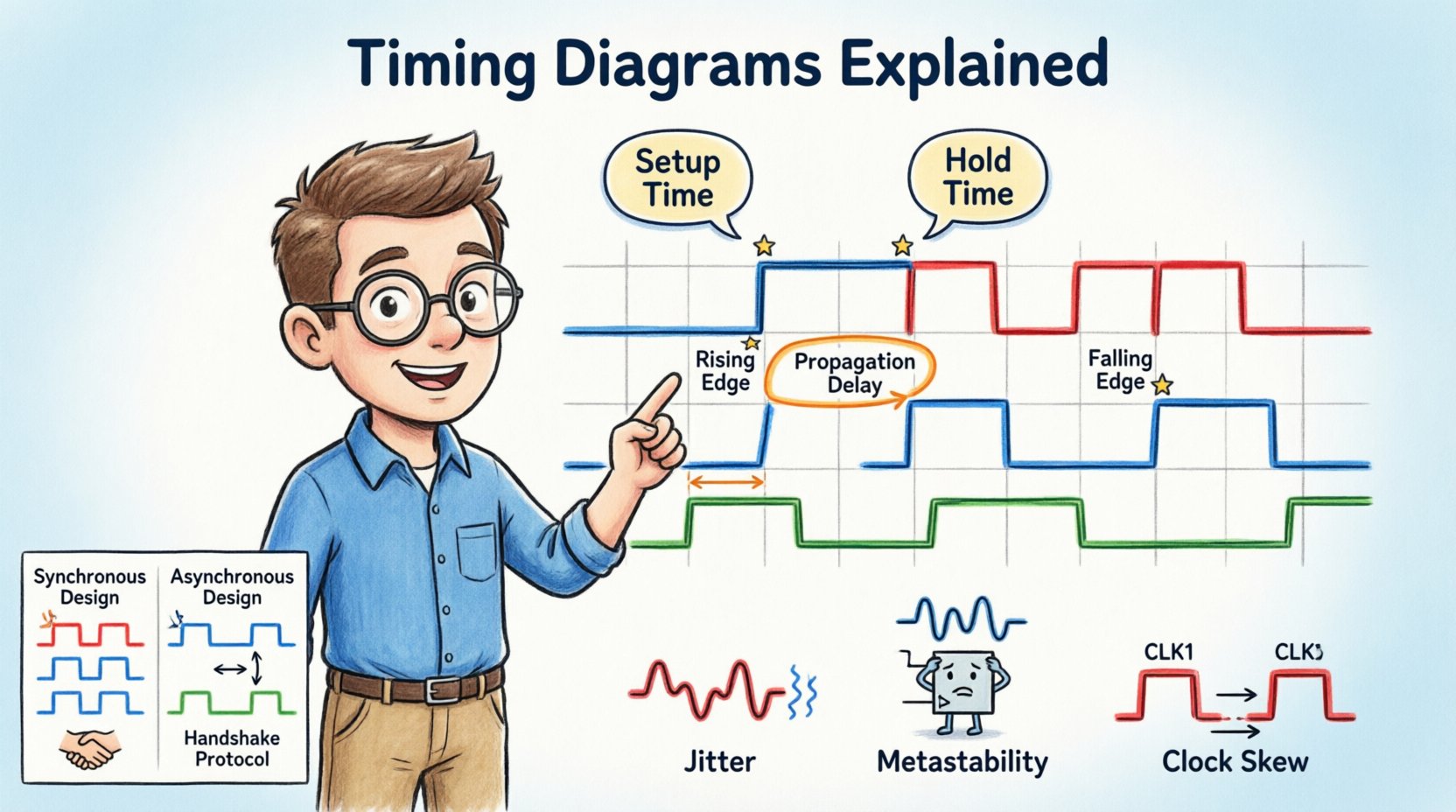

4. Transitions

Les transitions sont les moments où un signal passe de Haut à Bas ou de Bas à Haut.

- Front montant : Transition de Bas à Haut. Essentiel pour déclencher des événements.

- Front descendant : Transition de Haut à Bas. Utilisé pour des séquences de contrôle spécifiques.

- Déclenché par front : Le signal n’est évalué que pendant la transition, et non pendant l’état stable.

⚙️ Paramètres clés de temporisation

Une conception numérique précise repose sur la quantification de la relation entre les signaux. Les paramètres suivants constituent la base de l’analyse de temporisation.

1. Retard de propagation (tpd)

Il s’agit du temps nécessaire à un signal pour passer de l’entrée d’une porte logique ou d’un composant à sa sortie. Aucun signal ne change instantanément ; les limitations physiques entraînent un retard.

- Importance : Si le retard est trop long, la logique suivante peut recevoir les données trop tard, ce qui provoque des erreurs.

- Mesure : Mesuré à partir du point de tension à 50 % de la transition d’entrée jusqu’au point de tension à 50 % de la transition de sortie.

2. Temps de préparation (tsu)

Le temps de préparation est la durée minimale pendant laquelle les signaux de données doivent être stablesavantl’arrivée d’un front d’horloge.

- Scénario : Si un bascule nécessite que les données soient prêtes 5 nanosecondes avant que l’horloge ne déclenche, c’est le temps de préparation.

- Violation : Si les données changent trop près du front d’horloge, le système ne peut pas capturer correctement la valeur.

3. Temps de maintien (th)

Le temps de maintien est la durée minimale pendant laquelle les signaux de données doivent rester stablesaprèsl’arrivée d’une transition d’horloge.

- Scénario :Le bascule doit « voir » les données pendant une courte période après le déclenchement pour les verrouiller de manière sécurisée.

- Violation :Si les données changent immédiatement après l’arête d’horloge, l’entrée peut ne pas être correctement verrouillée.

4. Désynchronisation d’horloge

La désynchronisation d’horloge se produit lorsque le signal d’horloge arrive à différents composants à des moments différents. Cela est souvent dû aux différences de longueur de tracé sur une carte PCB.

- Désynchronisation positive :L’horloge arrive plus tard à la destination.

- Désynchronisation négative :L’horloge arrive plus tôt à la destination.

5. Jitter

Le jitter est la variation à court terme des instants significatifs d’un signal par rapport à leurs positions idéales dans le temps. Il ajoute de l’incertitude à l’analyse de temporisation.

📊 Comparaison : Conception synchrone vs. asynchrone

Comprendre la différence entre ces deux philosophies de conception est essentiel pour interpréter correctement les diagrammes de temporisation.

| Fonctionnalité | Temporisation synchrone | Temporisation asynchrone |

|---|---|---|

| Signal de contrôle | Utilise une horloge globale | Utilise des signaux d’échange |

| Prévisibilité | Très prévisible | Variable selon la charge |

| Complexité | Exige une distribution d’horloge | Exige une logique d’échange complexe |

| Consommation d’énergie | Peut être élevée (basulement de l’horloge) | Souvent plus faible (pilotée par l’activité) |

| Diagramme de temporisation | Aligné sur les fronts d’horloge | Dépend de la fin de l’état précédent |

🧐 Comment lire et analyser les diagrammes de temporisation

Analyser une forme d’onde nécessite une approche systématique. Suivez ces étapes pour vous assurer de ne pas manquer de détails essentiels.

Étape 1 : Identifier l’horloge

Localisez le signal d’horloge principal. Il sert généralement de référence pour tous les autres temps. Dans les systèmes synchrones, chaque transition de données devrait idéalement être référencée à cet edge d’horloge.

Étape 2 : Vérifier les bourrasques

Recherchez des impulsions courtes et involontaires (bourrasques) sur les lignes de signal. Elles peuvent provoquer des déclenchements erronés dans les portes logiques. Sur un diagramme propre, les transitions doivent être nettes, bien que la capture en conditions réelles montre souvent du bruit.

Étape 3 : Vérifier les fenêtres de setup et de hold

Tracez des lignes verticales imaginaires représentant les fenêtres de setup et de hold autour du front actif de l’horloge. Assurez-vous que le signal de données est stable dans ces zones.

Étape 4 : Vérifier les signaux de contrôle

Assurez-vous que les signaux de contrôle comme Chip Select (CS) ou Enable (EN) restent actifs pendant toute la durée du transfert de données. Si un signal de contrôle chute pendant qu’un transfert est en cours, une corruption se produit.

Étape 5 : Mesurer les intervalles

Calculez le temps entre des événements spécifiques. Par exemple, mesurez la latence entre le signal « Request » et le signal « Response ». Cela aide à valider les performances par rapport aux spécifications.

🚀 Concepts avancés en analyse de temporisation

À mesure que les systèmes deviennent plus rapides et plus complexes, les diagrammes de temporisation basiques évoluent vers des exigences d’analyse sophistiquées.

1. Métastabilité

La métastabilité se produit lorsque une bascule reçoit une entrée qui viole les exigences de temps de setup ou de hold. Au lieu de se stabiliser clairement sur 0 ou 1, la sortie entre dans un état indéfini pendant une durée imprévisible.

- Cause :Cela se produit souvent lorsque des signaux asynchrones traversent des domaines d’horloge.

- Atténuation :Utilisez des chaînes de synchronisation (plusieurs bascules en série) pour réduire la probabilité de métastabilité.

- Visuel :Sur un diagramme de temporisation, cela apparaît comme un signal qui oscille ou met un temps anormalement long à se stabiliser.

2. Budgets de temps de setup et de hold

Les ingénieurs calculent un budget de temporisation pour s’assurer que le système fonctionne à la fréquence maximale. Cela consiste à soustraire toutes les délais (fils, portes, décalage d’horloge) de la période d’horloge.

Si le délai total dépasse le temps disponible, la fréquence d’opération maximale doit être réduite.

3. Chronogrammes des interfaces à haute vitesse

Des interfaces comme la mémoire DDR ou PCIe nécessitent un chronogramme extrêmement précis. Ces diagrammes incluent souvent :

- Diagrammes d’œil :Une superposition de nombreuses transitions de signal pour visualiser la qualité du signal.

- Distorsion du cycle de travail :Assurer que les durées Hautes et Basses sont équilibrées.

- Alignement de phase :Assurer que les données et l’horloge arrivent synchronisées sur plusieurs bits.

4. États de gestion de l’alimentation

Les dispositifs modernes entrent en modes à faible consommation. Les diagrammes de chronogrammes doivent tenir compte de la latence de réveil. Par exemple, un signal qui active l’alimentation d’un périphérique doit se produire avant que le dispositif ne soit prêt à recevoir des données.

📝 Meilleures pratiques pour la documentation

Une documentation claire prévient les erreurs pendant le développement et le débogage. Respectez ces normes lors de la création ou de la revue des diagrammes de chronogrammes.

- Échelle cohérente :Utilisez des échelles de temps cohérentes sur les diagrammes connexes pour permettre une comparaison facile.

- Étiquettes claires :Chaque signal doit être étiqueté avec sa fonction et sa polarité logique (par exemple,

RESET#pour actif bas). - Niveaux de zoom :Fournissez à la fois un aperçu général et une vue agrandie des transitions critiques (comme les fenêtres de setup/hold).

- Codage par couleur :Utilisez des couleurs pour distinguer entre différents domaines de tension ou sources d’horloge (par exemple, Rouge pour l’horloge, Bleu pour les données).

- Contrôle de version :Les exigences de chronogramme évoluent. Assurez-vous que les diagrammes sont versionnés pour correspondre à la révision matérielle.

🛠️ Pièges courants et dépannage

Même les ingénieurs expérimentés rencontrent des problèmes de chronogramme. Voici des scénarios courants et la manière de les résoudre.

Piège 1 : Ignorer le retard de trace

Les pistes de circuit imprimé ont une longueur physique, ce qui introduit un retard. À haute fréquence, quelques pouces de fil peuvent équivaloir à un cycle d’horloge.

- Solution : Prenez en compte la longueur de la piste dans vos calculs de budget de temporisation.

Piège 2 : Entrées flottantes

Les entrées non connectées peuvent flotter vers une tension intermédiaire, provoquant une oscillation.

- Solution : Assurez-vous que toutes les entrées disposent de résistances de tirage vers le haut ou vers le bas définies.

Piège 3 : Conditions de course

Lorsque deux signaux changent simultanément, l’ordre d’arrivée détermine le résultat.

- Solution : Utilisez une logique de synchronisation ou des machines à états pour séquencer les événements.

Piège 4 : Dépassement et sous-passe

Les réflexions de signal peuvent provoquer des tensions dépassant les rails d’alimentation (dépassement) ou tombant en dessous de la masse (sous-passe).

- Solution : Mettez en œuvre des résistances de terminaison appropriées et un ajustement d’impédance.

🔗 Applications dans le monde réel

Les diagrammes de temporisation sont appliqués dans divers domaines du génie.

1. Interfaces mémoire

La DRAM et la SDRAM nécessitent des séquences de temporisation strictes pour les opérations de lecture/écriture. La latence CAS et le délai RAS à CAS sont des paramètres critiques visualisés dans ces diagrammes.

2. Communication avec les microcontrôleurs

Les protocoles comme I2C, SPI et UART reposent sur des relations de temporisation spécifiques entre les lignes d’horloge et de données. Par exemple, dans I2C, la ligne de données doit être stable pendant que l’horloge est à l’état haut.

3. Séquençage des alimentations

Les systèmes complexes exigent que les rails d’alimentation s’allument dans un ordre spécifique. Les diagrammes de temporisation assurent que la tension du cœur est stable avant que la tension d’entrée/sortie ne soit appliquée.

🎯 Résumé des points clés

Maîtriser les diagrammes de temporisation exige de la patience et une attention aux détails. Les points suivants résument les connaissances essentielles pour une conception et une analyse efficaces.

- Le temps est critique :La logique numérique repose sur des relations temporelles précises entre les signaux.

- Préparation et maintien : Ce sont les deux contraintes les plus courantes qui déterminent la vitesse maximale de fonctionnement.

- Vérification visuelle : Les diagrammes vous permettent de repérer des conflits potentiels avant la construction du matériel.

- Le contexte compte : Prenez toujours en compte l’environnement physique (PCB, température, tension) qui influence le timing du signal.

- Normalisation :Utilisez des symboles et des notations standardisés pour assurer une clarté de communication entre les équipes.

En appliquant ces principes, vous assurez que vos systèmes numériques sont robustes, fiables et performants. La capacité à interpréter et à créer ces diagrammes est une compétence fondamentale qui distingue les conceptions fonctionnelles de celles qui échouent sur le terrain.

📈 Vers l’avant

À mesure que la technologie évolue, les contraintes de timing deviennent plus strictes. Les systèmes modernes fonctionnent à des vitesses de gigahertz où les nanosecondes ont une importance capitale. Un apprentissage continu en matière d’intégrité du signal et de fermeture du timing est nécessaire pour les ingénieurs travaillant sur des matériels de pointe.

Commencez par analyser les schémas existants et leurs diagrammes de timing correspondants. Entraînez-vous à mesurer les intervalles et à identifier les violations. Au fil du temps, les schémas deviendront intuitifs, vous permettant de prévoir les problèmes avant qu’ils ne se manifestent physiquement.