समय आरेख डिजिटल प्रणाली के सत्यापन की आधारशिला हैं। वे अमूर्त तर्क को इंजीनियरों, डिजाइनरों और परीक्षकों द्वारा संकेत व्यवहार के अनुरूप जांचने के लिए निर्भर दृश्य समय रेखाओं में बदल देते हैं। जब किसी समय आरेख में त्रुटियाँ होती हैं, तो उनके परिणाम ड्राफ्टबोर्ड से बहुत आगे तक फैल जाते हैं। गलत समय संबंधी मान्यताएँ हार्डवेयर विफलता, डेटा क्षति या उत्पादन परिवेश में प्रणाली अस्थिरता का कारण बन सकती हैं। यह मार्गदर्शिका समय विश्लेषण में पाए जाने वाली सबसे आम गलतियों का अध्ययन करती है और सटीकता सुनिश्चित करने के लिए व्यावहारिक रणनीतियाँ प्रदान करती है।

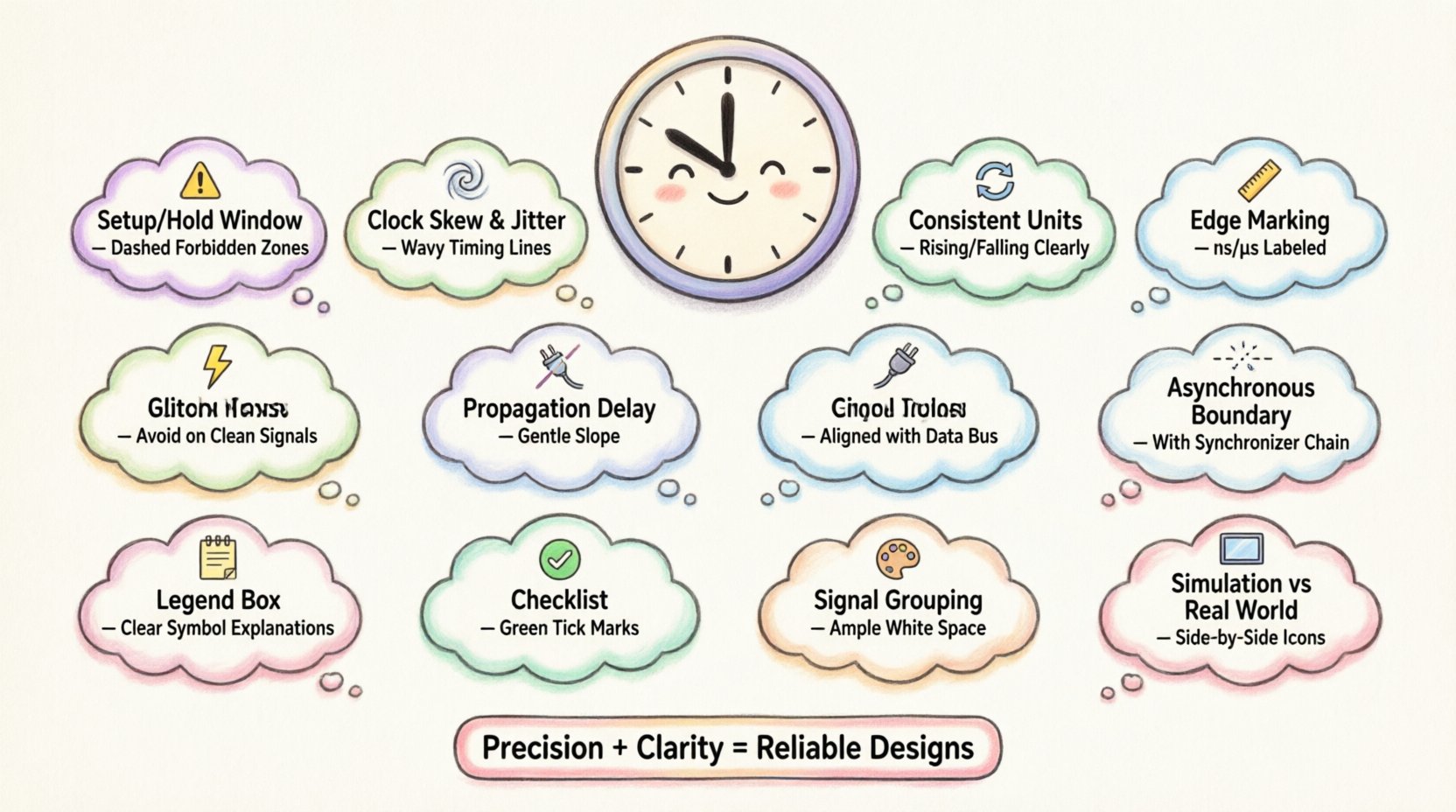

एक सटीक समय आरेख बनाने के लिए केवल रेखाएँ खींचने से अधिक चाहिए। इसमें घड़ी के क्षेत्रों, संकेत प्रसार और भौतिक सीमाओं की गहन समझ की आवश्यकता होती है। इंजीनियर अक्सर दृश्यीकरण चरण को जल्दी कर देते हैं, जिससे उन्हें छोटी-छोटी बातें नजर आती हैं जो कार्यान्वयन के दौरान महत्वपूर्ण हो जाती हैं। इन सामान्य गलतियों को जल्दी से पहचानने से टीमें डिबगिंग और एकीकरण चरणों में महत्वपूर्ण समय बचा सकती हैं। आइए उन विशिष्ट क्षेत्रों का अध्ययन करें जहाँ त्रुटियाँ आमतौर पर होती हैं।

1. सेटअप और होल्ड समय उल्लंघन के गलत अर्थ निकालना ⚠️

सेटअप और होल्ड समय सिंक्रोनस डिजिटल डिजाइन में मूल बाधाएँ हैं। जब डेटा सक्रिय घड़ी के किनारे से बहुत देर से आता है, तो सेटअप उल्लंघन होता है। जब डेटा घड़ी के किनारे के बाद बहुत जल्दी बदल जाता है, तो होल्ड उल्लंघन होता है। ये केवल सैद्धांतिक अवधारणाएँ नहीं हैं; इनका अर्थ फ्लिप-फ्लॉप और लॉजिक गेट्स की भौतिक सीमाओं को दर्शाता है।

बहुत से आरेख डेटा संकेतों के वैधता के खंड को स्पष्ट रूप से नहीं दर्शाते हैं। इन संकेतों को बनाते समय, इंजीनियर कभी-कभी महत्वपूर्ण सेटअप और होल्ड खंडों को छोड़ देते हैं, जिससे समीक्षा के दौरान अस्पष्टता उत्पन्न होती है। एक मजबूत आरेख में इन खंडों को घड़ी के किनारे के संबंध में स्पष्ट रूप से चिह्नित करना चाहिए।

- आम त्रुटि: जिटर या स्क्यू को ध्यान में रखे बिना डेटा संक्रमण को घड़ी के किनारे के साथ बिल्कुल समानांतर बनाना।

- आम त्रुटि: सेटअप/होल्ड खंडों के लिए किनारे की दिशा (बढ़ती बनाम गिरती) को नजरअंदाज करना।

- आम त्रुटि: शून्य संक्रमण समय वाले आदर्श घड़ी के किनारों को मान लेना।

इन समस्याओं से बचने के लिए, सेटअप और होल्ड सीमाओं को हमेशा टिप्पणी करें। डेटा संक्रमण अमान्य होने वाले निषिद्ध क्षेत्रों को दर्शाने के लिए अलग-अलग छायांकन या चिह्नों का उपयोग करें। इस दृश्य संकेत के कारण समीक्षकों को यह जांचना होगा कि क्या संकेत मार्ग प्राप्त करने वाली तर्क की समय सीमाओं के अनुरूप है।

2. घड़ी के स्क्यू और जिटर को नजरअंदाज करना 🌪️

घड़ी का स्क्यू विभिन्न घटकों पर घड़ी संकेत के आगमन समय के अंतर को संदर्भित करता है। जिटर घड़ी संकेत के समय में अल्पकालिक भिन्नताओं का प्रतिनिधित्व करता है। दोनों कारक डेटा संकेतों के प्रभावी समय खंडों को बहुत बदल सकते हैं।

आरेखों में एक सामान्य गलती यह है कि घड़ी को सभी घटकों के लिए एक सीधी ऊर्ध्वाधर रेखा के रूप में लिया जाता है। वास्तविकता में, वितरण नेटवर्क देरी उत्पन्न करते हैं। यदि एक आरेख में एक ही घड़ी रेखा तीन अलग-अलग रजिस्टरों में शाखा बनाती है और पथ अंतरों को ध्यान में नहीं रखती है, तो यह प्रणाली के व्यवहार के असत्य दृश्य को प्रस्तुत करता है।

- प्रभाव: स्क्यू डेटा के प्रसार के लिए उपलब्ध समय को कम कर सकता है, जिससे गलत सेटअप उल्लंघन हो सकता है।

- प्रभाव: जिटर होल्ड समय सीमा को संकुचित कर सकता है, जिससे अस्थिरता का जोखिम बढ़ जाता है।

आरेख बनाते समय, यदि स्क्यू महत्वपूर्ण है, तो घड़ी के मार्गों को अलग-अलग रेखाओं के रूप में अपेक्षित विस्थापन के साथ दर्शाएं। यदि स्क्यू नगण्य है, तो इस मान्यता को आरेख नोट्स में स्पष्ट रूप से बताएं। यदि यह समय बजट को प्रभावित करता है, तो घड़ी वितरण की जटिलता को छिपाएं नहीं।

3. असंगत समय पैमाने और इकाइयाँ 📏

सबसे सरल लेकिन सबसे नुकसानदेह त्रुटियों में से एक एक ही आरेख में समय पैमानों को मिलाना है। एक खंड में नैनोसेकंड दिखाए जा सकते हैं जबकि दूसरे में माइक्रोसेकंड दिखाए जा सकते हैं। इस असंगतता के कारण पाठक को निरंतर अनुपातों की पुनर्गणना करनी पड़ती है, जिससे गलत व्याख्या की संभावना बढ़ जाती है।

एक और समस्या स्पष्ट समय अक्ष की कमी है। स्केल बार या लेबल वाले टिक्स के बिना, पल्स की अवधि व्यक्तिगत रूप से निर्धारित हो जाती है। एक छोटा पल्स 10 नैनोसेकंड या 100 नैनोसेकंड हो सकता है, जो पाठक द्वारा अंतराल के व्याख्या पर निर्भर करता है।

संगतता बनाए रखने के लिए इन मानकों का पालन करें:

- पैमाना निर्धारित करें: आरेख के नीचे या ऊपर एक समय नाप का उपयोग करें।

- वैज्ञानिक रूप से लिखें: शीर्षक में इकाइयों (ns, μs, ps) को स्पष्ट रूप से लेबल करें।

- अनुपातों को समानुपाती रखें: घटनाओं के बीच क्षैतिज दूरी समय अंतर के बराबर होना चाहिए।

सुसंगतता विश्वास बनाती है। जब भी इंजीनियर आरेख को देखता है, उसे ड्राइंग स्केल के बारे में अनुमान लगाए बिना ही समान समयानुक्रम मान प्राप्त करना चाहिए।

4. किनारे ट्रिगर में अस्पष्टता 🔄

डिजिटल तर्क अक्सर विशिष्ट किनारे ट्रिगर पर निर्भर करता है, जैसे बढ़ते किनारे या गिरते किनारे। एक समय आरेख में स्पष्ट रूप से दिखाना चाहिए कि कौन सा किनारा क्रिया को ट्रिगर करता है। इस जगह अस्पष्टता हार्डवेयर में पूरी तरह विपरीत व्यवहार का कारण बन सकती है।

एक सामान्य गलती यह है कि क्लॉक सिग्नल को सक्रिय किनारे के बिना बनाना। उदाहरण के लिए, यदि एक फ्लिप-फ्लॉप गिरते किनारे पर ट्रिगर होता है लेकिन आरेख बढ़ते किनारे ट्रिगर के समान दिखता है, तो लॉजिक डिजाइनर गलत व्यवहार को लागू कर सकता है।

- सर्वोत्तम व्यवहार: सक्रिय किनारे को दर्शाने के लिए क्लॉक लाइन पर तीर का उपयोग करें।

- सर्वोत्तम व्यवहार: संकेतक में ट्रिगर प्रकार को लेबल करें (उदाहरण के लिए, “पॉजीडज”, “एनएडज”)।

- सर्वोत्तम व्यवहार: दोनों किनारे सक्रिय हों तभी दोहरे तीर का उपयोग करने से बचें।

स्पष्टता सर्वोच्च महत्व की है। यदि कोई सिग्नल असमानक है, तो यह सुनिश्चित करें कि इसे क्लॉक डोमेन से स्पष्ट रूप से अलग किया गया हो ताकि यह स्पष्ट न हो कि कौन सा किनारा इसे नियंत्रित करता है।

5. प्रसारण देरी को नजरअंदाज करना ⏳

प्रसारण देरी एक सिग्नल के लॉजिक गेट या तार के माध्यम से इनपुट से आउटपुट तक यात्रा करने में लगने वाला समय है। आदर्श आरेखों में, सिग्नल को तुरंत बदलते हुए दिखाया जाता है। भौतिक प्रणालियों में, हमेशा कोई देरी होती है।

जब डिजाइनर प्रसारण देरी को नजरअंदाज करते हैं, तो समय आरेख यह सुझाव देता है कि आउटपुट इनपुट बदलने के तुरंत बाद बदल जाता है। यह सिलिकॉन में होने वाले समय उल्लंघन को छिपा सकता है। उदाहरण के लिए, एक संयोजी मार्ग आरेख में क्लॉक अवधि को पूरा करता हुआ दिख सकता है, लेकिन वास्तविक देरी के कारण डेटा अगले क्लॉक किनारे के पार जाता है।

| विशेषता | आदर्श आरेख | वास्तविक दुनिया का कार्यान्वयन |

|---|---|---|

| सिग्नल संक्रमण | उर्ध्वाधर रेखा | देरी के साथ झुकी हुई रेखा |

| प्रसारण | तुरंत | गेट देरी + तार देरी |

| सेटअप मार्जिन | अक्सर जांचे बिना | सबसे खराब स्थिति को ध्यान में रखना चाहिए |

इसके निवारण के लिए, महत्वपूर्ण मार्गों के लिए अपेक्षित देरी को टिप्पणी करें। यदि देरी क्लॉक अवधि के संदर्भ में महत्वपूर्ण है, तो संक्रमण को झुकी हुई रेखा के साथ बनाएं या देरी के मान को स्पष्ट रूप से चिह्नित करें। यह दृश्य प्रस्तुतीकरण समीक्षकों को निर्माण से पहले संभावित बाधाओं को पहचानने में मदद करता है।

6. अस्थिरता के जोखिम को नजरअंदाज करना 🌌

अस्थिरता तब होती है जब फ्लिप-फ्लॉप क्लॉक किनारे के पास डेटा प्राप्त करता है, जिससे इसे अनिश्चित अवस्था में एक अनिश्चित अवधि के लिए प्रवेश करना पड़ता है। समय आरेख इस अवस्था को आमतौर पर स्पष्ट रूप से नहीं दर्शाते क्योंकि यह एक विफलता मोड है, सामान्य संचालन नहीं।

हालांकि, असिंक्रोनस इंटरफेस में मेटास्टेबिलिटी की संभावना को नजरअंदाज करना एक महत्वपूर्ण गलती है। यदि एक आरेख एक असिंक्रोनस सिग्नल को सिंक्रोनाइज़र श्रृंखला के बिना एक क्लॉक के साथ सिंक्रोनाइज़ करते हुए दिखाता है, तो डेटा के नुकसान या विकृति का खतरा होता है।

- पहचान:संशोधित सिंक्रोनाइज़ेशन के बिना क्लॉक डोमेन को पार करने वाले सिग्नलों की तलाश करें।

- दस्तावेज़ीकरण:नोट करें कि मेटास्टेबिलिटी का ज्ञात जोखिम कहाँ है और इसका निवारण कैसे किया जाता है।

- दृश्याकृति:असिंक्रोनस सीमाओं को दर्शाने के लिए बिंदीदार रेखाओं का उपयोग करें।

यहां तक कि यदि प्रणाली मेटास्टेबिलिटी को हैंडल करने के लिए डिज़ाइन की गई है, तो आरेख में सिंक्रोनाइज़ेशन चरणों को दर्शाना चाहिए। इससे यह सुनिश्चित होता है कि सत्यापन टीम को इन विशिष्ट स्थितियों के लिए परीक्षण करने की आवश्यकता है।

7. सिग्नल ग्लिचेस और खतरे ⚡

ग्लिचेस स्थायी आवेग होते हैं जो समानांतर पथों में असमान प्रसार देरी के कारण उत्पन्न होते हैं। यदि समय विश्लेषण में इनकी व्याख्या नहीं की गई है, तो ये तर्क के गलत ट्रिगरिंग का कारण बन सकते हैं।

एक सामान्य गलती यह है कि ग्लिचेस के भौतिक रूप से अनिवार्य होने पर भी साफ और स्थिर सिग्नल बनाना। उदाहरण के लिए, इनपुट के बीच स्विच करते समय एक मल्टीप्लेक्सर के आउटपुट कुछ क्षणों के लिए झपक सकता है जब तक यह स्थिर नहीं हो जाता। यदि आरेख में एक सुचारु संक्रमण दिखाया गया है, तो नीचे के लॉजिक को इन ग्लिचेस को फ़िल्टर करने के लिए डिज़ाइन नहीं किया गया हो सकता है।

आरेख में संभावित खतरे के क्षेत्रों को उजागर करें। अनोटेशन का उपयोग करके चेतावनी दें कि एक विशिष्ट सिग्नल राज्य परिवर्तन के दौरान अस्थायी व्यवहार दिखा सकता है। इससे परीक्षण रणनीति को ग्लिच डिटेक्शन स्थितियों को शामिल करने के लिए जानकारी मिलती है।

8. नियंत्रण सिग्नलों के लिए संदर्भ की कमी 🔌

नियंत्रण सिग्नलों जैसे एनेबल, रीसेट या चिप सेलेक्ट के बिना डेटा सिग्नल बेकार होते हैं। एक आरेख जो केवल डेटा लाइनों पर ध्यान केंद्रित करता है, अक्सर उस डेटा के वैध होने के लिए आवश्यक शर्तों को छोड़ देता है।

उदाहरण के लिए, एक डेटा बस वैध मान दिखा सकता है, लेकिन यदि उस खंड में “लेखन सक्षम” सिग्नल को सक्रिय नहीं दिखाया गया है, तो डेटा वास्तव में नजरअंदाज कर दिया जाता है। विपरीत रूप से, यदि “लेखन सक्षम” सक्रिय है लेकिन डेटा अवैध है, तो प्रणाली अर्थहीन डेटा लिखती है।

- नियंत्रण शामिल करें: हमेशा नियंत्रण सिग्नलों को डेटा सिग्नलों के साथ दिखाएं।

- वैधता परिभाषित करें: जब डेटा विश्वसनीय होता है, उसे दर्शाने के लिए एक “वैध” फ्लैग या समान संकेतक का उपयोग करें।

- अवस्था की स्थितियाँ: नियंत्रण सिग्नलों की अवस्था (उच्च सक्रिय बनाम निम्न सक्रिय) को स्पष्ट रूप से लेबल करें।

पूर्णता महत्वपूर्ण है। नियंत्रण सिग्नल संदर्भ के बिना एक समय आरेख अक्सर डिबगिंग के दौरान भ्रम का कारण बनता है। सुनिश्चित करें कि नियंत्रण और डेटा के बीच संबंध दृश्य रूप से स्पष्ट हो।

9. खराब अनोटेशन और लेजेंड उपयोग 📝

यहां तक कि एक सही आरेख भी अगर उचित अनोटेशन के बिना है, तो गलत तरीके से समझा जा सकता है। प्रतीक, संक्षिप्त नाम और लेजेंड को संगत रखना चाहिए और स्पष्ट करना चाहिए।

सामान्य अनोटेशन त्रुटियाँ शामिल हैं:

- वर्णनात्मक नामों के बजाय “सिग्नल A” जैसे सामान्य लेबल का उपयोग करना।

- विशिष्ट रेखा शैलियों (ठोस बनाम बिंदीदार) के अर्थ को स्पष्ट न करना।

- सक्रिय स्तर परिभाषा (सक्रिय उच्च बनाम सक्रिय निम्न) को छोड़ देना।

प्रत्येक समय आरेख का हिस्सा एक निर्दिष्ट लेजेंड खंड होना चाहिए। यह प्रत्येक प्रतीक, रेखा शैली और संक्षिप्त नाम को परिभाषित करता है। इससे पाठक पर मानसिक भार कम होता है और यह सुनिश्चित करता है कि सभी आरेख को एक ही तरीके से समझते हैं।

10. सत्यापन और समीक्षा चेकलिस्ट ✅

समय आरेख को अंतिम रूप देने से पहले, एक व्यवस्थित समीक्षा की आवश्यकता होती है। अपने कार्य की सटीकता और स्पष्टता की पुष्टि करने के लिए निम्नलिखित चेकलिस्ट का उपयोग करें।

| चेक आइटम | पास मानदंड |

|---|---|

| समय पैमाना | स्थिर इकाइयाँ और स्पष्ट रूलर प्रदान किए गए |

| घड़ी किनारा | सभी घड़ियों के लिए सक्रिय किनारा स्पष्ट रूप से चिह्नित किया गया |

| सेटअप/होल्ड | सिंक्रोनस सिग्नल्स के लिए खिड़कियाँ परिभाषित की गई हैं |

| प्रसारण | महत्वपूर्ण मार्गों में देरी को ध्यान में रखा गया |

| नियंत्रण सिग्नल | एनेबल/रीसेट सिग्नल को डेटा के साथ दिखाया गया |

| प्रतीकों की व्याख्या | सभी प्रतीकों और संक्षिप्त रूपों की व्याख्या की गई |

| डोमेन क्रॉसिंग | CDC बिंदुओं की पहचान की गई और चिह्नित की गई |

इस चेकलिस्ट को नियमित रूप से अपडेट करने से यह सुनिश्चित होता है कि कोई भी सामान्य गलती छूट न जाए। यह डॉक्यूमेंटेशन के इंजीनियरिंग टीम तक पहुंचने से पहले गुणवत्ता के द्वार के रूप में कार्य करता है।

11. दृश्य स्पष्टता और लेआउट डिज़ाइन 🎨

समय आरेख का लेआउट त्रुटियों के पता लगाने में कितनी आसानी होती है, इस पर प्रभाव डालता है। ओवरलैपिंग सिग्नल वाले भारी आरेख गलत पढ़ने के लिए अधिक झुके होते हैं। संबंधित सिग्नलों का ऊर्ध्वाधर संरेखण आंख को घटनाओं के बीच संबंध का पता लगाने में मदद करता है।

इन लेआउट सिद्धांतों का पालन करें:

- सिग्नलों को समूहित करें:संबंधित सिग्नलों (जैसे पता और डेटा) को एक साथ रखें।

- किनारों को संरेखित करें:सुनिश्चित करें कि सभी चैनलों में घड़ी के किनारे ऊर्ध्वाधर रूप से संरेखित हों।

- जगह छोड़ें:सिग्नल ओवरलैप को बचाने के लिए पर्याप्त सफेद जगह छोड़ें।

- रंग कोडिंग:अगर उपलब्ध हो, तो विभिन्न घड़ी क्षेत्रों के लिए अलग-अलग रंगों का उपयोग करें (हालांकि मुद्रित के लिए काला और सफेद मानक है)।

एक साफ लेआउट आरेख के अर्थ को समझने के लिए आवश्यक मानसिक प्रयास को कम करता है। इससे तुरंत विचलन और समय संबंधी उल्लंघन को देखना आसान हो जाता है।

12. वास्तविक दुनिया की सीमाएं बनाम सिमुलेशन 🖥️

केवल सिमुलेशन से प्राप्त टाइमिंग आरेख भौतिक वास्तविता को दर्शा सकते हैं। सिमुलेशन उपकरण अक्सर आदर्श स्थितियों के बारे में मानते हैं, जैसे शून्य पैरासिटिक धारिता और पूर्ण रूटिंग।

सिमुलेशन परिणामों को दस्तावेजीकरण में बदलते समय, इंजीनियरों को उत्पादन में भिन्नताओं को ध्यान में रखना होता है। प्रक्रिया, वोल्टेज और तापमान (PVT) कोने समय सीमा को बदल सकते हैं। केवल नामांकित मान दिखाने वाला आरेख लचीले डिजाइन के लिए पर्याप्त नहीं हो सकता है।

- सबसे खराब मामला:समय विश्लेषण के लिए सबसे धीमे प्रक्रिया कोने को ध्यान में रखें।

- सबसे तेज मामला:होल्ड समय विश्लेषण के लिए सबसे तेज प्रक्रिया कोने को ध्यान में रखें।

- मार्जिन:PVT भिन्नताओं को ध्यान में रखने के लिए आरेख में सुरक्षा मार्जिन जोड़ें।

दस्तावेजीकरण डिजाइन की लचीलापन को दर्शाना चाहिए, केवल बेहतरीन सिमुलेशन परिणामों को नहीं। इससे टीम को वास्तविक दुनिया के डेप्लॉयमेंट स्थितियों के लिए तैयार किया जाता है।

टाइमिंग सटीकता पर अंतिम विचार 🛡️

टाइमिंग आरेख तकनीकी विनिर्देशों के समान ही संचार उपकरण हैं। उनका मुख्य उद्देश्य सभी हितधारकों को इरादे और सीमाओं को स्पष्ट रूप से समझाना है। विक्षेप को नजरअंदाज करने, किनारे ट्रिगर को अनदेखा करने या नियंत्रण सिग्नल को छोड़ने जैसी आम गलतियों से बचकर इंजीनियर यह सुनिश्चित करते हैं कि डिजाइन का इरादा दस्तावेजीकरण से हार्डवेयर तक सुरक्षित रहे।

इन आरेखों में सटीकता के कारण महंगे री-स्पिन और डीबगिंग चक्कर बचते हैं। एक अच्छी तरह से संरचित आरेख पूरे प्रोजेक्ट जीवनचक्र के लिए एकमात्र सच्चाई का स्रोत बनता है। समय निवेश करें ताकि टाइमिंग विश्लेषण सही हो, और नीचे के कार्यान्वयन में चलना आसान हो।

याद रखें कि एक टाइमिंग आरेख एक जीवंत दस्तावेज है। जब भी डिजाइन में परिवर्तन होता है, उसे अपडेट किया जाना चाहिए। टाइमिंग जानकारी की अखंडता बनाए रखने से यह सुनिश्चित होता है कि प्रणाली अपने संचालन जीवनकाल भर विश्वसनीय रहे। लचीले डिजिटल डिजाइन प्रदान करने के लिए सटीकता, स्पष्टता और पूर्णता पर ध्यान केंद्रित करें।