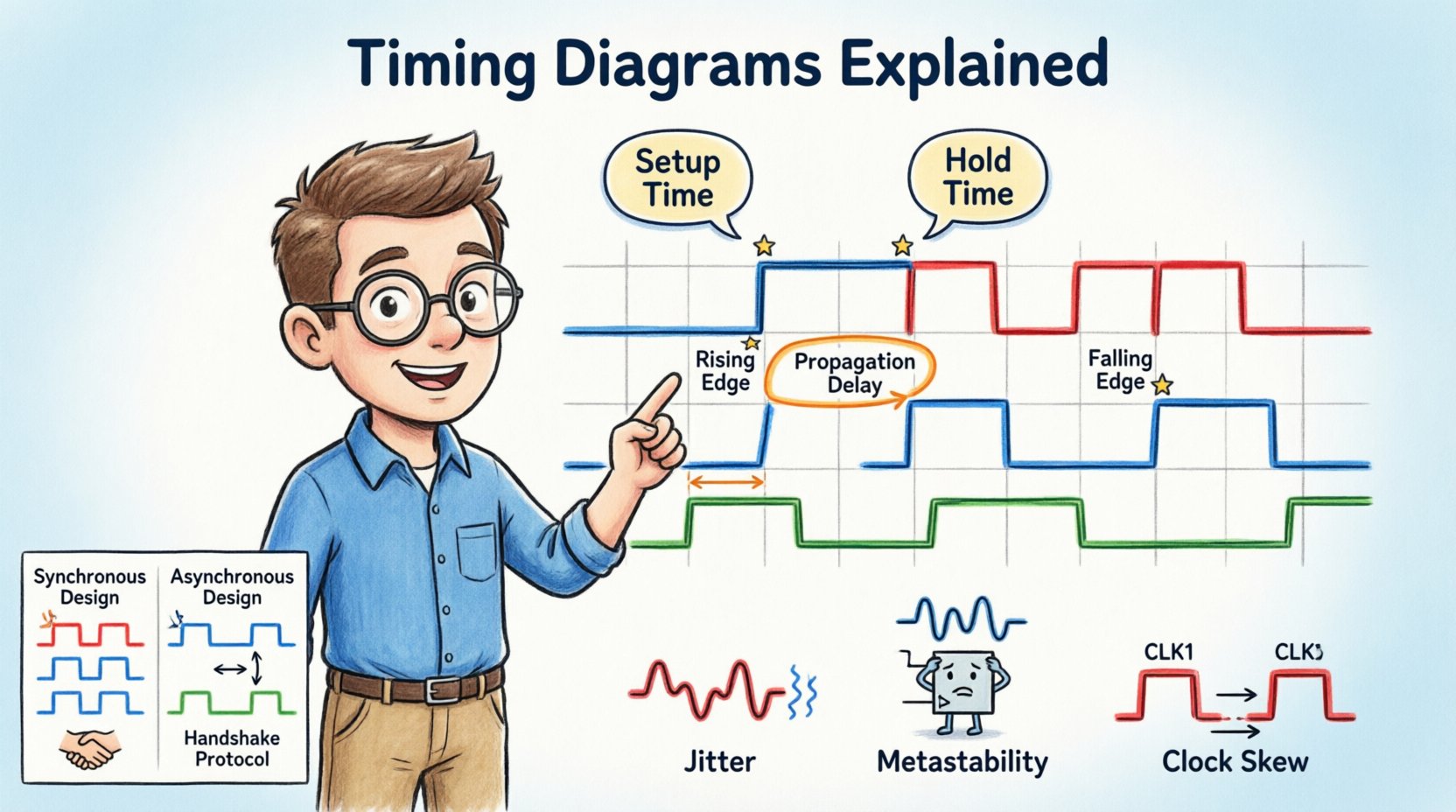

डिजिटल इलेक्ट्रॉनिक्स और सिस्टम डिजाइन की दुनिया में, समय केवल एक आयाम नहीं है; यह एक महत्वपूर्ण पैरामीटर है जो तय करता है कि क्या एक सर्किट सही तरीके से काम करेगा या भयंकर तरीके से विफल हो जाएगा।टाइमिंग डायग्राम्सइंजीनियर द्वारा समय के साथ सिग्नलों के व्यवहार को समझाने के लिए उपयोग की जाने वाली दृश्य भाषा के रूप में काम करते हैं। चाहे आप माइक्रोकंट्रोलर इंटरफेस डिजाइन कर रहे हों, मेमोरी बस के डिबगिंग कर रहे हों, या उच्च गति डेटा संचरण का विश्लेषण कर रहे हों, इन डायग्राम्स को समझना अनिवार्य है।

यह मार्गदर्शिका टाइमिंग डायग्राम्स की यांत्रिकी का अध्ययन करती है, जटिल सिग्नल व्यवहार को समझने योग्य घटकों में तोड़ती है। हम मूल परिभाषाओं से उन्नत विश्लेषण तक जाएंगे, ताकि आप तरंगरूपों को सटीकता के साथ व्याख्या करने के लिए उपकरण प्राप्त कर सकें।

🔍 टाइमिंग डायग्राम क्या है?

एक टाइमिंग डायग्राम एक डिजिटल सिस्टम में सिग्नल परिवर्तनों के क्रम का एक आलेखी प्रतिनिधित्व है। एक स्कीमेटिक के विपरीत, जो घटकों के जुड़ाव को दिखाता है, एक टाइमिंग डायग्राम दिखाता हैजबवे जुड़ाव अवस्था बदलते हैं। यह एक क्षैतिज समय अक्ष के साथ सिग्नल गतिविधि को मैप करता है, जिससे डिजाइनर यह सत्यापित कर सकते हैं कि डेटा क्लॉक एज से पहले स्थिर है या नियंत्रण सिग्नल सही समय पर असरित होते हैं।

इन डायग्राम्स का उपयोग निम्नलिखित के लिए आवश्यक है:

- हार्डवेयर और सॉफ्टवेयर अंतरक्रिया की पुष्टि करना।

- संचार प्रोटोकॉल के डिबगिंग करना।

- सेटअप और होल्ड समय की आवश्यकताओं को पूरा करने की गारंटी देना।

- भविष्य के रखरखाव के लिए सिस्टम व्यवहार का दस्तावेजीकरण करना।

समय की स्पष्ट समझ के बिना, यहां तक कि तार्किक रूप से सही सर्किट भी सिग्नल रेस या मेटास्टेबिलिटी के कारण विफल हो सकता है।

🛠️ टाइमिंग डायग्राम के मुख्य घटक

एक टाइमिंग डायग्राम को प्रभावी ढंग से पढ़ने के लिए, आपको इसके मूल निर्माण ब्लॉक्स की पहचान करनी होगी। प्रत्येक तत्व डिजिटल सिस्टम की अवस्था और प्रवाह के संबंध में विशिष्ट जानकारी ले जाता है।

1. समय अक्ष

क्षैतिज रेखा समय के प्रगमन का प्रतिनिधित्व करती है। यह आमतौर पर बाएं से दाएं बहती है। विस्तृत तकनीकी दस्तावेजों में, इस अक्ष को विशिष्ट समय इकाइयों (नैनोसेकंड, पिकोसेकंड) या क्लॉक साइकिल के साथ चिह्नित किया जा सकता है।

2. सिग्नल लाइनें

ऊर्ध्वाधर रेखाएं व्यक्तिगत सिग्नलों का प्रतिनिधित्व करती हैं, जैसे क्लॉक लाइनें, डेटा बसें या नियंत्रण लाइनें (जैसे चिप सेलेक्ट या रीड/राइट)। प्रत्येक लाइन सर्किट में एक विशिष्ट नोड के संबंध में होती है।

3. लॉजिक स्तर

सिग्नल आमतौर पर दो अवस्थाओं में से एक में मौजूद होते हैं:

- उच्च (लॉजिक 1 / VCC):आमतौर पर सिग्नल ट्रैक के शीर्ष पर एक रेखा द्वारा दर्शाया जाता है।

- निम्न (लॉजिक 0 / GND):आमतौर पर सिग्नल ट्रैक के नीचे एक रेखा द्वारा दर्शाया जाता है।

कुछ प्रणालियां एक्टिव लोलॉजिक, जहां सिग्नल वोल्टेज कम होने पर अपना कार्य करता है। डायग्राम में, इसे आमतौर पर सिग्नल नाम के पास एक बबल या विशिष्ट नोटेशन द्वारा इंगित किया जाता है।

4. संक्रमण

संक्रमण वे क्षण हैं जब कोई सिग्नल हाई से लो या लो से हाई में बदलता है।

- राइजिंग एज:लो से हाई की ओर संक्रमण। घटनाओं को ट्रिगर करने के लिए महत्वपूर्ण।

- फॉलिंग एज:हाई से लो की ओर संक्रमण। विशिष्ट नियंत्रण अनुक्रमों के लिए उपयोग किया जाता है।

- एज-ट्रिगर्ड: सिग्नल का मूल्यांकन केवल संक्रमण के दौरान किया जाता है, स्थिर अवस्था के दौरान नहीं।

⚙️ मुख्य समय संबंधी पैरामीटर

सटीक डिजिटल डिज़ाइन सिग्नलों के बीच संबंध को मापने पर निर्भर करता है। निम्नलिखित पैरामीटर समय विश्लेषण की आधारशिला हैं।

1. प्रोपेगेशन देरी (tpd)

यह वह समय है जिसमें कोई सिग्नल लॉजिक गेट या घटक के इनपुट से आउटपुट तक यात्रा करता है। कोई भी सिग्नल तुरंत नहीं बदलता; भौतिक सीमाएं देरी का कारण बनती हैं।

- महत्व: यदि देरी बहुत अधिक है, तो बाद की लॉजिक डेटा बहुत देर से प्राप्त कर सकती है, जिससे त्रुटियां हो सकती हैं।

- मापन: इनपुट संक्रमण के 50% वोल्टेज बिंदु से आउटपुट संक्रमण के 50% वोल्टेज बिंदु तक मापा जाता है।

2. सेटअप समय (tsu)

सेटअप समय वह न्यूनतम अवधि है जिसके दौरान डेटा सिग्नल स्थिर रहने की आवश्यकता होती हैपहले क्लॉक एज आने से पहले।

- परिदृश्य: यदि एक फ्लिप-फ्लॉप को क्लॉक ट्रिगर होने से 5 नैनोसेकंड पहले डेटा तैयार होने की आवश्यकता हो, तो वह सेटअप समय है।

- उल्लंघन: यदि डेटा क्लॉक एज के बहुत निकट बदलता है, तो सिस्टम मान को सही तरीके से कैप्चर नहीं कर पाता है।

3. होल्ड समय (th)

होल्ड समय वह न्यूनतम अवधि है जिसके दौरान डेटा सिग्नलों को स्थिर रहना चाहिएके बादएक क्लॉक एज आता है।

- परिदृश्य: फ्लिप-फ्लॉप को ट्रिगर के बाद डेटा को एक छोटी अवधि के लिए “देखना” होगा ताकि इसे सुरक्षित रूप से लैच किया जा सके।

- उल्लंघन: यदि डेटा क्लॉक एज के तुरंत बाद बदल जाता है, तो इनपुट सही तरीके से लैच नहीं हो सकता है।

4. क्लॉक स्क्यू

क्लॉक स्क्यू तब होता है जब क्लॉक सिग्नल विभिन्न घटकों पर अलग-अलग समय पर पहुंचता है। इसका कारण अक्सर PCB पर ट्रेस लंबाई के अंतर के कारण होता है।

- सकारात्मक स्क्यू: क्लॉक गंतव्य पर बाद में पहुंचता है।

- नकारात्मक स्क्यू: क्लॉक गंतव्य पर पहले पहुंचता है।

5. जिटर

जिटर समय में किसी सिग्नल के महत्वपूर्ण क्षणों के अपनी आदर्श स्थितियों से छोटी अवधि के अंतर को कहते हैं। यह समय विश्लेषण में अनिश्चितता जोड़ता है।

📊 तुलना: सिंक्रोनस बनाम एसिंक्रोनस डिज़ाइन

इन दोनों डिज़ाइन दृष्टिकोणों के बीच अंतर को समझना समय आरेखों को सही तरीके से व्याख्या करने के लिए आवश्यक है।

| विशेषता | सिंक्रोनस समय | एसिंक्रोनस समय |

|---|---|---|

| नियंत्रण सिग्नल | एक वैश्विक क्लॉक का उपयोग करता है | हैंडशेकिंग सिग्नलों का उपयोग करता है |

| पूर्वानुमान | बहुत अधिक पूर्वानुमान योग्य | लोड पर आधारित चर |

| जटिलता | क्लॉक वितरण की आवश्यकता होती है | जटिल हैंडशेक तर्क की आवश्यकता होती है |

| पावर उपभोग | उच्च हो सकता है (क्लॉक टॉगलिंग) | अक्सर कम (गतिविधि संचालित) |

| टाइमिंग आरेख | क्लॉक किनारों के साथ संरेखित | पिछले अवस्था पूर्ण होने पर निर्भर |

🧐 टाइमिंग आरेखों को पढ़ना और विश्लेषित करना कैसे करें

एक तरंगरूप का विश्लेषण करने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। महत्वपूर्ण विवरणों को छोड़ने से बचने के लिए इन चरणों का पालन करें।

चरण 1: क्लॉक की पहचान करें

मुख्य क्लॉक सिग्नल को स्थापित करें। यह आमतौर पर सभी अन्य समय संबंधी चीजों के लिए संदर्भ होता है। सिंक्रोनस प्रणालियों में, प्रत्येक डेटा संक्रमण को इस क्लॉक किनारे के संदर्भ में आदर्श रूप से बनाया जाना चाहिए।

चरण 2: ग्लिचेस की जांच करें

सिग्नल लाइनों पर छोटे, अनचाहे पल्स (ग्लिचेस) की तलाश करें। इनके लॉजिक गेट में गलत ट्रिगर करने की संभावना होती है। एक साफ आरेख में, संक्रमण साफ होने चाहिए, हालांकि वास्तविक दुनिया के अनुभव में अक्सर शोर होता है।

चरण 3: सेटअप और होल्ड विंडो की पुष्टि करें

सक्रिय क्लॉक किनारे के चारों ओर सेटअप और होल्ड विंडो का प्रतिनिधित्व करने वाली काल्पनिक ऊर्ध्वाधर रेखाएं खींचें। सुनिश्चित करें कि डेटा सिग्नल इन क्षेत्रों के भीतर स्थिर है।

चरण 4: नियंत्रण सिग्नलों की जांच करें

सुनिश्चित करें कि चिप सेलेक्ट (CS) या एनेबल (EN) जैसे नियंत्रण सिग्नल डेटा स्थानांतरण के पूरे दौरान सक्रिय रहें। यदि डेटा अभी भी भेजे जा रहे हों तो नियंत्रण सिग्नल गिर जाता है, तो विकृति हो जाती है।

चरण 5: अंतराल मापें

विशिष्ट घटनाओं के बीच के समय की गणना करें। उदाहरण के लिए, एक “अनुरोध” सिग्नल से “प्रतिक्रिया” सिग्नल तक की देरी को मापें। यह विनिर्देशों के अनुसार प्रदर्शन की पुष्टि करने में मदद करता है।

🚀 टाइमिंग विश्लेषण में उन्नत अवधारणाएं

जैसे-जैसे प्रणालियां तेज और अधिक जटिल होती हैं, मूल टाइमिंग आरेख सूक्ष्म विश्लेषण की आवश्यकताओं में विकसित होते जाते हैं।

1. मेटास्टेबिलिटी

मेटास्टेबिलिटी तब होती है जब फ्लिप-फ्लॉप को सेटअप या होल्ड समय के आवश्यकताओं के उल्लंघन करने वाला इनपुट मिलता है। स्पष्ट 0 या 1 में निर्णय लेने के बजाय, आउटपुट एक अपरिभाषित अवस्था में अनिश्चित अवधि के लिए प्रवेश करता है।

- कारण:अक्सर तब होता है जब असिंक्रोनस सिग्नल क्लॉक डोमेन को पार करते हैं।

- उपाय:मेटास्टेबिलिटी की संभावना को कम करने के लिए सिंक्रोनाइज़र श्रृंखला (श्रृंखला में बहुत से फ्लिप-फ्लॉप) का उपयोग करें।

- दृश्य:टाइमिंग आरेख पर, इसे एक सिग्नल के दोहराव या असामान्य रूप से लंबे समय तक स्थिर होने के रूप में देखा जाता है।

2. सेटअप और होल्ड समय बजट

इंजीनियर एक टाइमिंग बजट की गणना करते हैं ताकि यह सुनिश्चित किया जा सके कि प्रणाली अधिकतम आवृत्ति पर काम करे। इसमें क्लॉक अवधि से सभी देरी (तार, गेट, क्लॉक स्क्यू) को घटाना शामिल है।

यदि कुल देरी उपलब्ध समय से अधिक हो जाती है, तो अधिकतम संचालन आवृत्ति को कम करना होगा।

3. उच्च गति इंटरफेस समयानुसार

DDR मेमोरी या PCIe जैसे इंटरफेस को अत्यधिक सटीक समयानुसार आवश्यकता होती है। इन आरेखों में अक्सर शामिल होते हैं:

- आई आरेख: सिग्नल गुणवत्ता को देखने के लिए बहुत सारे सिग्नल संक्रमणों का अतिव्यापन।

- ड्यूटी साइकिल विकृति: यह सुनिश्चित करना कि उच्च और निम्न समय संतुलित हों।

- फेज समन्वय: बहुत सारे बिट्स के माध्यम से डेटा और क्लॉक के सिंक में आने की गारंटी देना।

4. पावर प्रबंधन अवस्थाएँ

आधुनिक उपकरण निम्न शक्ति मोड में प्रवेश करते हैं। समय आरेखों को जागृत होने के लैटेंसी को ध्यान में रखना चाहिए। उदाहरण के लिए, एक पेरिफेरल को पावर देने वाला सिग्नल उपकरण डेटा प्राप्त करने के लिए तैयार होने से पहले होना चाहिए।

📝 दस्तावेजीकरण के लिए सर्वोत्तम प्रथाएँ

स्पष्ट दस्तावेजीकरण विकास और डीबगिंग के दौरान त्रुटियों को रोकता है। समय आरेख बनाने या समीक्षा करते समय इन मानकों का पालन करें।

- संगत एकरूपता: संबंधित आरेखों में समय के संगत पैमाने का उपयोग करें ताकि आसानी से तुलना की जा सके।

- स्पष्ट लेबल: प्रत्येक सिग्नल को उसके कार्य और तर्क ध्रुवता (उदाहरण के लिए,

RESET#एक्टिव लो के लिए)। - जूम स्तर: महत्वपूर्ण संक्रमणों (जैसे सेटअप/होल्ड विंडो) के लिए उच्च स्तर का सारांश और जूम किए गए दृश्य प्रदान करें।

- रंग कोडिंग: विभिन्न वोल्टेज क्षेत्रों या क्लॉक स्रोतों के बीच अंतर करने के लिए रंगों का उपयोग करें (उदाहरण के लिए, क्लॉक के लिए लाल, डेटा के लिए नीला)।

- संस्करण नियंत्रण: समय सीमाएँ बदलती हैं। सुनिश्चित करें कि आरेखों को हार्डवेयर संस्करण के अनुरूप संस्करणित किया गया हो।

🛠️ सामान्य त्रुटियाँ और समस्या निवारण

यहाँ तक कि अनुभवी � ingineers को भी समय संबंधी समस्याओं का सामना करना पड़ता है। यहाँ आम परिस्थितियाँ और उन्हें कैसे संबोधित करना है, उनके बारे में है।

त्रुटि 1: ट्रेस देरी को नजरअंदाज करना

PCB ट्रेस की भौतिक लंबाई होती है, जिससे देरी आती है। उच्च आवृत्तियों पर, कुछ इंच तार एक क्लॉक साइकिल के बराबर हो सकते हैं।

- समाधान: अपने समय बजट गणनाओं में ट्रेस लंबाई को ध्यान में रखें।

गलती 2: तैरते हुए इनपुट

अनकनेक्टेड इनपुट एक मध्यवर्ती वोल्टेज तक तैर सकते हैं, जिससे दोलन होता है।

- समाधान: सुनिश्चित करें कि सभी इनपुट में परिभाषित पुल-अप या पुल-डाउन प्रतिरोध हों।

गलती 3: दौड़ की स्थिति

जब दो सिग्नल एक साथ बदलते हैं, तो आगमन का क्रम परिणाम निर्धारित करता है।

- समाधान: घटनाओं के क्रम को नियंत्रित करने के लिए सिंक्रोनाइजेशन लॉजिक या स्टेट मशीन का उपयोग करें।

गलती 4: ओवरशूट और अंडरशूट

सिग्नल प्रतिबिंबन के कारण वोल्टेज पावर रेल्स को पार कर सकते हैं (ओवरशूट) या ग्राउंड से नीचे गिर सकते हैं (अंडरशूट)।

- समाधान: सही टर्मिनेशन प्रतिरोधक और इम्पीडेंस मैचिंग कार्यान्वित करें।

🔗 वास्तविक दुनिया के अनुप्रयोग

समय आरेखों का इंजीनियरिंग के विभिन्न क्षेत्रों में उपयोग किया जाता है।

1. मेमोरी इंटरफेस

DRAM और SDRAM को पढ़ने/लिखने के ऑपरेशन के लिए सख्त समय क्रम की आवश्यकता होती है। CAS लेटेंसी और RAS से CAS देरी महत्वपूर्ण पैरामीटर हैं जो इन आरेखों में दृश्यमान होते हैं।

2. माइक्रोकंट्रोलर संचार

I2C, SPI और UART जैसे प्रोटोकॉल को क्लॉक और डेटा लाइनों के बीच विशिष्ट समय संबंधों पर निर्भर रहना होता है। उदाहरण के लिए, I2C में, क्लॉक उच्च होने के दौरान डेटा लाइन स्थिर होनी चाहिए।

3. पावर सप्लाई क्रमबद्धता

जटिल प्रणालियों को विशिष्ट क्रम में पावर रेल्स चालू करने की आवश्यकता होती है। समय आरेख सुनिश्चित करते हैं कि I/O वोल्टेज लागू करने से पहले कोर वोल्टेज स्थिर हो।

🎯 मुख्य बातों का सारांश

समय आरेखों को समझने के लिए धैर्य और विस्तार से ध्यान देने की आवश्यकता होती है। निम्नलिखित बिंदु दक्ष डिजाइन और विश्लेषण के लिए आवश्यक ज्ञान का सारांश प्रस्तुत करते हैं।

- समय महत्वपूर्ण है: डिजिटल लॉजिक सिग्नलों के बीच सटीक समय संबंधों पर निर्भर करता है।

- सेटअप और होल्ड: ये दो सबसे आम सीमाएं हैं जो अधिकतम संचालन गति को निर्धारित करती हैं।

- दृश्य सत्यापन: आरेख आपको हार्डवेयर बनाए जाने से पहले संभावित संघर्षों को देखने की अनुमति देते हैं।

- संदर्भ महत्वपूर्ण है: सदैव भौतिक परिवेश (PCB, तापमान, वोल्टेज) को ध्यान में रखें जो सिग्नल समय को प्रभावित करता है।

- मानकीकरण:टीमों के बीच संचार स्पष्टता सुनिश्चित करने के लिए मानक प्रतीकों और नोटेशन का उपयोग करें।

इन सिद्धांतों के अनुप्रयोग से आप यह सुनिश्चित करते हैं कि आपके डिजिटल प्रणाली दृढ़, विश्वसनीय और कार्यक्षम हैं। इन आरेखों को समझने और बनाने की क्षमता एक मूलभूत कौशल है जो कार्यात्मक डिजाइनों को उन डिजाइनों से अलग करता है जो मैदान में विफल हो जाते हैं।

📈 आगे बढ़ना

तकनीक विकसित होने के साथ, समय सीमाएं संकीर्ण हो जाती हैं। आधुनिक प्रणालियां गीगाहर्ट्ज गति पर काम करती हैं जहां नैनोसेकंड महत्वपूर्ण होते हैं। अग्रणी हार्डवेयर पर काम कर रहे � ingineers के लिए सिग्नल अखंडता और समय सीमा बंद करने के बारे में निरंतर सीखना आवश्यक है।

मौजूदा आरेखों और उनके संबंधित समय आरेखों के विश्लेषण से शुरुआत करें। अंतराल मापने और उल्लंघनों की पहचान करने का अभ्यास करें। समय के साथ, ये पैटर्न स्वाभाविक हो जाएंगे, जिससे आप उन समस्याओं की भविष्यवाणी कर सकेंगे जो भौतिक रूप से प्रकट होने से पहले ही दिखाई देंगी।