डिजिटल इलेक्ट्रॉनिक्स और हार्डवेयर इंजीनियरिंग की दुनिया में, घटकों के बीच संचार सटीक समन्वय पर निर्भर करता है। जब तक सिग्नल के राज्य में बदलाव के समय का स्पष्ट ज्ञान नहीं होता, तब तक प्रणाली विफल हो जाती है। टाइमिंग डायग्राम इस समन्वय के लिए नक्शा के रूप में कार्य करता है। यह समय के साथ सिग्नलों के बीच संबंध को दृश्यमान बनाता है, जो बताता है कि डेटा मान्य, स्थिर और प्रोसेसिंग के लिए तैयार है या नहीं। यह मार्गदर्शिका इंजीनियरों और छात्रों द्वारा इन महत्वपूर्ण दृश्य उपकरणों के विश्लेषण के दौरान सामना किए जाने वाले मूल सवालों का समाधान करती है।

चाहे आप माइक्रोकंट्रोलर इंटरफेस डिज़ाइन कर रहे हों, संचार प्रोटोकॉल के डिबगिंग में लगे हों, या डिजिटल लॉजिक का अध्ययन कर रहे हों, अपने डिज़ाइन के समय संबंधी पहलुओं को समझना अनिवार्य है। यह लेख टाइमिंग डायग्राम की रचना का अध्ययन करता है, महत्वपूर्ण पैरामीटर्स की व्याख्या करता है, और सिग्नल अखंडता और समन्वय से संबंधित आम सवालों के उत्तर देता है।

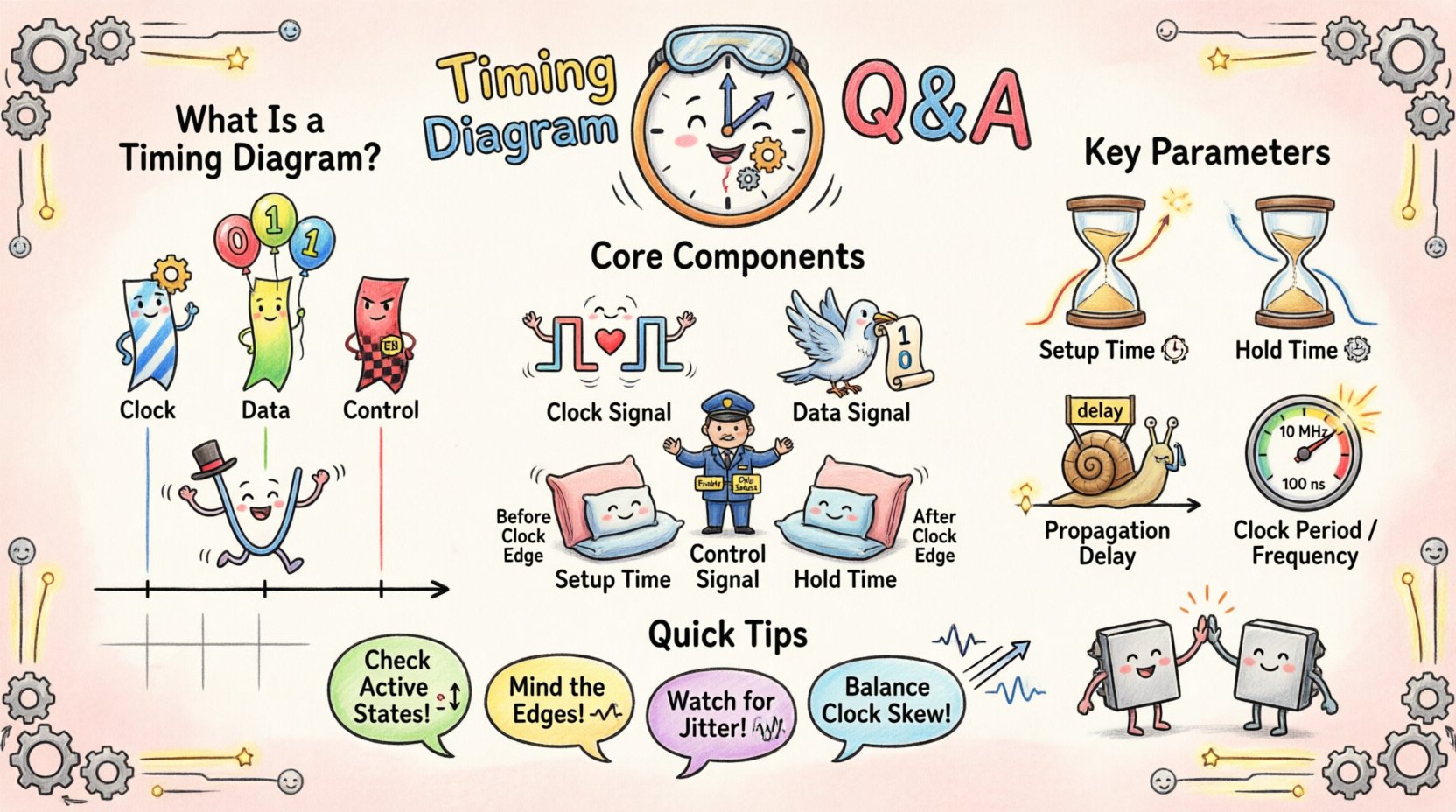

टाइमिंग डायग्राम वास्तव में क्या है? 📊

एक टाइमिंग डायग्राम एक प्रणाली में घटनाओं के क्रम का एक आलेखी प्रतिनिधित्व है। इसमें सिग्नल स्तरों को क्षैतिज समय अक्ष के सापेक्ष आलेखित किया जाता है। लॉजिक डायग्राम के विपरीत जो जुड़ाव दिखाता है, टाइमिंग डायग्राम व्यवहार दिखाता है। इससे आप देख सकते हैं कि कोई सिग्नल दूसरी सिग्नल के पहले या बाद में उच्च या निम्न स्तर पर बदलता है या नहीं। यह दृश्य संदर्भ आवश्यक है कि अगले क्लॉक एज आने से पहले रिसीवर को डेटा पढ़ने के लिए पर्याप्त समय मिले, इसकी पुष्टि करने के लिए।

मुख्य विशेषताएं शामिल हैं:

- समय अक्ष:आमतौर पर बाएं से दाएं क्षैतिज दिशा में चलता है।

- सिग्नल लाइनें:अलग-अलग तारों या डेटा बस का प्रतिनिधित्व करने वाली क्षैतिज रेखाएं।

- लॉजिक स्तर:उच्च (1) और निम्न (0) अवस्थाओं को अलग-अलग वोल्टेज प्लेटॉन के रूप में दर्शाया जाता है।

- किनारे:एक अवस्था से दूसरी अवस्था में संक्रमण को दर्शाने वाली ऊर्ध्वाधर रेखाएं।

टाइमिंग डायग्राम के मुख्य घटक 🧩

इन डायग्रामों को प्रभावी ढंग से पढ़ने के लिए, आपको तरंगरूप के बनाने वाले मानक तत्वों की पहचान करनी होगी। प्रत्येक तत्व प्रणाली के समन्वय में एक विशिष्ट भूमिका निभाता है।

| घटक | विवरण | दृश्य संकेतक |

|---|---|---|

| क्लॉक सिग्नल | प्रणाली के लिए धड़कन प्रदान करता है। अन्य सिग्नल आमतौर पर इसके सापेक्ष नमूना लिए जाते हैं। | नियमित वर्ग तरंग पैटर्न |

| डेटा सिग्नल | स्थानांतरित हो रही वास्तविक जानकारी को ले जाता है। | इनपुट पर आधारित अनियमित संक्रमण |

| नियंत्रण सिग्नल | डेटा के प्रवाह को नियंत्रित करता है (उदाहरण के लिए, एनेबल, चिप सेलेक्ट, लिखना)। | एक्टिव उच्च या एक्टिव निम्न पल्स |

| सेटअप समय | क्लॉक एज से पहले डेटा को स्थिर रहने के लिए आवश्यक समयावधि। | किनारे से पहले क्षैतिज दूरी |

| होल्ड समय | डेटा को क्लॉक एज के बाद स्थिर रहना चाहिए। | किनारे के बाद क्षैतिज दूरी |

महत्वपूर्ण समय सीमा पैरामीटर्स को समझना ⚙️

समय सीमा पैरामीटर्स उन सीमाओं को परिभाषित करते हैं जिनके भीतर एक डिजिटल सर्किट सही तरीके से काम करता है। इन पैरामीटर्स के उल्लंघन के कारण अप्रत्याशित व्यवहार होने की संभावना होती है। नीचे सबसे महत्वपूर्ण मापदंडों की परिभाषाएं और प्रभाव दिए गए हैं।

1. सेटअप समय ⏳

सेटअप समय वह न्यूनतम समय है जिसके दौरान डेटा सिग्नल को क्लॉक सिग्नल के ट्रिगरिंग एज से पहले स्थिर रखा जाना चाहिए। यदि डेटा क्लॉक एज के बहुत निकट बदलता है, तो फ्लिप-फ्लॉप सही तरीके से मान को कैप्चर नहीं कर सकता है। यह अक्सर उच्च गति डिजाइन में सबसे महत्वपूर्ण सीमा होती है क्योंकि यह ऑपरेशन की अधिकतम आवृत्ति को निर्धारित करती है।

2. होल्ड समय ⏳

होल्ड समय वह न्यूनतम समय है जिसके दौरान डेटा सिग्नल को क्लॉक सिग्नल के ट्रिगरिंग एज के बाद स्थिर रखा जाना चाहिए। सेटअप समय के विपरीत, होल्ड समय आमतौर पर क्लॉक आवृत्ति से स्वतंत्र होता है। इसका निर्धारण फ्लिप-फ्लॉप के आंतरिक देरी और डेटा पथ के बाहरी प्रसारण देरी पर निर्भर करता है।

3. प्रसारण देरी ⏳

यह एक सिग्नल के घटक के इनपुट से आउटपुट तक यात्रा करने में लगने वाला समय है। यह तापमान, वोल्टेज और निर्माण अंतराल पर निर्भर करता है। समय आरेख में, इसे एक सिग्नल में परिवर्तन और दूसरे सिग्नल में उत्पन्न परिवर्तन के बीच की देरी के रूप में दिखाया जाता है।

4. क्लॉक आवधि और आवृत्ति ⏳

क्लॉक आवधि क्लॉक सिग्नल के एक पूर्ण चक्र की अवधि है। आवृत्ति आवधि का व्युत्क्रम है। छोटी आवधि का मतलब है उच्च आवृत्ति, जो तेजी से प्रोसेसिंग की अनुमति देती है, लेकिन सिग्नल स्थिरता के लिए खाई बंद कर देती है।

अक्सर पूछे जाने वाले प्रश्न ❓

इंजीनियर्स को अक्सर ऐसे विशिष्ट परिदृश्यों का सामना करना पड़ता है जो भ्रम पैदा करते हैं। टाइमिंग विश्लेषण से संबंधित सबसे जरूरी प्रश्नों के विस्तृत उत्तर नीचे दिए गए हैं।

प्रश्न: यदि सेटअप समय का उल्लंघन किया जाता है तो क्या होता है? 🛑

जब सेटअप समय की आवश्यकता पूरी नहीं होती है, तो फ्लिप-फ्लॉप एक ऐसी स्थिति में प्रवेश करता है जिसे जाना जाता हैअस्थिरता। इस स्थिति में, आउटपुट तुरंत एक वैध लॉजिक हाई या लो में स्थिर नहीं होता है। बल्कि, यह अनिश्चित समय तक उतार-चढ़ाव कर सकता है या एक मध्यवर्ती वोल्टेज स्तर पर रह सकता है। इससे नीचे के लॉजिक को दूषित मान पढ़ने की संभावना होती है, जिससे सिस्टम त्रुटियां या क्रैश हो सकते हैं। गंभीर मामलों में, अस्थिरता पूरे सर्किट में फैल सकती है, जिससे एक कार्यात्मक विफलता होती है जिसे डीबग करना मुश्किल होता है।

प्रश्न: क्लॉक स्क्यू को कैसे संभालें? 🔄

क्लॉक स्क्यू तब होता है जब क्लॉक सिग्नल विभिन्न घटकों पर अलग-अलग समय पर पहुंचता है। यह विभिन्न पथ लंबाई या लोडिंग अंतर के कारण हो सकता है। स्क्यू को प्रबंधित करने के लिए:

- रूटिंग संतुलन:क्लॉक ट्रेस को समान लंबाई और चौड़ाई के साथ रूट करें।

- बफरिंग:बहुत सारे लोड को समान रूप से ड्राइव करने के लिए क्लॉक बफर का उपयोग करें।

- समय सीमा:सेटअप और होल्ड समय में पर्याप्त लचीलापन रखकर सिस्टम का डिजाइन करें ताकि छोटे स्क्यू विचलनों को स्वीकार किया जा सके।

प्रश्न: सिंक्रोनस और एसिंक्रोनस समय में क्या अंतर है? ⚖️

इसमेंसिंक्रोनस प्रणालियाँ, सभी संचालन एकल घड़ी संकेत द्वारा निर्देशित होते हैं। इन प्रणालियों के समय आरेखों में नियमित, दोहराए जाने वाले घड़ी के किनारे दिखाई देते हैं। इसमेंअसिंक्रोनस प्रणालियाँ, सिग्नल एक वैश्विक घड़ी के बिना क्रियाएँ शुरू करते हैं। इन प्रणालियों के समय आरेखों में घटना-आधारित संक्रमण दिखाई देते हैं, जिनमें सिग्नलों के बीच अंतराल में अधिक भिन्नता होती है। असिंक्रोनस डिज़ाइनों का विश्लेषण करना कठिन होता है, लेकिन विशिष्ट कम शक्ति वाले अनुप्रयोगों में अधिक ऊर्जा कुशल हो सकते हैं।

प्रश्न: जिटर का समय आरेख पर क्या प्रभाव पड़ता है? 📉

जिटर समय में किसी सिग्नल के आदर्श स्थिति से छोटे समय के लिए भिन्नता है। समय आरेख में, इसका प्रभाव घड़ी सिग्नल के किनारों के थोड़ा जल्दी या थोड़ा बाद दिखाई देने के रूप में दिखाई देता है। अत्यधिक जिटर डेटा को कैप्चर करने की प्रभावी खाई को कम कर देता है। यह सेटअप और होल्ड मार्जिन को प्रभावी रूप से संकुचित कर देता है, जिससे समय सीमा के उल्लंघन का जोखिम बढ़ जाता है। उच्च गति वाले इंटरफेस को डेटा अखंडता बनाए रखने के लिए सख्त जिटर नियंत्रण की आवश्यकता होती है।

प्रश्न: क्या मैं घड़ी के बिना समय आरेख पढ़ सकता हूँ? 🕵️

हाँ, लेकिन इसके लिए एक अलग दृष्टिकोण की आवश्यकता होती है। असिंक्रोनस प्रोटोकॉल जैसे I2C या UART हमेशा साझा घड़ी लाइन का उपयोग नहीं करते हैं। इसके बजाय, वे पूर्व निर्धारित बॉड दरों या हैंडशेक सिग्नलों पर निर्भर करते हैं। इन आरेखों में, आपको पल्स चौड़ाई और संक्रमणों के बीच के समय को देखकर डेटा दर का अनुमान लगाना होगा। उदाहरण के लिए, UART में, स्टार्ट बिट की अवधि बाद के डेटा बिट्स के लिए समय निर्धारित करती है।

तरंगरूपों को पढ़ना और समझना 🔍

एक समय आरेख की व्याख्या करने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। रेखाओं को यादृच्छिक रूप से स्कैन करने से अक्सर विवरण छूट जाते हैं। सटीक विश्लेषण के लिए इस प्रक्रिया का पालन करें।

- संदर्भ की पहचान करें: घड़ी सिग्नल या मुख्य नियंत्रण सिग्नल को खोजें। सभी अन्य समय सीमाएँ इसके सापेक्ष होती हैं।

- सक्रिय अवस्थाओं की जाँच करें: यह निर्धारित करें कि सिग्नल सक्रिय उच्च हैं या सक्रिय निम्न हैं। एक निम्न पल्स का अर्थ “सक्रिय” हो सकता है, जबकि उच्च पल्स का अर्थ “अक्रिय” होता है। यह आमतौर पर ब्लॉक आरेखों में पिन नाम पर बुलबुला प्रतीक द्वारा दर्शाया जाता है।

- किनारों के संरेखण का विश्लेषण करें: देखें कि डेटा किनारे घड़ी के किनारों के साथ कहाँ संरेखित हैं। डेटा को आदर्श रूप से घड़ी स्थिर होने पर (उदाहरण के लिए, निम्न चरण) बदलना चाहिए और सक्रिय किनारे के दौरान स्थिर रहना चाहिए।

- निर्भरता का अनुसरण करें: कारण-प्रभाव संबंध का अनुसरण करें। यदि सिग्नल A सिग्नल B को ट्रिगर करता है, तो उनके बीच स्पष्ट देरी होनी चाहिए, जो प्रसारण देरी के अनुरूप हो।

- पल्स चौड़ाई की पुष्टि करें: सुनिश्चित करें कि सक्रिय पल्स इतने चौड़े हैं कि प्राप्त करने वाले घटक द्वारा उन्हें पहचाना जा सके। बहुत संकीर्ण पल्स को शोर के रूप में फ़िल्टर कर दिया जा सकता है।

आरेख व्याख्या में आम गलतियाँ ❌

यहाँ तक कि अनुभवी � ingineers भी विशिष्ट विवरणों को नजरअंदाज करने पर आरेखों की गलत व्याख्या कर सकते हैं। इन आम जाल में फंसने से बचें।

- लॉजिक स्तरों को नजरअंदाज करना: बिना पुष्टि के सभी सिग्नल सक्रिय उच्च मानना। हमेशा डेटाशीट या ब्लॉक आरेख की जाँच करें।

- प्रसारण देरी को नजरअंदाज करना: सिग्नल तुरंत बदल जाते हैं, इसका मानना। वास्तविक दुनिया के घटकों के पास सीमित प्रतिक्रिया समय होता है।

- समय पैमाने को गलत पढ़ना: समय इकाई (नैनोसेकंड बनाम माइक्रोसेकंड) को नोटिस करने में विफलता। एक संकेत जो धीमी जूम पर स्थिर लगता है, तेज जूम पर ग्लिच दिखा सकता है।

- पावर अवस्थाओं को नजरअंदाज करना: समय आरेख अक्सर उपकरण स्लीप मोड में प्रवेश करने पर बदल जाते हैं। सुनिश्चित करें कि आप सक्रिय समय अनुक्रम को देख रहे हैं।

सटीक विश्लेषण के लिए रणनीतियाँ 🛠️

अपने समय विश्लेषण को मजबूत बनाने के लिए, इन रणनीतियों को अपनाएं। इन विधियों में संस्थिरता बनाए रखने और त्रुटि के संभावना को कम करने में मदद मिलती है।

- ग्रिड लाइन्स का उपयोग करें:समय अंतराल को सटीक रूप से मापने के लिए आरेख पर ग्रिड लाइन्स के साथ अपने कर्सर या मार्कर को संरेखित करें।

- मान्यताओं को दस्तावेज़ित करें:विश्लेषण शुरू करने से पहले मानी गई घड़ी आवृत्ति और तर्क स्तरों को लिखें। इससे बाद में भ्रम से बचा जा सकता है।

- प्रतिस्थापन संदर्भ:समय आरेख की अवस्था मशीन तर्क के साथ तुलना करें। प्रत्येक अवस्था संक्रमण के लिए एक संगत समय घटना होनी चाहिए।

- परिवर्तनों का सिमुलेशन करें:सबसे खराब स्थितियों को ध्यान में रखें। यदि तापमान बढ़ता है और देरी बढ़ती है तो क्या होता है? यदि वोल्टेज घटता है और ड्राइव ताकत कम होती है तो क्या होता है?

- महत्वपूर्ण मार्गों पर ध्यान केंद्रित करें:अपनी तर्क में सबसे लंबे मार्ग की पहचान करें। यह मार्ग प्रणाली की अधिकतम घड़ी गति निर्धारित करता है। इन विशिष्ट मार्गों के लिए समय विश्लेषण को प्राथमिकता दें।

समय उल्लंघनों का प्रभाव ⚠️

समय के महत्व को समझना निर्णायक है। जब समय उल्लंघन होता है, तो परिपथ का भौतिक व्यवहार बदल जाता है। सबसे आम परिणाम डेटा क्षति है। एक रजिस्टर एक ‘1’ को पकड़ सकता है जबकि उसे ‘0’ को पकड़ना चाहिए था। संचार प्रोटोकॉल में, इसके परिणामस्वरूप फ्रेमिंग त्रुटियाँ या खोए हुए पैकेट हो सकते हैं। नियंत्रण प्रणालियों में, यह गलत एक्चुएटर आदेशों की ओर जा सकता है, जिससे भौतिक क्षति या सुरक्षा खतरे का खतरा हो सकता है।

इसके अलावा, समय उल्लंघन अस्थायी विफलताओं का कारण बन सकते हैं। एक प्रणाली कमरे के तापमान पर पूरी तरह से काम कर सकती है, लेकिन गर्म होने पर विफल हो सकती है। ऐसा इसलिए होता है क्योंकि प्रसारण देरी तापमान के साथ बढ़ती है। पर्याप्त समय अंतराल के साथ डिज़ाइन करने से इन पर्यावरणीय परिवर्तनों को ध्यान में रखा जा सकता है।

समय आरेखों के लिए श्रेष्ठ व्यवहार 📝

स्पष्ट और सटीक समय आरेख बनाना एक कौशल है जो अभ्यास के साथ बेहतर होता है। दूसरों के लिए समझने में आसान आरेख बनाने के लिए इन दिशानिर्देशों का पालन करें।

- सब कुछ लेबल करें: प्रत्येक सिग्नल लाइन का स्पष्ट नाम होना चाहिए। “Signal 1” जैसे सामान्य लेबल से बचें।

- स्थिर प escala का उपयोग करें: पूरे आरेख में एक समान समय पैमाना बनाए रखें, जब तक कि आप किसी विशिष्ट घटना पर ज़ूम नहीं करना चाहते।

- महत्वपूर्ण घटनाओं को उजागर करें: सेटअप और होल्ड विंडो को चिह्नित करने के लिए अलग-अलग रंग या मोटी रेखाओं का उपयोग करें।

- टिप्पणियाँ शामिल करें: जटिल बातचीत या विशिष्ट सीमाओं को समझाने के लिए पाठ नोट जोड़ें।

- डेटा शीट्स के साथ सत्यापित करें: हमेशा अपने आरेख के पैरामीटर्स की आधिकारिक घटक विशिष्टताओं के साथ तुलना करें।

उन्नत Pertimbangan: बहु-घड़ी क्षेत्र 🌐

आधुनिक प्रणालियाँ अक्सर बहु-घड़ी क्षेत्रों का उपयोग करती हैं। उदाहरण के लिए, एक प्रोसेसर 2 GHz पर चल सकता है जबकि मेमोरी कंट्रोलर 400 MHz पर चलता है। इन प्रणालियों के लिए समय आरेख बहुत अधिक जटिल हो जाते हैं। आपको ध्यान देना होगा:

- क्रॉस-घड़ी नमूनाकरण: एक आवृत्ति से दूसरी आवृत्ति में डेटा कैसे आगे बढ़ता है।

- FIFO बफर: असिंक्रोनस क्लॉक्स के बीच डेटा प्रवाह को समकालीन करने का तरीका।

- रीसेट समकालीनता: सभी डोमेन को एक समन्वित तरीके से रीसेट करने का ध्यान रखना ताकि अवस्था असंगतियाँ न हों।

इन आरेखों के विश्लेषण के समय, हैंडशेक सिग्नल या सिंक्रोनाइज़र श्रृंखला जैसे समकालीनता तर्क की तलाश करें। इन घटकों को विभिन्न समय सीमा के बीच अंतर को सुरक्षित ढंग से पार करने के लिए विशेष रूप से डिज़ाइन किया गया है।

निष्कर्ष: सटीकता महत्वपूर्ण है 🔑

समय आरेख केवल चित्रों से अधिक हैं; वे कार्यकारी प्रणाली का गणितीय सबूत हैं। वे विश्वसनीयता और प्रदर्शन की सीमाओं को परिभाषित करते हैं। मूल घटकों, पैरामीटरों और संभावित त्रुटियों को समझकर आप वास्तविक दुनिया की स्थितियों में सही तरीके से काम करने वाली प्रणालियों को डिज़ाइन कर सकते हैं। सेटअप समय, होल्ड समय और प्रसारण देरी पर ध्यान देना एक कार्यात्मक प्रोटोटाइप और उत्पादन तैयार उत्पाद के बीच अंतर बनाता है। इन आरेखों को पढ़ने और बनाने में निरंतर अभ्यास आपकी तकनीकी अनुभूति को तेज करेगा और आपके इंजीनियरिंग परिणामों में सुधार करेगा।

याद रखें कि प्रत्येक किनारा सूचना के प्रवाह के बारे में एक कहानी बताता है। उस सूचना के यात्रा करने में लगने वाले समय का सम्मान करें, और आपके डिज़ाइन समय के परीक्षण में खड़े रहेंगे।