डिजिटल सिस्टम की जटिल संरचना में, सिग्नल के अवस्था बदलने के सटीक क्षण को समझना महत्वपूर्ण है। समय आरेख सिग्नलों के समय के साथ विकास का दृश्य प्रतिनिधित्व प्रदान करते हैं। इंजीनियरों, विकासकर्ताओं और डिजाइनरों के लिए ये आवश्यक उपकरण हैं जिन्हें यह सत्यापित करने की आवश्यकता होती है कि घटक सही तरीके से बातचीत कर रहे हैं। इन दृश्य सहायताओं के बिना, असमान समय संचार का निराकरण या क्लॉक डोमेन की पुष्टि करना एक अनुमान खेल बन जाता है। यह मार्गदर्शिका सिस्टम डिजाइन में समय आरेखों के यांत्रिकी, लाभ और अनुप्रयोगों का अध्ययन करती है।

समय आरेख क्या है? ⚙️

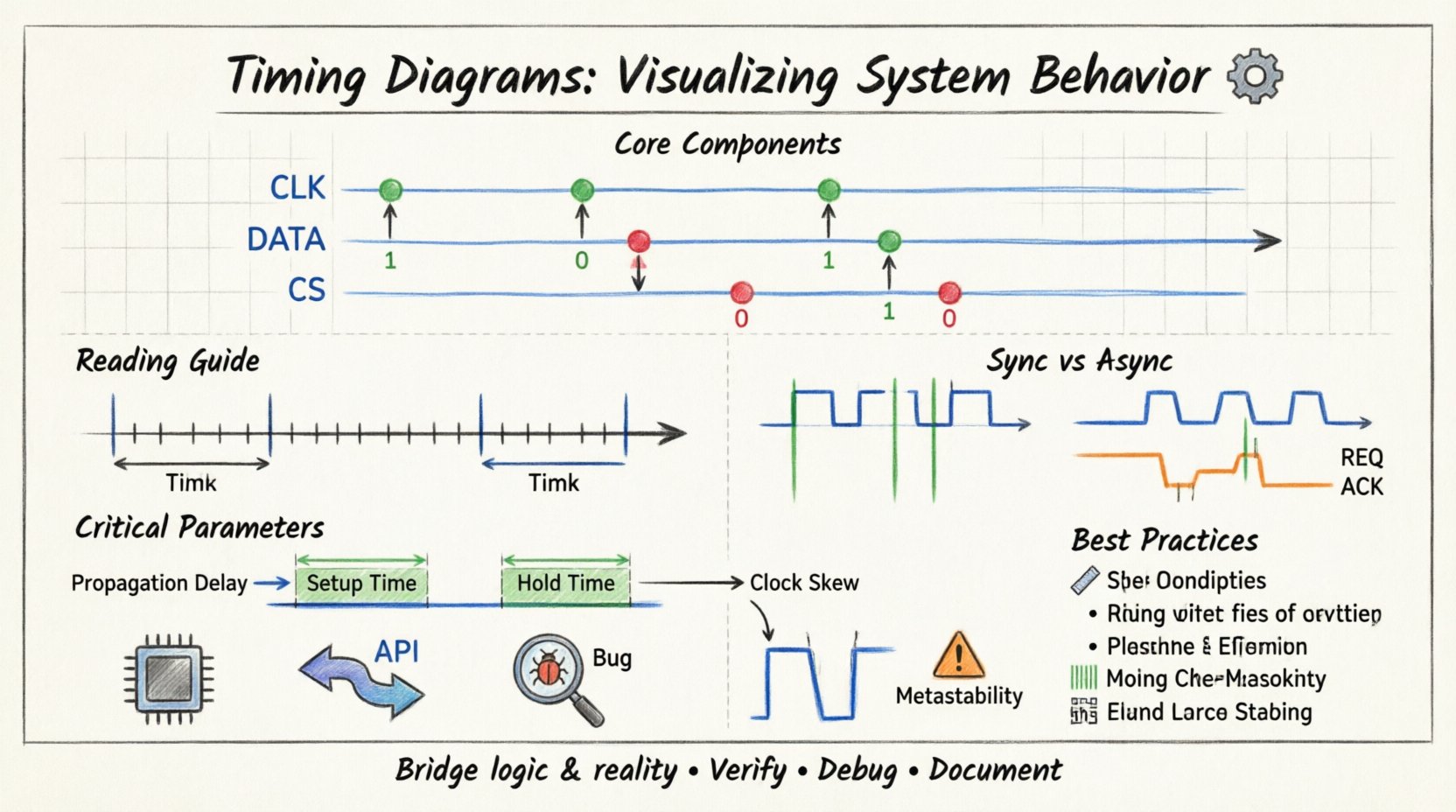

एक समय आरेख एक ग्राफ है जो किसी अवधि के दौरान सिग्नलों के व्यवहार को दिखाता है। यह सिग्नलों की तार्किक अवस्था को समय रेखा के साथ मैप करता है। सर्किट आरेखों के विपरीत जो भौतिक जुड़ाव दिखाते हैं, समय आरेख घटनाओं के बीच समय संबंध पर ध्यान केंद्रित करते हैं। वे प्रश्नों के उत्तर देते हैं जैसे: क्या सिग्नल A सिग्नल B से पहले बदलता है? क्लॉक पल्स पर्याप्त चौड़ा है? डेटा को स्थिर होने में कितना समय लगता है?

इन आरेखों का मूलभूत महत्व है:

- हार्डवेयर प्रोटोकॉल की पुष्टि करना

- सॉफ्टवेयर तर्क अंतरक्रियाओं का दस्तावेजीकरण

- रेस कंडीशन का निराकरण

- क्लॉक और डेटा संरेखण की पुष्टि करना

समय आरेख के मूल घटक 🧩

एक समय आरेख को प्रभावी ढंग से समझने के लिए, उसके निर्माण तत्वों को समझना आवश्यक है। प्रत्येक आरेख विशिष्ट तत्वों से मिलकर बना होता है जो सिस्टम के संचालन के बारे में जानकारी प्रदान करते हैं।

1. समय अक्ष 📏

क्षैतिज अक्ष समय का प्रतिनिधित्व करता है। यह आमतौर पर बाएं से दाएं बहता है। पैमाना निरपेक्ष (नैनोसेकंड, माइक्रोसेकंड) या सापेक्ष (क्लॉक चक्कर) हो सकता है। सिंक्रोनस सिस्टम में, समय को आमतौर पर क्लॉक किनारों के अनुरूप अलग-अलग चरणों में विभाजित किया जाता है।

2. सिग्नल लाइनें 📡

प्रत्येक लाइन एक विशिष्ट सिग्नल, तार या डेटा बस का प्रतिनिधित्व करती है। इन लाइनों को नामों के साथ लेबल किया जाता है जैसेCLK, डेटा, CS (चिप चयन), याRST (रीसेट)। लाइन की ऊर्ध्वाधर स्थिति विभिन्न सिग्नलों को बाधित करने से बचाने के लिए अलग करती है।

3. तार्किक स्तर 🟢🔴

सिग्नल आमतौर पर अलग-अलग अवस्थाओं में मौजूद होते हैं। डिजिटल तर्क में, ये उच्च (तार्किक 1) और निम्न (तार्किक 0) होते हैं। समय आरेख इन अवस्थाओं के बीच संक्रमण को दिखाते हैं। निम्न से उच्च की ओर संक्रमण एक उत्थान किनारा है। उच्च से निम्न की ओर संक्रमण एक गिरावट किनारा है।

4. घटनाएं और संक्रमण 🔄

घटनाएं वे विशिष्ट क्षण हैं जहां एक सिग्नल की अवस्था बदलती है। इन्हें अक्सर ऊर्ध्वाधर रेखाओं या तीरों द्वारा चिह्नित किया जाता है। महत्वपूर्ण घटनाओं में क्लॉक किनारे, डेटा लॉक्स और स्वीकृति सिग्नल शामिल हैं। इन घटनाओं के बीच की दूरी अवधि को दर्शाती है।

समय आरेखों को प्रभावी ढंग से पढ़ना 👁️

इन आरेखों को पढ़ने के लिए एक व्यवस्थित दृष्टिकोण की आवश्यकता होती है। घटनाओं के क्रम के गलत व्याख्या करने से डिजाइन की कमियां हो सकती हैं। सटीकता सुनिश्चित करने के लिए इन नियमों का पालन करें।

- बाएं से दाएं: हमेशा टाइमलाइन को शुरू से (बाएं) अंत तक (दाएं) पढ़ें। इससे संचालन के क्रमागत प्रवाह का प्रतिनिधित्व होता है।

- ऊर्ध्वाधर संरेखण: ऊर्ध्वाधर रूप से संरेखित घटनाएँ एक साथ होती हैं। यदि दो सिग्नल एक ही ऊर्ध्वाधर रेखा पर बदलते हैं, तो वे समकालिक होते हैं।

- अवधि: सिग्नल स्थिति की क्षैतिज लंबाई इस बात को दर्शाती है कि यह कितनी देर तक उस स्थिति में रहता है। एक चौड़ा पल्स लंबी अवधि का अर्थ है।

- निर्भरताएँ: कारण और प्रभाव की तलाश करें। एक सिग्नल के बदलाव के दूसरे को ट्रिगर करने की संभावना होती है। आरेख इन ट्रिगर्स के बीच लेटेंसी को दर्शाता है।

सिंक्रोनस बनाम एसिंक्रोनस प्रणाली 🔄

समय आरेख यह बताने पर बहुत अंतर दिखाते हैं कि क्या प्रणाली सिंक्रोनस है या एसिंक्रोनस। सही विश्लेषण के लिए इस अंतर को समझना आवश्यक है।

सिंक्रोनस प्रणाली ⏰

इन प्रणालियों का एक वैश्विक घड़ी सिग्नल पर निर्भरता होती है। सभी अवस्था परिवर्तन विशिष्ट घड़ी के किनारों (उत्थान या अवनति) पर होते हैं। आरेख में नियमित घड़ी पैटर्न दिखाया जाएगा। डेटा केवल तभी सैंपल किया जाता है जब घड़ी अनुमति देती है। इससे समय निर्धारित होता है, लेकिन सेटअप और होल्ड समय जैसी सीमाएँ भी आती हैं।

एसिंक्रोनस प्रणाली 🕰️

इन प्रणालियों का वैश्विक घड़ी पर निर्भर नहीं होता है। अवस्था परिवर्तन तब होते हैं जब इनपुट सिग्नल बदलते हैं। यहाँ समय आरेख कम नियमित लगते हैं। इनका ध्यान हैंडशेक प्रोटोकॉल पर होता है। एक सिग्नल को ऊपर जाना चाहिए, फिर दूसरा, फिर वापस नीचे। इसके लिए देरी के ध्यान से विश्लेषण की आवश्यकता होती है ताकि रेस कंडीशन से बचा जा सके।

समय विश्लेषण में महत्वपूर्ण पैरामीटर ⚙️

केवल रेखाएँ खींचने से आगे, इंजीनियर विशिष्ट पैरामीटरों का विश्लेषण करते हैं ताकि विश्वसनीयता सुनिश्चित हो सके। इन पैरामीटरों द्वारा वह खंड निर्धारित किया जाता है जिसमें प्रणाली सही तरीके से काम करती है।

- प्रसारण देरी: एक सिग्नल के घटक के माध्यम से इनपुट से आउटपुट तक यात्रा करने में लगने वाला समय। यह देरी लॉजिक गेट्स के माध्यम से जमा होती है।

- सेटअप समय: घड़ी के किनारे से पहले डेटा के स्थिर रहने का न्यूनतम समय। यदि डेटा बहुत देर से बदलता है, तो फ्लिप-फ्लॉप इसे सही तरीके से कैप्चर नहीं कर पाएगा।

- होल्ड समय: घड़ी के किनारे के बाद डेटा के स्थिर रहने का न्यूनतम समय। यदि डेटा बहुत जल्दी बदलता है, तो वर्तमान मान खो जाता है।

- घड़ी विचलन: विभिन्न घटकों पर घड़ी सिग्नल के आगमन समय का अंतर। उच्च विचलन सेटअप या होल्ड उल्लंघन का कारण बन सकता है।

- मेटास्टेबिलिटी: एक ऐसी स्थिति जहाँ फ्लिप-फ्लॉप आउटपुट न तो उच्च है और न ही निम्न। यह तब होता है जब सेटअप या होल्ड समय का उल्लंघन होता है। समय आरेख मेटास्टेबिलिटी के जोखिम को दृश्यमान करने में मदद करते हैं।

हार्डवेयर और सॉफ्टवेयर में अनुप्रयोग 🔌

समय आरेख केवल हार्डवेयर तक सीमित नहीं हैं। इनका उपयोग सॉफ्टवेयर आर्किटेक्चर और प्रोटोकॉल डिजाइन में भी व्यापक रूप से किया जाता है।

हार्डवेयर डिजाइन

हार्डवेयर में, इन आरेखों का उपयोग बस प्रोटोकॉल के अनुरूपता के लिए किया जाता है। उदाहरण के लिए, पढ़ने के स्ट्रोब के सक्रिय होने से पहले एड्रेस बस के स्थिर रहने की जांच करना। यह सुनिश्चित करते हैं कि मेमोरी एक्सेस समय प्रोसेसर की घड़ी गति के अनुरूप हो। इनका उपयोग सिग्नल संक्रमण के दौरान शक्ति उपभोग के शिखर के विश्लेषण के लिए भी किया जाता है।

सॉफ्टवेयर और प्रोटोकॉल

सॉफ्टवेयर में, समय आरेख एपीआई कॉल या संदेश आदान-प्रदान को मैप करते हैं। वे सेवाओं के बीच अनुरोधों और प्रतिक्रियाओं के क्रम को दिखाते हैं। इससे वितरित प्रणालियों में लेटेंसी समस्याओं की पहचान में मदद मिलती है। वे बहु-थ्रेडेड वातावरणों में क्रियाओं के क्रम को स्पष्ट करते हैं।

आम गलतियाँ और त्रुटियाँ 🛑

समय आरेख बनाने या पढ़ने में ध्यान न देने पर त्रुटियाँ हो सकती हैं। आम गलतियों के बारे में जागरूक रहने से सटीकता में सुधार होता है।

- एक्टिव लो को नजरअंदाज करना: बहुत से सिग्नल एक्टिव-लो लॉजिक (उल्टा) का उपयोग करते हैं। एक लाइन के लो पर गिरने का मतलब हो सकता है कि सिग्नल सक्रिय है। हमेशा लेजेंड या लेबल चेक करें।

- तत्काल संक्रमण की धारणा करना: वास्तविक सिग्नल में राइज और फॉल टाइम होते हैं। आदर्श आरेख में ऊर्ध्वाधर रेखाएँ दिखाई जाती हैं, लेकिन भौतिक सिग्नल ढलान वाले होते हैं। इस ढलान का सिग्नल अखंडता पर प्रभाव पड़ता है।

- ग्लिचेस को नजरअंदाज करना: छोटे पल्स जो न्यूनतम चौड़ाई की आवश्यकता पूरी नहीं करते हैं, गलत ट्रिगर का कारण बन सकते हैं। इन्हें अक्सर ग्लिचेस कहा जाता है।

- हाई-जी का गलत अर्थ निकालना: हाई-इम्पीडेंस स्थिति का मतलब है कि सिग्नल अलग है। आरेखों में इसे डैश की लाइन या एक विशिष्ट प्रतीक के रूप में दिखाया जाता है। इसकी उपेक्षा करने से बस कंटेंशन त्रुटियाँ हो सकती हैं।

- गलत क्लॉक अनुरूपता: यह मान लेना कि सभी क्लॉक फेज-अलाइन्ड हैं, जबकि ऐसा नहीं है। स्क्यू डेटा के गलत नमूनाकरण का कारण बन सकता है।

आरेख प्रकारों की तुलना 📊

विभिन्न संदर्भों के लिए विभिन्न दृश्य प्रस्तुति विधियाँ आवश्यक होती हैं। जबकि समय आरेख शक्तिशाली हैं, वे एकमात्र उपकरण नहीं हैं।

| आरेख प्रकार | प्राथमिक फोकस | सबसे अच्छा उपयोग किया जाता है |

|---|---|---|

| समय आरेख | समय और सिग्नल अवस्थाएँ | क्लॉक/डेटा संबंधों की पुष्टि करना |

| अवस्था आरेख | प्रणाली की अवस्थाएँ | तर्क प्रवाह और शर्तों को परिभाषित करना |

| अनुक्रम आरेख | संदेश क्रम | सॉफ्टवेयर अंतरक्रियाएँ और एपीआई कॉल |

| परिपथ आरेख | भौतिक कनेक्शन | वायरिंग और घटक व्यवस्था |

| तरंग आकृति दर्शक | रियल-टाइम सिग्नल | वास्तविक हार्डवेयर व्यवहार का डीबगिंग |

दस्तावेज़ीकरण के लिए सर्वोत्तम प्रथाएँ 📝

टीमों और भविष्य के संदर्भ के लिए समय आरेखों को उपयोगी बनाने के लिए, इन सर्वोत्तम प्रथाओं का पालन करें। स्पष्ट दस्तावेज़ीकरण अस्पष्टता को कम करता है और डीबगिंग को तेज करता है।

- सब कुछ लेबल करें: प्रत्येक सिग्नल लाइन का स्पष्ट नाम होना चाहिए। सामान्य लेबल जैसे कि सिग1.

- इकाइयाँ शामिल करें: अक्ष पर समय की इकाइयाँ निर्दिष्ट करें। क्या हम मिलीसेकंड या क्लॉक साइकिल्स को देख रहे हैं?

- महत्वपूर्ण बिंदुओं को चिह्नित करें: सेटअप और होल्ड विंडो को स्पष्ट रूप से हाइलाइट करें। महत्वपूर्ण समय विंडो को चिह्नित करने के लिए छायांकन या अलग-अलग रंगों का उपयोग करें।

- इसे व्यवस्थित रखें: संबंधित सिग्नलों को एक साथ समूहित करें। उदाहरण के लिए, सभी नियंत्रण सिग्नल ऊपर, डेटा सिग्नल नीचे।

- मान्यताओं को दस्तावेज़ीकृत करें: निर्माण के दौरान बनाई गई किसी भी मान्यता को नोट करें। उदाहरण के लिए, शून्य प्रसारण देरी या विशिष्ट लोड स्थितियों को मान लें।

- संगत नोटेशन का उपयोग करें: बढ़ते किनारों, गिरते किनारों और उच्च प्रतिरोध अवस्थाओं के लिए मानक प्रतीकों का पालन करें।

आरेख बनाने के लिए चरण-दर-चरण मार्गदर्शिका 🛠️

शुरुआत से एक समय आरेख बनाने के लिए एक संरचित दृष्टिकोण की आवश्यकता होती है। पूर्णता सुनिश्चित करने के लिए इन चरणों का पालन करें।

- सिग्नल पहचानें: बातचीत में शामिल सभी इनपुट और आउटपुट की सूची बनाएं।

- क्रम निर्धारित करें: घटनाओं के क्रम को परिभाषित करें। प्रक्रिया को क्या ट्रिगर करता है?

- समय पैमाना सेट करें: समय अक्ष की विस्तृतता का निर्णय लें।

- घड़ी खींचें: यदि समकालिक है, तो सबसे पहले घड़ी सिग्नल खींचें। यह आरेख के बाकी हिस्से को स्थिर करता है।

- डेटा जोड़ें: क्लॉक किनारों के संबंध में डेटा सिग्नल को आलेखित करें।

- प्रतिबंधों की जांच करें: आलेखित सिग्नलों के विरुद्ध सेटअप और होल्ड समय की पुष्टि करें।

- समीक्षा: कोई तार्किक अंतराल न हो, इसकी गारंटी देने के लिए समय रेखा के माध्यम से चलें।

डिबगिंग में समय की भूमिका 🐞

जब कोई प्रणाली विफल होती है, तो समय आरेख अक्सर इंजीनियरों की पहली जांच की जगह होती है। वे यह निर्धारित करने में मदद करते हैं कि समस्या तार्किक है या समय संबंधी। यदि तर्क सही है लेकिन समय गलत है, तो प्रणाली अस्थायी रूप से विफल हो जाती है। यह एक कठिन तार्किक त्रुटि की तुलना में अक्सर अधिक कठिन होती है।

डिबगिंग परिदृश्य में शामिल हैं:

- डेटा क्षति: पढ़े जा रहे सिग्नल में बदलाव हो रहा है।

- छूटे हुए इंटरप्ट: एक इंटरप्ट सिग्नल जो इतना छोटा है कि पहचाना नहीं जा सकता।

- बस प्रतिस्पर्धा: दो उपकरण एक साथ बस को ड्राइव कर रहे हैं।

- क्लॉक डोमेन क्रॉसिंग: उचित समन्वय के बिना विभिन्न क्लॉक आवृत्तियों के बीच सिग्नल चल रहे हैं।

डेटा चौड़ाई और संरेखण को समझना 📐

समय आरेख डेटा चौड़ाई को भी दर्शाते हैं। समानांतर बस के लिए कई लाइनों की आवश्यकता होती है। प्रत्येक लाइन को समकालीन रूप से संक्रमण करना चाहिए। असंरेखण डेटा त्रुटियों का कारण बन सकता है। आरेख एक क्लॉक चक्र के भीतर बिट्स के संरेखण को दिखाता है। श्रृंखला संचार के लिए, समय आरेख बिट स्ट्रीम को दिखाता है। यह बिट अवधि और नमूना बिंदु को उजागर करता है।

उन्नत विषय: जिटर और शोर 📉

वास्तविक दुनिया के सिग्नल पूर्ण नहीं होते हैं। जिटर क्लॉक किनारे के आदर्श स्थान से विचलन है। शोर सिग्नल स्तर में यादृच्छिक उतार-चढ़ाव है। समय आरेख एक तीक्ष्ण रेखा के बजाय किनारे के चारों ओर एक मोटी पट्टी दिखाकर जिटर का प्रतिनिधित्व कर सकते हैं। इससे अनिश्चितता का संकेत मिलता है। डिजाइनरों को यह सुनिश्चित करना चाहिए कि प्रणाली इस अनिश्चितता को सहन कर सके। जिटर पट्टी और सेटअप/होल्ड विंडो के बीच का अंतर सुरक्षा सीमा है।

परीक्षण सूट्स के साथ एकीकरण 🧪

समय आरेख केवल डिजाइन के लिए नहीं होते हैं। इनका उपयोग परीक्षण मामलों के उत्पादन के लिए किया जाता है। स्वचालित परीक्षण सूट्स यह जांच सकते हैं कि वास्तविक प्रणाली का व्यवहार आरेख के अनुरूप है या नहीं। यदि मापी गई समय सीमा सहिष्णुता से बाहर हो जाती है, तो परीक्षण असफल हो जाता है। इससे यह सुनिश्चित होता है कि हार्डवेयर या सॉफ्टवेयर अपने जीवनचक्र के दौरान निर्देशों को पूरा करता है।

प्रणाली दृश्यीकरण पर निष्कर्ष 🎯

समय आरेख प्रणाली � ingineering का एक मूल बिंदु बने रहते हैं। वे अमूर्त तर्क और भौतिक वास्तविकता के बीच के अंतर को पार करते हैं। समय और सिग्नल के प्रवाह को दृश्याकरण करके, इंजीनियर विफलताओं की भविष्यवाणी कर सकते हैं। वे हार्डवेयर और सॉफ्टवेयर टीमों के बीच संचार को सुगम बनाते हैं। एक अच्छी तरह से बनाया गया आरेख पृष्ठों भर टेक्स्ट से अधिक जानकारी प्रसारित करता है। जैसे-जैसे प्रणालियां तेज और अधिक जटिल होती हैं, सटीक समय विश्लेषण की आवश्यकता बढ़ती है। इन आरेखों के निपुणता से दृढ़ और विश्वसनीय डिजाइन सुनिश्चित होते हैं।

स्पष्टता और सटीकता को प्राथमिकता देने की याद रखें। मान्यताओं से बचें। प्रत्येक संक्रमण की पुष्टि करें। अभ्यास के साथ, इन आरेखों को पढ़ना और बनाना डिजाइन प्रक्रिया का एक स्वाभाविक हिस्सा बन जाता है। वे डिजिटल तर्क के भूदृश्य में यात्री को मार्गदर्शन करने वाला नक्शा हैं।