デジタル電子工学およびシステム設計の複雑な世界において、部品間の通信は正確な時間的関係に大きく依存しています。タイミング図は、これらの関係を説明する視覚的な言語として機能します。これは信号の時間的変化を示すグラフィカルな表現です。このツールがなければ、ハードウェアの相互作用のデバッグや論理動作の検証はほぼ不可能です。このガイドでは、これらの図を効果的に解釈するために必要な基本的な要素、パラメータ、読み取り戦略について探求します。

そもそもタイミング図とは何か? 📐

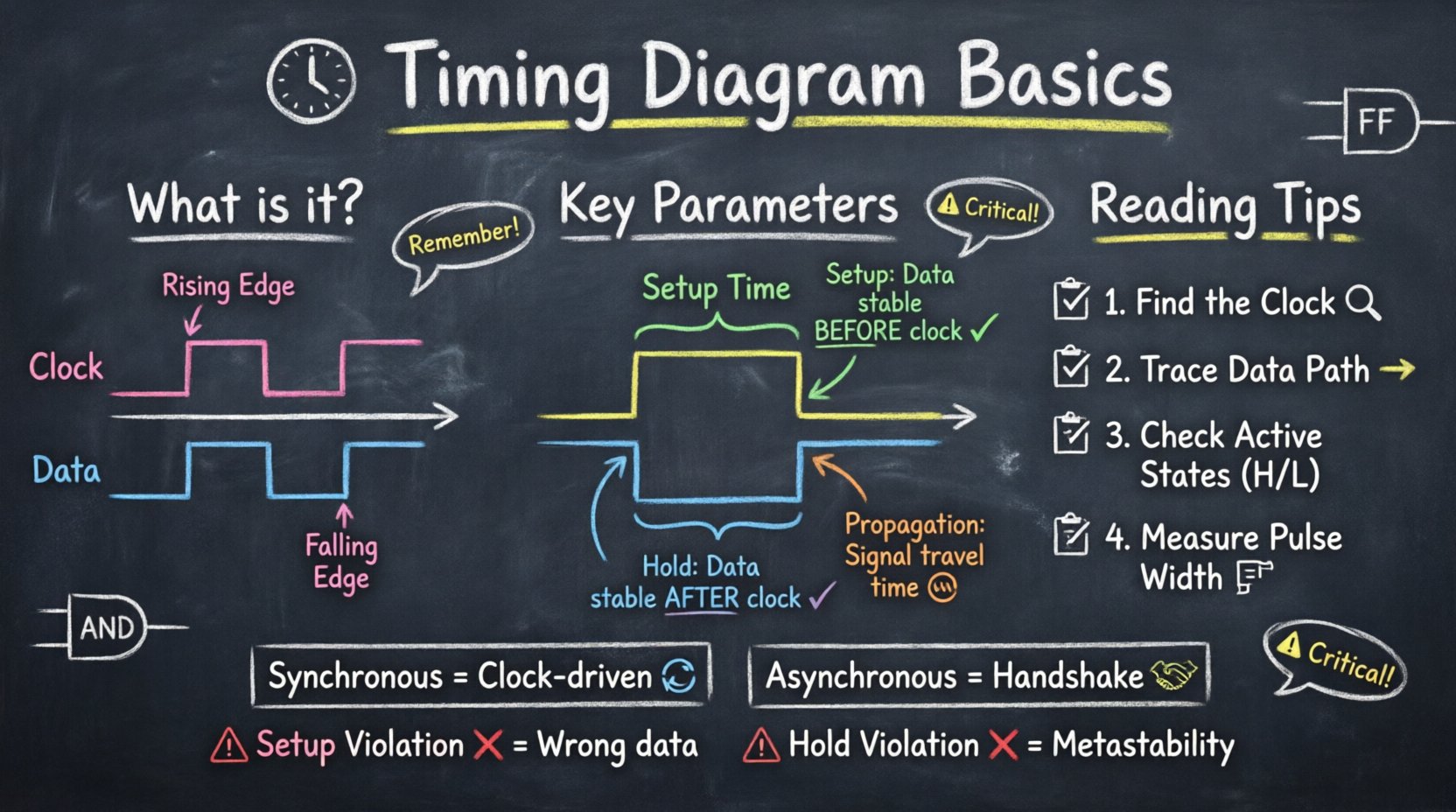

タイミング図は、定義された期間内における2つ以上の信号間の関係を示すために使用される特定の種類のグラフです。論理状態テーブルのようにグリッドに状態をリストアップするのではなく、タイミング図はこれらの状態を水平方向の時間軸上にマッピングします。この視覚的なアプローチにより、エンジニアはイベントの順序、パルスの持続時間、回路の異なる部分間の同期を把握できます。

これらの図は、いくつかの文脈において不可欠です:

- ハードウェア設計:クロックエッジが到着する前にデータが安定していることを確認するため。

- プロトコル解析:I²C、SPI、UARTなどの通信規格を理解するため。

- システム検証:ラス条件が発生しないように、ステートマシンが正しく遷移することを確認するため。

- デバッグ:システム障害を引き起こすセットアップまたはホールド違反を特定するため。

タイミングを視覚化することで、設計者は負荷下でのシステムの挙動を予測でき、信頼性と性能を確保できます。

タイミング図の核心的な要素 🎯

タイミング図を読むには、まずその基本的な構成要素を理解する必要があります。すべての図は信号、時間、遷移から構成されています。これらの要素の配置は、システムの電気的挙動について物語を語っています。

信号とライン

各水平線は特定の信号を表します。これはクロック信号、データライン、アドレスバス、または制御フラグである可能性があります。信号は通常、ラインの開始部または凡例にラベルが付けられます。ラインの垂直位置は電圧レベルを示すものではなく、基準線に対する垂直位置が論理状態を示します。

時間軸

水平軸は時間を表します。左から右へと流れます。多くの図では、時間間隔が垂直の破線でマークされています。これらのマーカーはしばしばクロックサイクルに対応します。時間スケールが常に線形であるとは限らないことに注意が必要です。場合によっては、特定の瞬間が拡大され、マイクロ秒やナノ秒の詳細が表示される一方、他の部分はマクロレベルの挙動を示すことがあります。

論理レベル

信号は通常、2つの状態(HighとLow)の間で切り替わります。これらはバイナリの1と0に対応します。一部の文脈では、Lowがアクティブ状態(アクティブロー)を表す場合があり、Highがアクティブ状態(アクティブハイ)を表す場合もあります。リセットやチップセレクトなどの制御信号を解釈するには、アクティブ状態を理解することが不可欠です。

遷移とエッジ

論理レベルをつなぐ垂直線は遷移を表します。主なエッジには2種類あります:

- リジングエッジ:LowからHighへの遷移。

- フェールイングエッジ:HighからLowへの遷移。

これらのエッジは、デジタル回路で動作をトリガーすることが多いです。たとえば、レジスタはクロック信号が立ち上がる瞬間にデータを更新する場合があります。

重要なタイミングパラメータ ⚙️

静的ラインを理解することは、戦いの半分にすぎません。動的パラメータは、システムが動作しなければならない制約を定義しています。これらのパラメータを違反すると、データ破損やシステムクラッシュが発生します。

セットアップ時間

セットアップ時間は、クロックエッジの前にデータ信号が安定して有効である必要がある最小時間です。データがクロックエッジに近すぎるように変化すると、受信回路が正しい値を登録するのに十分な時間が確保できない場合があります。このパラメータは同期システムでは厳格に遵守されます。

ホールド時間

ホールド時間は、クロックエッジの後にデータ信号が安定したまま維持される必要がある最小時間です。クロックがキャプチャをトリガーした後でも、データはすぐに変化してはいけません。速すぎると、内部のラッチやフリップフロップが不安定な状態に入ることがあります。

プロパゲーション遅延

プロパゲーション遅延は、信号がコンポーネントの入力から出力まで到達するまでの時間です。これは回路の物理的特性に固有のものです。複数のコンポーネントが連接されている場合、これらの遅延は累積され、システムの最大動作周波数に影響を与えます。

クロックサイクルと周波数

クロックサイクルは、クロック信号の1つの完全な周期の持続時間です。周波数はこの周期の逆数であり、ヘルツ(Hz)で測定されます。システムのタイミング予算はしばしばクロック周期によって定義されます。すべてのプロパゲーション遅延の合計がクロック周期を超えると、システムは正しく動作しなくなります。

| パラメータ | 定義 | 違反の影響 |

|---|---|---|

| セットアップ時間 | クロックエッジの前にデータが安定している時間 | データの欠落または誤ったキャプチャ |

| ホールド時間 | クロックエッジの後にデータが安定している時間 | メタスタビリティまたはデータ破損 |

| プロパゲーション遅延 | 信号が論理回路を通過する時間 | 最大周波数の低下またはタイミングエラー |

| スキュー | クロック信号の到着時間の差 | タイミングマージンの低下 |

| ジッター | 信号タイミングの短期的な変動 | 高速での不安定な動作 |

信号の読み取りと解析 📖

タイミング図の解釈には体系的なアプローチが必要です。視覚情報に急いで対応すると、システムの動作を誤解する原因になります。正確に図を分析するには、以下の手順に従ってください。

- クロックを特定する: システムを駆動する周期信号を特定してください。これは通常、他のすべての動作の基準となります。

- データパスをたどる:信号線をソースから宛先までたどります。データが生成される場所と消費される場所をメモしてください。

- アクティブ状態を確認する:信号がアクティブハイかアクティブロウかを確認します。ロウ信号は「有効」を意味する場合があり、ハイ信号は「無効」を意味する場合があります。

- 持続時間を測定する:パルスの幅を確認してください。パルスは検出可能に十分な幅を持っていますか?ノイズ(ゴースト)である可能性があるほど狭いでしょうか?

- シーケンスを検証する:コントロール信号が正しい順序で変化していることを確認してください。たとえば、システムが処理を開始する前にリセット信号をアサートする必要があります。

複雑な図を分析する際には、タイムラインを離散的なサイクルに分割すると役立ちます。1つのクロック周期ずつ分析することで、状態遷移を理解できます。

同期型と非同期型システム 🔄

タイミング図は、システムが同期型か非同期型かによって大きく異なります。この違いを理解することは、正しい解釈に不可欠です。

同期型システム

同期型システムでは、すべての操作がグローバルクロックによって調整されます。状態の変化はすべてクロックエッジに対して発生します。これによりタイミング解析がより予測可能になります。2つのレジスタ間の最長パスの遅延を合計することで、システムの最大速度を計算できます。ここでのタイミング図は非常に規則的で、イベントがクロックエッジと垂直に揃っています。

非同期型システム

非同期型システムはグローバルクロックに依存しません。代わりに、前の段階が準備ができたら信号が状態を変えるハンドシェイキングプロトコルを使用します。これらのシステムのタイミング図は、より不規則に見えます。イベントは周期的な刻みではなく、特定の信号遷移によって引き起こされます。このようなシステムを分析するには、信号間の依存関係に注意を払う必要があります。

一般的なタイミング問題と違反 ⚠️

慎重な設計をしても、タイミング問題が発生する場合があります。これらの問題は、再現が難しい間欠的な故障として現れることがよくあります。タイミング図でそれらを識別することは、トラブルシューティングの重要なスキルです。

セットアップ違反

データがクロックエッジに対して遅れて到着したときにセットアップ違反が発生します。視覚的には、データ遷移がすでにクロックエッジを過ぎた後に発生しているように見えます。その結果、受信コンポーネントが誤った値または前の値をキャプチャすることがよくあります。

ホールド違反

データがクロックエッジの直後に早すぎることでホールド違反が発生します。これは、コンポーネントがデータをキャプチャし終わる前に新しいデータが古いデータを上書きすることを意味します。これは特に危険で、出力電圧が高と低の間を浮遊するメタスタビリティを引き起こす可能性があるためです。

スキューとジッター

クロックスキューは、クロック信号が異なるコンポーネントに異なるタイミングで到着するときに発生します。スキューが大きすぎると、セットアップとホールドの有効なタイミングウィンドウが狭くなります。ジッターは、クロックエッジのタイミングの不安定さを指します。高いジッターはタイミングマージンを保証することが難しくなり、結果としてクロック速度を遅くする必要があります。

信号整合性のためのベストプラクティス 🛡️

堅牢な性能を確保するため、エンジニアはタイミング設計および解析においてベストプラクティスを遵守する必要があります。これらのガイドラインはリスクを最小限に抑え、システムの安定性を向上させます。

- トレース長を最小限に抑える:長いトレースは伝播遅延とノイズへの感受性を増加させます。可能な限り信号経路を短くしてください。

- インピーダンスを一致させる:送信ラインのインピーダンスがドライバとレシーバと一致していることを確認し、反射を防ぎます。

- グランドプレーンを使用する:固体のグランドプレーンは低インピーダンスの戻り路を提供し、ノイズやクロストークを低減する。

- 温度の影響を考慮する:電子部品は異なる温度で異なる挙動を示す。設計余裕は最悪の熱的条件を考慮して設定すべきである。

- 早期にシミュレーションを行う:物理的なプロトタイプを構築する前に、シミュレーションツールを使用してタイミングの挙動をモデル化する。これにより、設計サイクルの初期段階で違反を発見できる。

ハードウェアデバッグにおける応用 🔍

タイミング図は設計のためだけのものではない。デバッグにおいても不可欠なツールである。システムが故障した際、エンジニアはオシロスコープやロジックアナライザを使用して実際の信号波形を取得する。これらの取得されたトレースは、期待されるタイミング図と比較される。

実際の波形が図とずれている場合、その差異が根本原因を示唆する。例えば、キャプチャ期間中にデータラインにノイズがある場合、電源の問題や電磁干渉を示している可能性がある。クロックエッジが鋭くなく傾いている場合、ドライバ強度の問題を示唆している。

オシロスコープからの視覚的データをタイミング図の論理的要件と照合することで、エンジニアは障害を正確に特定できる。このプロセスにより、抽象的なタイミング制約が実際の物理的証拠に変換される。

主要な概念の要約 💡

タイミング図の基礎を習得することは、デジタルシステムを扱う上で不可欠である。信号、時間、論理状態の関係を理解することが含まれる。セットアップ時間、ホールド時間、伝播遅延といったパラメータに注意を払い、設計者は高速で信頼性の高いシステムを構築できる。

これらの図を読み解く能力は、ハードウェアチームとソフトウェアチーム間の効果的なコミュニケーションを可能にする。理論的な論理と物理的な現実の間の溝を埋める。シンプルな制御回路を設計している場合でも、複雑なマイクロプロセッサを設計している場合でも、タイミング解析はエンジニアリングの成功の基盤である。

常にアクティブ状態を確認し、クロックの境界を尊重し、物理的制限を考慮することを忘れないでください。練習を重ねることで、これらの視覚的表現を読み解くことが自然なことになり、問題の診断や性能の最適化を自信を持って行えるようになります。