タイミング図はデジタルシステム検証の基盤です。エンジニア、設計者、テスト担当者が信号の挙動を検証するために頼る、抽象的な論理を視覚的なタイムラインに変換します。タイミング図に誤りがあると、その影響は設計図の範囲をはるかに超えます。誤ったタイミングの仮定は、本番環境でのハードウェア障害、データ破損、またはシステムの不安定化を引き起こす可能性があります。本ガイドでは、タイミング解析でよく見られる誤りの原因を調査し、正確性を確保するための具体的な戦略を提示します。

正確なタイミング図を作成するには、単に線を引くこと以上に、クロックドメイン、信号伝播、物理的制約について深い理解が必要です。エンジニアはしばしば可視化フェーズを急ぎ、実装段階で重要になる微細な点を見逃しがちです。これらの一般的な誤りを早期に認識することで、デバッグや統合フェーズでの時間を大幅に節約できます。誤りが通常発生する具体的な領域を検討しましょう。

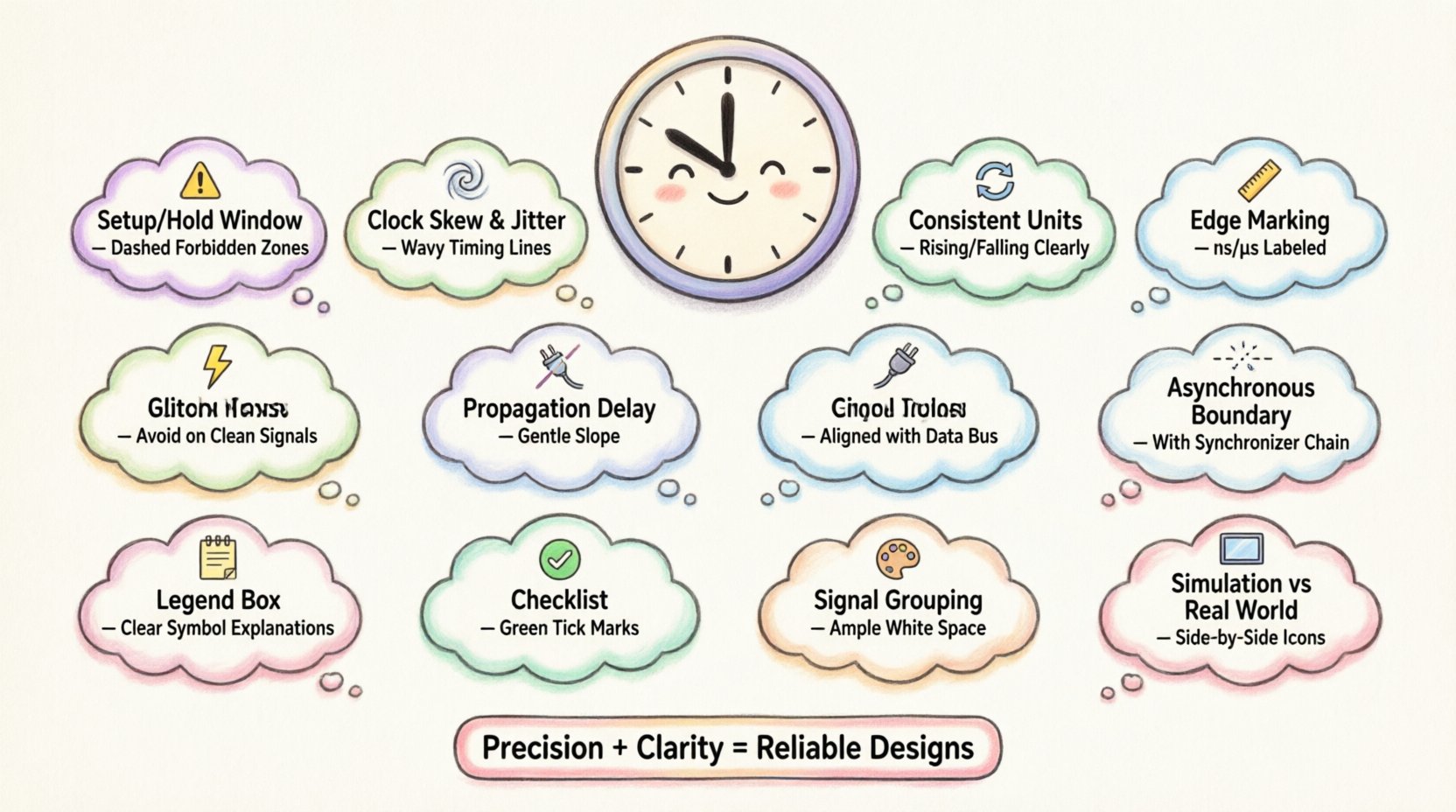

1. ライズ時間とホールド時間の違反を誤解すること ⚠️

セットアップ時間とホールド時間は同期デジタル設計における基本的な制約です。データがアクティブなクロックエッジの前に遅れて到着するとセットアップ違反が発生します。データがクロックエッジの後に早すぎることで変化するとホールド違反が発生します。これらは単なる理論的考えではなく、フリップフロップや論理ゲートの物理的限界を表しています。

多くの図では、データ信号の有効期間を明確に示すことができません。これらの信号を描画する際、エンジニアはしばしば重要なセットアップ時間とホールド時間のウィンドウを省略し、レビュー時に曖昧さを生じさせます。信頼性の高い図は、クロックエッジに対してこれらのウィンドウを明示的にマークすべきです。

- 一般的な誤り:ジッターまたはスケューを考慮せずに、データ遷移をクロックエッジと正確に一致させる描画。

- 一般的な誤り:セットアップ/ホールドウィンドウにおいて、エッジの方向(上昇 vs. 下降)を無視すること。

- 一般的な誤り:遷移時間がゼロの理想的なクロックエッジを仮定すること。

これらの問題を回避するには、常にセットアップ時間とホールド時間のマージンを注記してください。データ遷移が無効となる禁止領域を、明確な陰影やマークで示してください。この視覚的インジケータにより、レビュアーは信号パスが受信論理のタイミング要件を満たしているかを確認するよう強制されます。

2. クロックスケューとジッターを無視すること 🌪️

クロックスケューとは、クロック信号が異なる部品に到着する時間の差を指します。ジッターは、クロック信号のタイミングにおける短期的な変動を表します。これらの両方の要因は、データ信号の有効タイミングウィンドウを劇的に変化させる可能性があります。

図における一般的な誤りは、クロックをすべての部品に完全に垂直な直線として扱うことですが、実際には配信ネットワークが遅延を引き起こします。図で、パスの違いを考慮せずに単一のクロック線が3つの異なるレジスタに分岐していると、システム挙動の現実的でない姿を提示することになります。

- 影響:スケューは、データの伝播に利用可能な時間を減少させ、誤ったセットアップ違反を引き起こす可能性がある。

- 影響:ジッターはホールド時間のマージンを狭め、メタスタビリティのリスクを高める。

図を作成する際、スケューが顕著な場合は、クロックパスを相対的なオフセットを持つ別々の線として表現してください。スケューが無視できる程度の場合は、その仮定を図の注記に明確に記載してください。タイミング予算に影響を与える場合、クロック配信の複雑さを隠してはいけません。

3. 時間スケールと単位の不一致 📏

最も単純だが、最も深刻な誤りの一つは、単一の図内で時間スケールを混在させることです。一部のセクションではナノ秒を、別のセクションではマイクロ秒を表示する場合があります。この不一致により、読者は常に比率を再計算しなければならず、誤解のリスクが高まります。

別の問題は、明確な時間軸がないことです。スケールバーまたはラベル付きの目盛りがないと、パルスの持続時間が主観的になります。読者が間隔をどのように解釈するかによって、短いパルスが10ナノ秒か100ナノ秒かが変わってしまう可能性があります。

一貫性を保つためのこれらの基準に従ってください:

- スケールを定義する:図の下部または上部に時間目盛りを配置する。

- 科学的表記を使用する:ヘッダーに単位(ns、μs、ps)を明確にラベルする。

- 比率を比例させる: イベント間の水平距離が時間差と一致するようにしてください。

一貫性が信頼を生みます。図を見たすべてのエンジニアが、図のスケールについて仮定をせずに同じタイミング値を導き出せるべきです。

4. エッジトリガの曖昧さ 🔄

デジタル論理はしばしば特定のエッジトリガ、例えば立ち上がりエッジや立ち下がりエッジに依存します。タイミング図は、どのエッジが動作をトリガするかを明確に示す必要があります。ここでの曖昧さは、ハードウェアでまったく逆の動作を引き起こす可能性があります。

よくある間違いは、アクティブエッジを示さずにクロック信号を描くことです。例えば、フリップフロップが立ち下がりエッジでトリガするのに、図が立ち上がりエッジトリガとまったく同じように見えると、論理設計者は誤った動作を実装してしまう可能性があります。

- ベストプラクティス: クロックラインに矢印を付けて、アクティブエッジを示す。

- ベストプラクティス: 図例にトリガタイプをラベルする(例:「Posedge」、「Nedge」)。

- ベストプラクティス: 両エッジがアクティブでない限り、二重矢印を使用しない。

明確さが最も重要です。信号が非同期である場合、どのエッジがそれを制御しているかの混乱を避けるために、クロックドメインから明確に分離させる必要があります。

5. 伝播遅延を無視すること ⏳

伝播遅延とは、信号が論理ゲートや配線を通って入力から出力へ到達するまでの時間です。理想的な図では信号の変化が瞬時に見えるように描かれますが、実際のシステムでは常に遅延が生じます。

設計者が伝播遅延を無視すると、タイミング図は出力が入力の変化直後に即座に変化するように示します。これにより、シリコン上で発生するタイミング違反が隠れてしまう可能性があります。たとえば、組み合わせ回路のパスが図ではクロック周期を満たしているように見えるかもしれませんが、実際の遅延によりデータが次のクロックエッジを過ぎてしまうことがあります。

| 機能 | 理想図 | 実世界の実装 |

|---|---|---|

| 信号遷移 | 垂直線 | 遅延を伴う傾斜線 |

| 伝播 | 即時 | ゲート遅延 + 配線遅延 |

| セットアップマージン | しばしば確認されない | 最悪ケースを考慮しなければならない |

これを緩和するため、重要なパスに対して予想される遅延を注記してください。クロック周期に対して遅延が顕著である場合は、遷移を傾斜線で描くか、明確に遅延値をマークしてください。この視覚的表現により、製造前に潜在的なボトルネックをレビュアーが発見しやすくなります。

6. メタスタビリティリスクを無視すること 🌌

メタスタビリティは、フリップフロップがクロックエッジ付近のデータを受け取った際に発生し、予測不能な期間に未定義状態に入ってしまう現象です。タイミング図では、これは失敗モードであり通常動作ではないため、明示的に表現されることがほとんどありません。

しかし、非同期インターフェースにおけるメタスタビリティの可能性を無視することは重大な見落としである。図面が同期器チェーンなしに非同期信号がクロックに同期しているように示している場合、データ損失や破損のリスクを示唆している。

- 識別:適切な同期なしにクロックドメインを横切る信号を確認する。

- 文書化:メタスタビリティが既知のリスクである場所と、それがどのように緩和されているかを記録する。

- 可視化:破線を使用して非同期境界を示す。

システムがメタスタビリティを処理するように設計されていても、図面は同期段階を反映すべきである。これにより検証チームがこれらの特定の状態をテストする必要があることを確認できる。

7. 信号のギャップとハザード ⚡

ギャップは、並列パスにおける伝播遅延の不均衡によって生じる一時的なパルスである。タイミング解析で考慮されない場合、論理の誤動作を引き起こす可能性がある。

一般的な誤りは、物理的に避けられないギャップがある場所にクリーンで安定した信号を描くことである。例えば、マルチプレクサが入力間を切り替える際、出力は安定する前に一時的にちらつくことがある。図面が滑らかな遷移を示している場合、下流の論理回路はこれらのギャップをフィルタリングするように設計されていない可能性がある。

図面内の潜在的なハザード領域を強調する。特定の信号が状態変化中に一時的な動作を示す可能性があることを警告するための注記を使用する。これにより、テスト戦略にギャップ検出シナリオを含めることが可能になる。

8. コントロール信号の文脈不足 🔌

有効なデータ信号は、有効、リセット、チップセレクトなどのコントロール信号の文脈がなければ無意味である。データラインにのみ焦点を当てた図面は、そのデータが有効となる条件を欠いていることがよくある。

例えば、データバスが有効な値を示している場合でも、「Write Enable」信号がその期間中にアクティブでない限り、データは実質的に無視される。逆に、「Write Enable」がアクティブでもデータが無効な場合、システムはゴミデータを書き込む。

- コントロール信号の含む:常にコントロール信号をデータ信号と共に表示する。

- 有効性の定義:データが信頼できるタイミングを示すために、「Valid」フラグまたは類似のインジケータを使用する。

- 状態条件:コントロール信号の状態(High Active と Low Active)を明確にラベルする。

完全性が鍵である。コントロール信号の文脈を欠いたタイミング図は、デバッグ中に混乱の原因になりやすい。コントロール信号とデータの関係が視覚的に明確になるようにする。

9. 不適切な注記と凡例の使用 📝

適切な注記がなければ、完璧に正確な図面でも誤解される可能性がある。記号、省略語、凡例は一貫性を持ち、説明が必要である。

一般的な注記の誤りには以下が含まれる:

- 「Signal A」のような汎用的なラベルを使用し、説明的な名前を用いないこと。

- 特定の線種(実線 vs. 破線)の意味を説明しないこと。

- アクティブレベルの定義(Active High と Active Low)を省略すること。

専用の凡例セクションは、すべてのタイミング図に含まれるべきである。これは使用されたすべての記号、線種、省略語を定義する。これにより読者の認知負荷が軽減され、すべての人が図を同じように解釈できる。

10. 検証とレビュー確認リスト ✅

タイミング図を最終化する前に、体系的なレビューが必要です。以下のチェックリストを使用して、作業の正確性と明確性を検証してください。

| チェック項目 | 合格基準 |

|---|---|

| 時間スケール | 一貫した単位と明確な目盛りが提供されている |

| クロックエッジ | すべてのクロックに対してアクティブエッジが明確にマークされている |

| セットアップ/ホールド | 同期信号に対してウィンドウが定義されている |

| プロパゲーション | 重要なパスにおいて遅延が考慮されている |

| コントロール信号 | 有効/リセット信号がデータと共に表示されている |

| 凡例 | すべての記号と略語が説明されている |

| ドメインクロッシング | CDCポイントが特定され、マークされている |

このチェックリストを定期的に更新することで、一般的なミスが見逃されるのを防ぎます。設計チームにドキュメントが届く前に、品質のゲートとして機能します。

11. 視覚的明確性とレイアウト設計 🎨

タイミング図のレイアウトは、エラーがどれだけ簡単に検出できるかに影響します。信号が重なって混雑した図は誤読しやすくなります。関連する信号を縦方向に揃えることで、視線がイベント間の関係を追跡しやすくなります。

以下のレイアウト原則に従ってください:

- 信号をグループ化する:関連する信号(アドレスやデータなど)を近くに配置する。

- エッジを揃える:すべてのチャネルでクロックエッジが縦方向に揃っていることを確認する。

- 余白を確保する:信号の重なりを避けるために十分な白マスを確保する。

- 色分け:利用可能な場合、異なるクロックドメインに異なる色を使用する(ただし、印刷用には黒と白が標準である)。

明確なレイアウトは、図を解釈するために必要な認知的負荷を軽減します。これにより、異常やタイミング違反を一目で見つけることが容易になります。

12. 実世界の制約とシミュレーションの比較 🖥️

シミュレーションから単に導き出されたタイミング図は、物理的な現実を反映していない可能性がある。シミュレーションツールはしばしば理想的な状態、例えば寄生容量がゼロで、ルーティングが完全であるといった条件を仮定する。

シミュレーション結果を文書化する際、エンジニアは製造変動を考慮しなければならない。プロセス、電圧、温度(PVT)のコーナーはタイミングマージンをずらす可能性がある。名目値のみを示す図では、堅牢な設計には不十分な場合がある。

- 最悪ケース:タイミング解析には、最も遅いプロセスコーナーを考慮する。

- 最速ケース:ホールド時間解析には、最も速いプロセスコーナーを考慮する。

- マージン:PVTの変動を考慮するために、図に安全マージンを追加する。

文書化は、単に最良ケースのシミュレーション結果ではなく、設計の堅牢性を反映すべきである。これにより、チームは実世界での展開シナリオに備えることができる。

タイミング精度に関する最終的な考察 🛡️

タイミング図は技術仕様と同様に、コミュニケーションツールでもある。その主な目的は、すべてのステークホルダーに意図と制約を明確に伝えることである。スキューの無視、エッジトリガーの無視、制御信号の省略といった一般的なミスを避けることで、エンジニアは設計意図が文書からハードウェアに至るまで保持されることを保証する。

これらの図の正確性は、高コストな再設計やデバッグサイクルを防ぐ。適切に構成された図は、プロジェクトライフサイクル全体における唯一の真実の情報源となる。タイミング解析を正しく行うために時間を投資すれば、下流の実装プロセスもスムーズに進む。

タイミング図は動的な文書であることを忘れないでください。設計が変更されるたびに、図を更新すべきである。タイミング情報の整合性を維持することで、システムが運用期間中も信頼性を保つことができる。堅牢なデジタル設計を提供するためには、正確性、明確性、完全性に注力するべきである。