現代の分散システムの複雑なアーキテクチャにおいて、時間は単に測定されるべき指標ではなく、システムの挙動を規定する根本的な制約である。ソフトウェアの信頼性とは、クラッシュを防ぐことや例外を処理することだけを意味するものではない。特定の時間的境界内でコンポーネントが正しく相互作用することを保証することこそが、信頼性の本質である。複数のスレッド、サービス、またはハードウェアデバイスが共有リソースにアクセスしようとする場合、これらの相互作用の順序と持続時間は極めて重要になる。これがタイミング図が不可欠となる理由である。

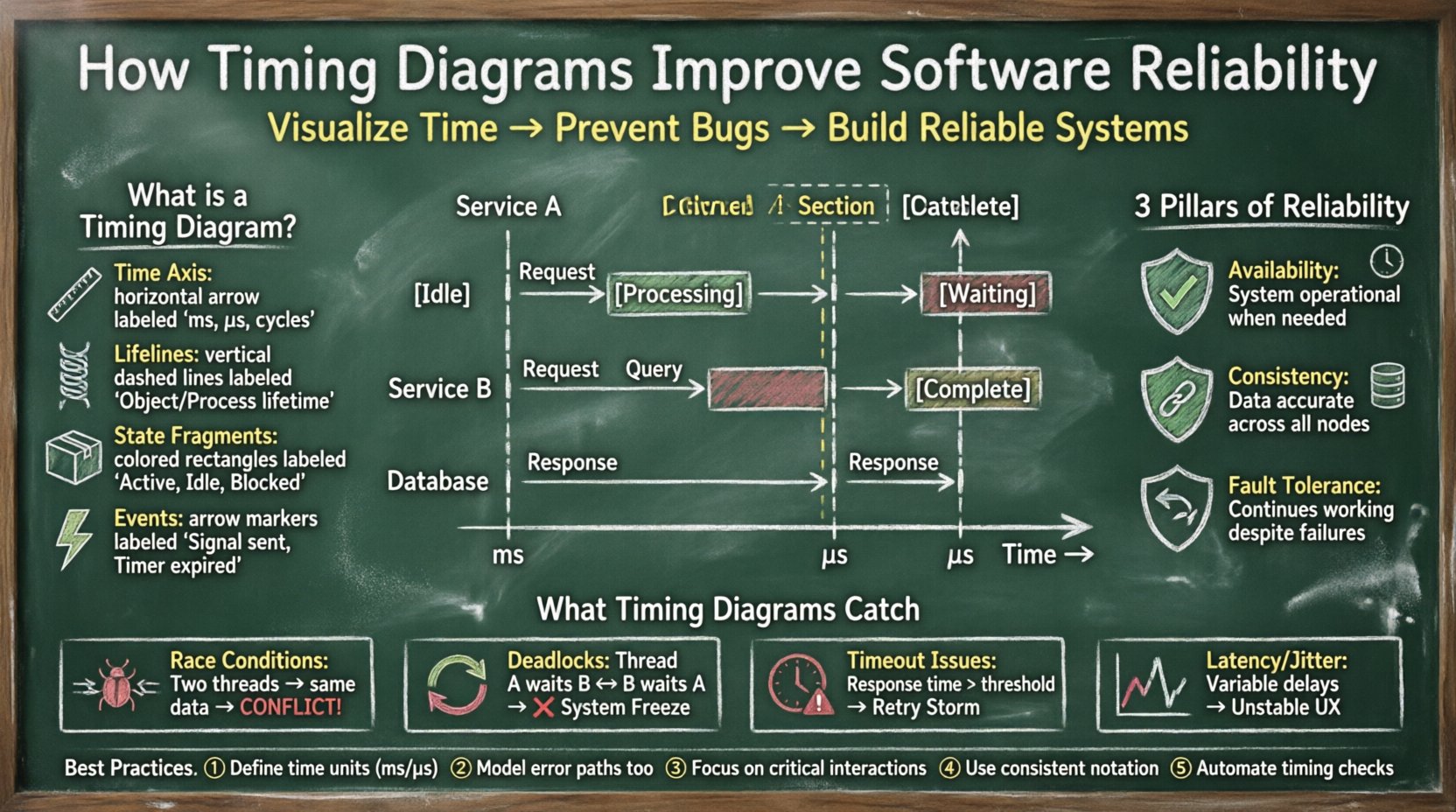

タイミング図は、信号やメッセージが時間とともに状態をどのように変化するかを視覚的に表現する。エンジニアは、1行のコードが実行される前から、イベント間の時間的関係をモデル化できる。時間の流れを可視化することで、チームは静的なフローチャートやシーケンス図では見えにくい、潜在的なボトルネック、レースコンディション、同期エラーを特定できる。このガイドでは、ソフトウェア信頼性を向上させるためにタイミング図をどう使うかというメカニズムを解説し、並行処理、レイテンシ分析、システム検証について深く掘り下げる。

🔍 エンジニアリングにおけるタイミング図の定義

タイミング図は、システムモデリングにおける行動図の一種で、オブジェクトの時間経過に伴う挙動を記述する。シーケンス図がメッセージの順序に主に注目するのに対し、タイミング図はイベント間の時間的関係に重点を置く。水平方向の時間軸に沿って、オブジェクトの状態とそれらの遷移を表示する。

- 時間軸:通常、左から右へ水平に進み、ミリ秒、マイクロ秒、またはクロックサイクル単位で時間の経過を表す。

- ライフライン:オブジェクトまたはプロセスの時間経過にわたる存在を表す垂直のバー。

- 状態断片:ライフライン上の長方形領域で、オブジェクトの状態(例:アクティブ、アイドル、ブロッキング、処理中)を示す。

- イベント:特定のアクション(例:信号の送信、タイマーの期限切れ)が発生するタイミングを示す矢印またはマーカー。

これらの要素をマッピングすることで、開発者はシステム操作のタイムラインを作成する。この視覚的文脈は、プロセスが完了するまでの時間や、他のプロセスを待つ時間の理解に不可欠である。抽象的な論理を、エラーを分析できる具体的なタイムラインに変換する。

🏗️ ソフトウェア信頼性の基盤

ソフトウェア工学における信頼性とは、指定された条件下で、特定の期間内にシステムが要求された機能を遂行する確率を指す。これを達成するためには、3つの主要な柱を満たす必要がある:

- 可用性:システムは必要に応じて稼働している必要がある。タイミング図は、復旧プロセスが許容可能な時間枠内で完了することを検証するのに役立つ。

- 整合性:データは分散ノード間で正確に保たれる必要がある。書き込みおよび読み込み操作を可視化することで、レイテンシによってデータ整合性が損なわれないことを確認できる。

- 故障耐性:システムは障害があっても継続して動作しなければならない。タイミング図は、フォールバックメカニズムが作動するまでの時間を明示し、ユーザーがサービスの中断を認識しないようにする。

時間制約を明確に理解しないと、システムは論理的には正しいが、実際には信頼性が低い状態になる可能性がある。たとえば、データベースクエリは正しいデータを返すかもしれないが、処理に10秒かかれば、応答性の高いユーザーインターフェースという信頼性要件に違反する。タイミング図はこうした時間的違反を明らかにする。

🐞 視覚的分析によるレースコンディションの検出

レースコンディションとは、2つ以上のプロセスが共有データを同時にアクセスする場合に発生し、最終的な結果がそれらの実行タイミングの相対的な順序に依存する状態である。これらは非決定論的であり、デバッガを接続するとしばしば消失するため、デバッグが極めて困難である。

タイミング図は、イベントの視覚的な順序を厳密に規定することで、このリスクを軽減する。潜在的なレースコンディションをモデル化する際、エンジニアは競合するスレッドのライフラインを描くことができる。図示された状況で、同期バリアが存在しない状態で両スレッドが同時に同じメモリ領域に書き込みを試みている場合、そのエラーは直ちに可視化される。

- 臨界領域の可視化:リソースがロックされている期間を強調表示する。他のプロセスがこの期間中にアクセスを試みた場合、図は衝突を示す。

- ゴーストの特定:ハードウェア-ソフトウェアインターフェースでは、セットアップ時間やホールド時間の要件を満たさない場合、信号のゴーストが発生する可能性がある。タイミング図はこれらの時間窓を明示的に表示する。

- 順序依存関係:初期化Aが初期化Bの開始前に完了することを保証する。図はこの依存関係に対する時間的チェックを強制する。

これらの問題を設計段階で解決することで、本番環境での障害発生確率が著しく低下する。並行性バグの検出を実行時ログから設計レビューへと移すことができる。

🧵 並行処理とスレッド同期の管理

現代のアプリケーションは、高負荷を処理するために非同期処理に大きく依存している。スレッド、コルーチン、ワーカープールにより、複数のタスクを並行して実行できる。しかし、ミューテックス、セマフォ、ロックなどの同期プリミティブは、独自のタイミングの複雑性をもたらす。

タイミング図は、これらの同期ポイントのモデル化を支援する。以下のような質問に答えるのに役立つ。

- スレッドはロックを待つ時間は、タイムアウトするまでどのくらいか?

- ロック取得時間はシステム負荷に応じて変化するか?

- 二つのスレッドが互いに無限に待つデッドロックは存在するか?

マルチスレッドアプリケーションを設計する際、エンジニアは各スレッドの状態を図示できる。スレッドAがリソース1を保持し、リソース2を待機している一方で、スレッドBがリソース2を保持し、リソース1を待機している場合、タイミング図は循環待機状態を明らかにする。この視覚的な証拠により、実装を開始する前にリソース取得ロジックを再構成できる。

さらに、タイミング図は優先度逆転の挙動を明確にする。リアルタイムシステムでは、高優先度タスクが、ロックを保持している低優先度タスクによってブロックされることがある。タイミング図により、この優先度逆転が明確になり、アーキテクトが優先度継承プロトコルを実装できる。

🌐 ネットワークプロトコルとハンドシェイク検証

分散システムでは、ネットワーク遅延は無視できない変数である。TCP/IP、HTTP/2、gRPCなどのプロトコルは、接続を確立するためにハンドシェイクに依存している。タイミング図は、これらの相互作用を検証するために不可欠である。

標準的な三回ハンドシェイク(SYN、SYN-ACK、ACK)を検討する。タイミング図によりエンジニアはこのプロセスの許容最大時間設定が可能である。図がACKの処理時間が設定されたタイムアウト閾値を超えることを示している場合、ストレス状態下で接続が失敗する可能性が高い。

- タイムアウト設定:リトライが発動するまでのリクエストの正確なミリ秒単位の期間を定義する。

- 再送信ロジック:失敗したパケットとその再送信の間隔を可視化し、ネットワークに過剰な負荷をかけることを確認する。

- Keep-Alive間隔:Keep-Aliveメッセージ間の間隔がネットワークのアイドルタイムアウトより短くなるようにし、過早な切断を防ぐ。

これらのネットワーク相互作用をモデル化することで、チームはソフトウェアがネットワークのジッターを適切に処理できることを保証できる。これにより、1つのマイクロサービスからの遅延応答が全体のフロントエンドを停止させる連鎖的障害を防ぐことができる。

⚙️ ハードウェア-ソフトウェアインターフェースのタイミング

ソフトウェアの信頼性は、ハードウェアとの相互作用の質に大きく依存する。組み込みシステム、IoTデバイス、高頻度取引プラットフォームは正確なタイミングを必要とする。数マイクロ秒の遅延でも、データ破損や財務損失を引き起こす可能性がある。

割り込みサービスルーチン(ISR)はその好例である。ハードウェア割り込みが発生すると、CPUは現在のタスクを一時停止して対応しなければならない。タイミング図は、割り込み遅延(割り込み要求からISRの実行開始までの時間)と割り込み応答時間の両方をマッピングする。

- 割り込み遅延:割り込みを認識するのに要する時間。

- コンテキストスイッチのオーバーヘッド:ISR中に保存および復元される時間。

- レジスタの保持:ISRが状態を変更する前に、状態が保存されていることを保証する。

タイミング図がISRが長すぎる場合、他の重要な割り込みをブロックする可能性があります。この視覚的分析により、開発者はISRコードを最適化するか、処理をバックグラウンドスレッドに移譲することで、リアルタイム要件を満たすことができます。

📉 ラテンシーやジッターの問題の特定

ラテンシーとは、データ転送の指示がなされてから実際に転送が開始されるまでの遅延を指します。ジッターとは、時間とともにラテンシーが変動する度合いを意味します。両方ともユーザー体験とシステムの安定性に悪影響を及ぼします。タイミング図は、これらの指標を分析する主なツールです。

リクエスト-レスポンスサイクルをモデル化する際、エンジニアは処理が行われる正確なポイントをマークできます。例えば:

- キュー待機時間:処理前にリクエストがバッファに滞在するのはどのくらいの時間ですか?

- 処理時間:ロジックが実際に実行されるのにどのくらいの時間がかかりますか?

- ネットワーク伝送:データがワイヤを伝わるのにどのくらいの時間がかかりますか?

これらのセグメントを合計することで、全体のラテンシーが計算されます。ジッターが高ければ、タイミング図は複数の反復においてイベント間の間隔が一貫性がないことを示します。この不一致は、基盤インフラの不安定性を示しており、リソース競合やネットワーク混雑の調査を促します。

📝 システム相互作用の記録

機能の追求の中でドキュメントはしばしば軽視されますが、長期的な信頼性にとって不可欠です。コードは頻繁に変更され、新しいチームメンバーも定期的に加入します。タイミング図は、システムが時間とともにどのように振る舞うかを示す耐久性のある参照資料となります。

適切に維持されたタイミング図のセットは、以下の機能を提供します:

- オンボーディング資料:新規開発者は、数千行のコードを読むことなく、時間的な流れを理解できます。

- デバッグ支援:バグが発生した際、エンジニアは実際の振る舞いを文書化されたタイミング図と比較することで、ずれを特定できます。

- 契約の定義:これらはサービス間の期待される振る舞いを定義し、統合のための契約として機能します。

このドキュメントは、インシデント対応時のエンジニアの認知負荷を軽減します。イベントのタイミングを推測する代わりに、視覚的な参照資料をもとに行動できます。

⚠️ 一般的なタイミング違反

すべてのタイミング問題が同等というわけではありません。一部は深刻な障害であり、他のものはパフォーマンスの低下です。以下の表は、システムモデル化で見つかる一般的な違反を分類しています。

| 違反の種類 | 説明 | 信頼性への影響 |

|---|---|---|

| セットアップ時間違反 | クロックエッジの前にデータが安定していない。 | 予測不能な状態変化、ハードウェア障害。 |

| ホールド時間違反 | クロックエッジの直後にデータが早すぎるように変化する。 | データ破損、メタスタビリティ。 |

| タイムアウトの期限切れ | 操作が定義された制限時間よりも長くかかる。 | サービス利用不能、リトライの嵐。 |

| デッドロック | 2つのプロセスが互いに無期限に待機している。 | システムのフリーズ、リソース枯渇。 |

| 優先度反転 | 高優先度タスクが低優先度タスクを待機している。 | デッドラインの逸脱、リアルタイム処理の失敗。 |

| バッファオーバーフロー | データが処理できる速度よりも速く到着する。 | パケット損失、メモリ枯渇。 |

これらのカテゴリをシステムのタイミング図と照らし合わせることで、直ちに対処が必要な問題を優先順位付けできる。ハードウェア違反はしばしばファームウェアの更新を要するが、ソフトウェアのタイムアウトは論理構造の再設計を必要とする場合がある。

🔄 開発ライフサイクルへの統合

信頼性の向上に効果的にタイミング図を使用するためには、ソフトウェア開発ライフサイクル(SDLC)に統合される必要がある。デプロイ後に後から追加する補足的なものにしてはならない。

- 設計フェーズ:システムアーキテクチャレビューの際に高レベルのタイミング図を作成する。重要な経路とタイミング制約を特定する。

- 実装フェーズ:タイミング図を単体テストのガイドとして使用する。論理的な正しさだけでなく、タイミングの境界もカバーしていることを確認する。

- 統合フェーズ:統合されたコンポーネントに対してタイミング解析を行う。統合システムがグローバルなタイミング要件を満たしていることを確認する。

- テストフェーズ:負荷テストツールを使用してタイミングデータを生成する。実際のタイミングログを元の図と比較する。

- 保守フェーズ:コードの変更がタイミングに影響する場合は図を更新する。ドキュメントがコードベースと同期されていることを確認する。

この統合により、各段階でタイミングに関する考慮が会話の一部となり、パイプラインの後半で信頼性の問題を修正するコストを削減できる。

📊 信頼性の向上の測定

タイミング図の利点をどのように定量するか?信頼性はしばしば稼働率のパーセンテージで測定されるが、タイミング図は特定の指標に貢献する:

- 平均故障間隔(MTBF):ラスコンディションやデッドロックを防ぐことで、障害の発生頻度が低下する。

- 平均修復時間(MTTR):より良いドキュメントと視覚的なログは、問題を診断するのに必要な時間を短縮する。

- 遅延の百分位数:タイミングのボトルネックを早期に特定することで、P99およびP999の遅延がより安定する。

- リソース利用状況:待機時間の最適化により、CPUのアイドル時間が減少し、全体的なスループットが向上する。

これらのメトリクスを時間とともに追跡することで、チームは厳密なタイミングモデリングとシステム安定性の直接的な相関関係を把握できる。信頼性は定性的な目標から定量的な現実へと移行する。

💡 最良の実践方法の要約

タイミング図のソフトウェア信頼性への影響を最大化するため、以下の実践を守ること。

- 明確な時間単位を定義する:曖昧さを避けるために、常に時間の単位(ms、s、サイクル)を明記する。

- エラー状態を含める:ハッピーパスだけでなく、タイムアウトパスやエラー処理パスもモデル化する。

- 重要なパスに注目する:すべての操作を図示する必要はない。システムの安定性に影響を与える相互作用に注目する。

- 一貫した表記を使用する:ライフラインとイベントに標準的な表記を採用し、チーム全体での理解を確保する。

- 可能な限り自動化する:タイミング解析ツールをCI/CDパイプラインに統合し、リグレッションを自動的に検出する。

ソフトウェアの信頼性は継続的な努力である。注意深さ、正確なモデリング、時間の影響がシステム動作にどのように及ぶかを深く理解することが求められる。タイミング図は、この複雑さを乗り越えるために必要な視覚的明確性を提供する。これらの実践を採用することで、エンジニアリングチームは機能するだけでなく、堅牢で予測可能であり、時間の予測不可能な性質に対して耐性を持つシステムを構築できる。

時間を可視化することで、そのコントロールを得ることができる。このコントロールは直接的に信頼性へとつながる。システムがより分散化・複雑化する中で、時間的関係をモデリングする能力は競争上の優位性となる。単に動作するシステムと、圧力下でも一貫して動作するシステムを分ける。