デジタル電子工学およびシステム設計の世界では、時間は単なる次元ではなく、回路が正常に動作するか、悲劇的な失敗を起こすかを決定する重要なパラメータである。タイミング図エンジニアが信号の時間的挙動を伝えるために用いる視覚的言語として機能する。マイコンインターフェースの設計、メモリバスのデバッグ、高速データ伝送の解析など、どのような状況においてもこれらの図を理解することは不可欠である。

このガイドでは、タイミング図のメカニズムを解説し、複雑な信号の挙動を理解しやすい要素に分解する。基本的な定義から高度な解析技術まで段階的に進み、波形を正確に解釈するためのツールを提供する。

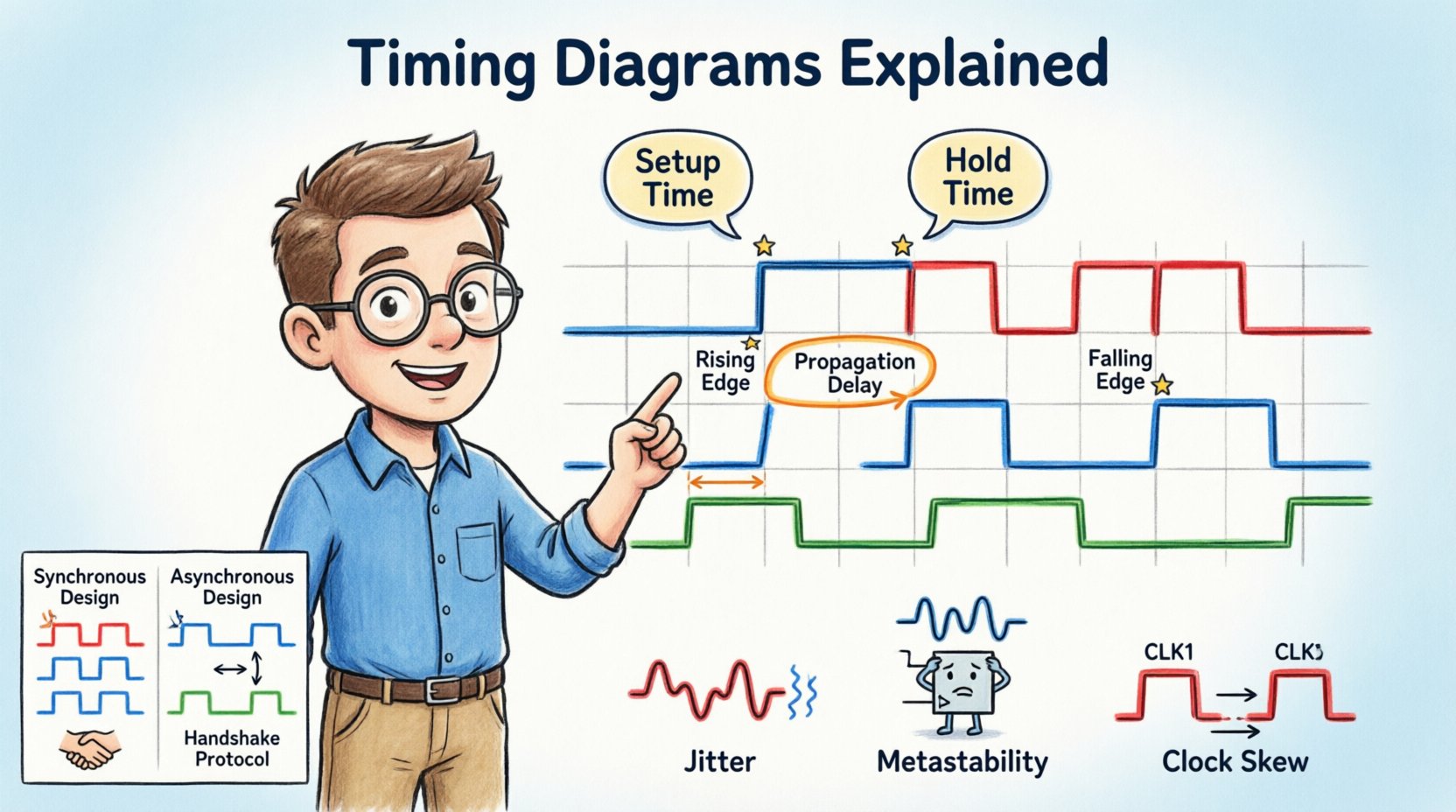

🔍 タイミング図とは何か?

タイミング図は、デジタルシステム内の信号変化の順序を図式化したものである。回路図が部品の接続方法を示すのに対し、タイミング図はいつその接続が状態を変化させるタイミングを示す。水平方向の時間軸に沿って信号の活動をマッピングすることで、設計者はクロックエッジの前にはデータが安定しているか、制御信号が適切なタイミングでアサートされているかを確認できる。

これらの図は以下の目的に不可欠である:

- ハードウェアとソフトウェアの相互作用の検証。

- 通信プロトコルのデバッグ。

- セットアップ時間およびホールド時間の要件を満たしていることを確認する。

- 将来の保守のためのシステム挙動の記録。

タイミングに関する明確な理解がなければ、論理的に正しい回路であっても、信号レースやメタスタビリティのため失敗する可能性がある。

🛠️ タイミング図の基本構成要素

タイミング図を効果的に読み取るためには、その基本的な構成要素を特定する必要がある。各要素は、デジタルシステムの状態と流れに関する特定の情報を含んでいる。

1. 時間軸

水平線は時間の進行を表す。通常、左から右へと流れます。詳細な技術文書では、この軸に特定の時間単位(ナノ秒、ピコ秒)またはクロックサイクルが目盛りとして示されることがある。

2. シグナルライン

垂直線は、クロックライン、データバス、制御ライン(チップセレクトやリード/ライトなど)といった個別の信号を表す。各ラインは回路内の特定のノードに対応している。

3. ロジックレベル

信号は通常、以下の2つの状態のいずれかに存在する:

- High(ロジック1 / VCC):信号トラックの上部に線を引くことでよく表現される。

- Low(ロジック0 / GND):信号トラックの下部に線を引くことで表現される。

一部のシステムではアクティブローロジックを使用しており、信号が電圧が低いときに機能する。図では、信号名の近くにボイル(丸印)を付けるか、特定の記号で示されることが多い。

4. トランジション

トランジションとは、信号がHighからLowへ、またはLowからHighへ変化する瞬間を指します。

- リジングエッジ:LowからHighへの遷移。イベントのトリガーに重要です。

- フェリングエッジ:HighからLowへの遷移。特定の制御シーケンスに使用されます。

- エッジトリガー:信号は安定状態ではなく、遷移中にのみ評価される。

⚙️ キーとなるタイミングパラメータ

正確なデジタル設計は、信号間の関係を定量することに依存します。以下のパラメータはタイミング解析の基盤です。

1. 伝播遅延(tpd)

信号が論理ゲートやコンポーネントの入力から出力まで到達するまでの時間です。信号は瞬時に変化することはありません。物理的な制限により遅延が生じます。

- 重要性:遅延が長すぎると、次の論理回路がデータを受け取るのが遅れ、エラーを引き起こす可能性があります。

- 測定方法:入力遷移の50%電圧点から出力遷移の50%電圧点までを測定する。

2. ライティング時間(tsu)

ライティング時間とは、データ信号が安定している必要がある最小時間です。クロックエッジが到着する前である。

- シナリオ:フリップフロップがクロックがトリガーする5ナノ秒前にデータを準備する必要がある場合、その時間がライティング時間です。

- 違反:データがクロックエッジに近いタイミングで変化すると、システムは値を正しくキャプチャできなくなる。

3. ホールド時間(th)

ホールド時間とは、データ信号が安定した状態を維持しなければならない最小時間である。の後クロックエッジが到着した後。

- シナリオ: フリップフロップは、トリガの後にデータを短時間「見ること」で、それを確実にラッチする必要がある。

- 違反: データがクロックエッジの直後に変化すると、入力が正しくラッチされない可能性がある。

4. クロックスキュー

クロックスキューとは、クロック信号が異なるコンポーネントに異なるタイミングで到着する現象である。これは、通常、PCB上のトレース長の違いによるものである。

- ポジティブスキー: クロックが宛先に遅れて到着する。

- ネガティブスキー: クロックが宛先に早く到着する。

5. ジッター

ジッターとは、信号の重要な瞬間が理想の時間位置から短期間でずれる現象である。これにより、タイミング解析に不確実性が加わる。

📊 比較:同期型設計と非同期型設計

これらの2つの設計哲学の違いを理解することは、タイミング図を正しく解釈するために不可欠である。

| 特徴 | 同期型タイミング | 非同期型タイミング |

|---|---|---|

| 制御信号 | グローバルクロックを使用 | ハンドシェイキング信号を使用 |

| 予測可能性 | 非常に予測可能 | 負荷に応じて変動 |

| 複雑さ | クロック配布が必要 | 複雑なハンドシェイキング論理が必要 |

| 消費電力 | 高い可能性がある(クロックのトグル) | 通常は低い(アクティビティ駆動) |

| タイミング図 | クロックエッジと同期している | 前の状態の完了に依存する |

🧐 タイミング図の読み方と分析の仕方

波形を分析するには体系的なアプローチが必要です。重要な詳細を見逃さないよう、以下の手順に従ってください。

ステップ1:クロックを特定する

主クロック信号を特定してください。これは通常、他のすべてのタイミングの基準となります。同期システムでは、すべてのデータ遷移が理想的にはこのクロックエッジに基づくべきです。

ステップ2:ギャップの有無を確認する

信号ラインに短い、意図しないパルス(ギャップ)がないか確認してください。これらは論理ゲートで誤動作を引き起こす可能性があります。きれいな図では遷移が明確ですが、実際の測定ではノイズが発生することが多いです。

ステップ3:セットアップ時間とホールド時間の確認

アクティブなクロックエッジの周囲に、セットアップ時間とホールド時間の領域を表す仮想の垂直線を引いてください。データ信号がこれらの領域内で安定していることを確認してください。

ステップ4:制御信号の確認

Chip Select(CS)やEnable(EN)などの制御信号が、データ転送の全期間中、有効であることを確認してください。制御信号がデータ送信中にもかかわらず低下すると、データが破損します。

ステップ5:時間間隔を測定する

特定のイベント間の時間を計算してください。たとえば、「リクエスト」信号から「レスポンス」信号までの遅延を測定します。これにより、仕様に対する性能の検証が可能になります。

🚀 タイミング解析の高度な概念

システムがより高速かつ複雑になるにつれて、基本的なタイミング図は高度な解析要件へと進化します。

1. メタスタビリティ

メタスタビリティは、フリップフロップがセットアップ時間またはホールド時間の要件を満たさない入力を受けるときに発生します。明確な0または1に収束する代わりに、出力は予測不能な期間、定義されない状態に入ります。

- 原因:非同期信号がクロックドメインを跨ぐときに頻繁に発生する。

- 対策:同期器チェーン(複数のフリップフロップを直列に配置)を使用して、メタスタビリティの発生確率を低下させる。

- 視覚的特徴:タイミング図では、信号が振動しているか、異常に長い時間かけて安定しているように見える。

2. セットアップ時間とホールド時間の予算

エンジニアは、システムが最大周波数で動作することを保証するために、タイミング予算を計算します。これには、クロック周期からすべての遅延(配線、ゲート、クロックスキー)を差し引く作業が含まれます。

総遅延が利用可能な時間を超える場合、最大動作周波数を低下させる必要があります。

3. 高速インターフェースのタイミング

DDRメモリやPCIeなどのインターフェースは、極めて正確なタイミングを必要とします。これらの図には通常、以下が含まれます:

- アイダイアグラム:信号品質を可視化するために、多数の信号遷移を重ね合わせたもの。

- デューティーサイクル歪み:High時間とLow時間がバランスしていることを確認する。

- 位相同期:複数ビットにわたってデータとクロックが同期して到着することを確認する。

4. パワーマネジメント状態

現代のデバイスは低消費電力モードに入ります。タイミング図はウェイクアップ遅延を考慮する必要があります。たとえば、周辺機器に電力を供給する信号は、デバイスがデータを受信できる状態になる前に発生しなければなりません。

📝 ドキュメント作成のベストプラクティス

明確なドキュメントは開発やデバッグ中のエラーを防ぎます。タイミング図を作成またはレビューする際は、これらの基準に従ってください。

- 一貫したスケーリング:関連する図の間で時間スケールを一貫させて、比較を容易にする。

- 明確なラベル:すべての信号には、その機能と論理極性(例:

RESET#はアクティブローを表す)。 - ズームレベル:高レベルの概要と、重要な遷移(例:セットアップ/ホールドウィンドウ)のズームイン表示の両方を提供する。

- 色分け:異なる電圧ドメインやクロックソースを区別するために色を使用する(例:赤はクロック、青はデータ)。

- バージョン管理:タイミング要件は変化します。図がハードウェアのリビジョンと一致するように、バージョン管理を確実に行う。

🛠️ 一般的な落とし穴とトラブルシューティング

経験豊富なエンジニアでもタイミングの問題に直面することがあります。以下に一般的な状況とその対処法を示します。

落とし穴1:トレース遅延を無視すること

PCBのトレースには物理的な長さがあり、遅延を引き起こします。高周波数では、数インチの配線がクロックサイクルに相当する場合があります。

- 解決策: ティミング予算の計算において、トレース長を考慮してください。

落とし穴2:浮遊入力

接続されていない入力は中間電圧に浮遊する可能性があり、振動を引き起こすことがあります。

- 解決策:すべての入力に明確なプルアップまたはプルダウン抵抗を確保してください。

落とし穴3:レースコンディション

2つの信号が同時に変化する場合、到着順序が結果を決定します。

- 解決策:イベントの順序を制御するために、同期論理回路またはステートマシンを使用してください。

落とし穴4:オーバーシュートとアンダーシュート

信号の反射により、電圧が電源レールを超える(オーバーシュート)またはグランド以下に低下する(アンダーシュート)ことがあります。

- 解決策:適切な終端抵抗とインピーダンス整合を実装してください。

🔗 実世界の応用

ティミング図は、さまざまな分野の工学において応用されています。

1. メモリインターフェース

DRAMおよびSDRAMは、読み取り/書き込み操作に厳密なタイミングシーケンスを必要とします。CASレイテンシーやRASからCASまでの遅延は、これらの図で可視化される重要なパラメータです。

2. マイコン通信

I2C、SPI、UARTなどのプロトコルは、クロック線とデータ線の間の特定のタイミング関係に依存しています。たとえば、I2Cではクロックがハイの間、データ線が安定している必要があります。

3. パワーサプライの順序制御

複雑なシステムでは、電源レールを特定の順序で起動する必要があります。ティミング図により、I/O電圧が印加される前にコア電圧が安定していることを保証できます。

🎯 主なポイントのまとめ

ティミング図を習得するには、忍耐力と細部への注意が必要です。以下のポイントが、効果的な設計と分析に必要な知識を要約しています。

- 時間は重要です:デジタル論理は、信号間の正確な時間的関係に依存しています。

- セットアップとホールド:これらは、最大動作速度を決定する最も一般的な制約です。

- 視覚的検証:図により、ハードウェアが構築される前に潜在的な衝突を確認できます。

- 文脈が重要です: 信号のタイミングに影響を与える物理的環境(PCB、温度、電圧)を常に考慮してください。

- 標準化: チーム間でのコミュニケーションの明確さを確保するために、標準的な記号や表記を使用してください。

これらの原則を適用することで、デジタルシステムが堅牢で信頼性が高く、パフォーマンスに優れていることを保証できます。これらの図を解釈し、作成できる能力は、現場で機能する設計と失敗する設計を分ける基本的なスキルです。

📈 今後の展望

技術が進歩するにつれて、タイミング制約は厳しくなる。現代のシステムはギガヘルツレベルで動作し、ナノ秒単位の違いが極めて重要になる。最先端のハードウェア開発に従事するエンジニアにとって、信号整合性とタイミングクロージャに関する継続的な学習が不可欠である。

既存の回路図とその対応するタイミング図を分析することから始めましょう。時間間隔の測定や違反の特定を練習することで、時間とともにパターンが直感的に理解できるようになり、物理的に問題が発生する前に予測できるようになります。