タイミング図はデジタルシステム設計の基盤である。論理、ハードウェア、ソフトウェアの間の視覚的契約として機能し、信号がいつ状態を変化させるべきかを正確に定義する。しかし、工学分野で広く使用されているにもかかわらず、これらの図がどのように作成され、解釈され、利用されるかについて、根強い誤解が存在している。多くの専門家が、タイミング図を静的な図解と見なしており、システム動作の動的な表現とは捉えていない。

このガイドは、誤解を解き明かすことを目的としている。一般的な誤解を分析し、信号伝播の技術的現実を検証し、正確なタイミング文書作成のためのフレームワークを構築する。事実と虚構を明確に分けることで、エンジニアはデバッグ時間を短縮し、システムの信頼性を向上させることができる。

タイミング図とは何か? 🤔

タイミング図とは、時間の経過とともにデジタル回路内の信号の挙動を図式化したものである。回路図が接続関係を示すのに対し、タイミング図は因果関係と時間的関係を示す。信号レベル(高、低、浮遊)を時間軸に対してプロットすることで、設計者がデータが予想されるタイミングで安定しているかを確認できる。

主な特徴には以下が含まれる:

- 時間軸:通常は水平方向に延び、イベントの進行を表す。

- 信号線:特定の配線、バス、または論理状態を表す垂直線。

- エッジ:低から高への遷移(リジング)または高から低への遷移(フェーリング)。

- ラベル:セットアップ時間、ホールド時間、または遅延を示す注記。

これらの要素を明確に理解しないと、図は明確さではなく混乱の原因となる。

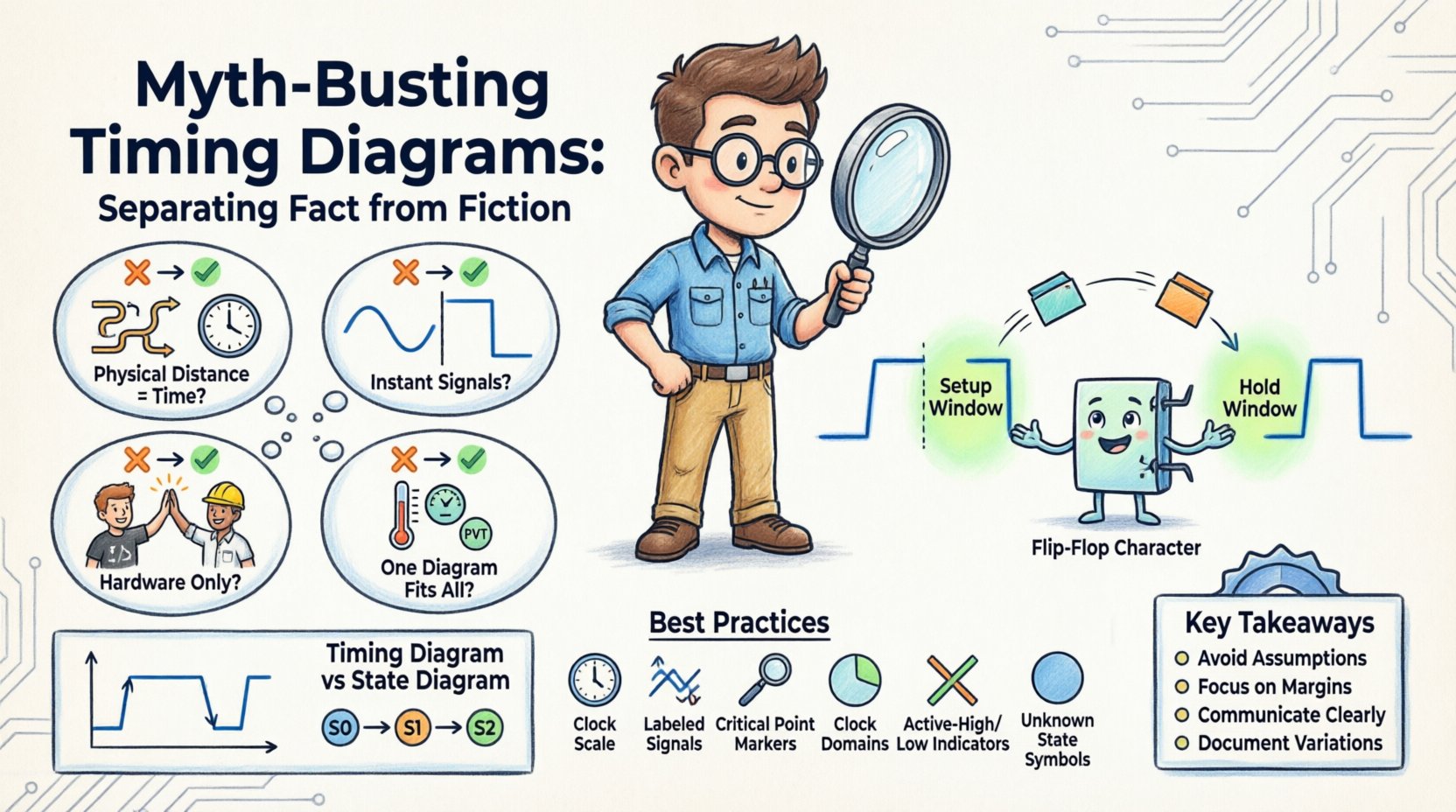

タイミング図に関する一般的な誤解 🚫

設計品質を向上させるためには、まず誤った信念がエラーを引き起こすことを特定する必要がある。以下は、技術界で広く流通している代表的な誤解である。

誤解その1:タイミング図は正確な物理的距離を示す

虚構:エンジニアはしばしば、図上の2つのエッジ間の水平距離が、PCB上の物理的トレース長に直接対応すると仮定する。

事実:タイミング図は物理的な空間ではなく、論理的または電気的な時間を表す。トレース長は伝播遅延に影響するが、図はその遅延の「結果」に注目しており、幾何学的形状そのものには注目しない。結果その遅延の結果に注目しており、幾何学的形状そのものには注目しない。1ナノ秒の遅延は、FR4基板上の15cmのトレース、または異なる誘電率を持つ銅トレース上の10cmのトレースを表す可能性がある。図は物理的な媒体を抽象化し、タイミングウィンドウに焦点を当てる。

- 物理的な長さが遅延を決定するが、図は遅延の値を示す。

- ルーティングの複雑さは隠されている。重要なのは最終的な結果だけである。

- 時間と距離の間に1:1のスケール関係があると仮定すると、レイアウトエラーが生じる。

誤解その2:信号遷移は瞬時に起こる

虚構:多くの図では、垂直線が信号の状態変化が即座に起こることを示している。

事実:物理的な信号は瞬時に状態を変えることはない。常に立ち上がり時間と立ち下がり時間が存在する。図で垂直なエッジが示されている場合、それはクロック周期に対して速い遷移を表しているが、ゼロではない。遷移時間を無視すると、リングやクロストークなどの信号整合性の問題が生じる可能性があり、これらは理想化された図では見えない。

- 立ち上がり時間とは、電圧が10%から90%に達するまでの時間である。

- 図は読みやすさのためにしばしばこれを簡略化するが、シミュレーションではこれを考慮しなければならない。

- 高速設計では、遷移傾斜の明示的なモデル化が求められる。

誤解3:タイミング図はハードウェアエンジニア専用である 🛠️

虚構:ソフトウェア開発者やシステムアーキテクトはしばしばタイミング図を無視し、コード論理とは無関係だと仮定している。

事実:ソフトウェアはハードウェアのタイミング制約に従わなければならない。割り込み、DMA転送、メモリマップドI/Oはすべて、ハードウェアによって設定されたタイミングに依存している。ドライバがハードウェアが「準備完了」信号をアサートする前にデータを読み込もうとすると、バスエラーが発生する。タイミング図は異分野間のコミュニケーションに不可欠である。

- ソフトウェア割り込みはハードウェアのクロックサイクルと整合しなければならない。

- メモリアクセス窓はタイミング仕様によって定義される。

- ハードウェアチームとソフトウェアチームの両方が、タイムラインについて共有された理解を持つ必要がある。

誤解4:一つの図ですべての状況をカバーできる 🌍

虚構:一つのタイミング図で、運用条件に関係なく全体のシステムを記述できる。

事実:タイミングは温度、電圧、プロセス変動(PVT)によって変化する。ノーマル条件で描かれた図でも極端な状況では失敗する可能性がある。設計者は最悪ケースを考慮しなければならない。最良状態を示す図よりも、動作限界を強調した図の方がしばしば有用である。

- 最悪ケースの遅延が最小クロック周期を決定する。

- 温度は抵抗と静電容量に影響する。

- プロセス変動はトランジスタのスイッチング速度を変化させる。

詳細解説:セットアップ時間とホールド時間 ⏱️

タイミング違反を理解することは重要である。データ整合性の分析を支配する2つの特定の概念がある:セットアップ時間とホールド時間。これらはデジタルシステムにおける最も難解なバグの原因となることが多い。

セットアップ時間(Tsu)

セットアップ時間とは、クロックエッジの前にデータが安定している必要がある最小時間である。データがクロックエッジに近すぎるように変化すると、受信側のフリップフロップが正しい値をキャプチャできなくなる可能性がある。

- これは、キャプチャウィンドウが閉じる前にデータが安定していることを保証する。

- 違反は準安定状態または誤った論理状態を引き起こす。

- パス遅延は、クロック周期からセットアップ時間分を引いた値より小さくなければならない。

ホールド時間 (Th)

ホールド時間は、データが安定したまま保たれる必要がある最小時間である。クロックエッジの後データが安定したまま保たれる必要がある時間である。クロックエッジの直後にデータが変化しすぎると、フリップフロップは以前にキャプチャした値を失う可能性がある。

- これにより、データがラッチされるのに十分な時間安定した状態を保つことができる。

- 違反はセットアップ違反よりもしばしば修正が難しい。

- パス遅延は、ホールド時間の要件よりも大きくなければならない。

タイミング違反のシナリオ

タイミング図を分析する際には、以下のパターンに注目する。

- セットアップ違反: データ信号がクロックエッジが到着する時点でまだ変化している。

- ホールド違反: データ信号がクロックエッジの直後に変化する。

- グリッチ: セットアップ/ホールドウィンドウ内に存在するが、有効な遷移ではない短いパルス。

タイミング図 vs. ステート図 🔄

タイミング図とステート図の間に混乱が生じることが多い。両者ともシステムの動作を記述するが、異なる問いに答える。ステート図はシステムが何行うか(論理フロー)を示すのに対し、タイミング図はいつその動作が起こるタイミング(時間的フロー)を示す。

| 特徴 | タイミング図 | ステート図 |

|---|---|---|

| 主な焦点 | 時間と信号レベル | 論理と制御フロー |

| 軸の表現 | 水平軸 = 時間 | 水平軸 = 論理状態 |

| 適している用途 | 信号整合性、同期 | アルゴリズム設計、有限状態機械論理 |

| 複雑さ | 高い時間的詳細 | 高い論理的分岐 |

| 信号の詳細 | 電圧レベル(High/Low)を表示 | 抽象的な状態(アイドル/実行)を表示 |

適切な図を用いることで誤解を防ぐことができます。状態機械はタイミング図なしで設計可能ですが、高速バスインターフェースはそうはいきません。

正確な図を作成するためのベストプラクティス ✅

ドキュメントの効果を確保するため、以下のガイドラインに従ってください。ドキュメントの正確さは実装時の曖昧さを減らします。

- 時間スケールを定義する: 常に単位(ns、µs、サイクル)を明記する。サイクルを使用する場合は、クロック周波数を定義する。

- すべての信号にラベルを付ける: 「Signal 1」のような汎用名を使用しない。代わりに「CLK_IN」や「DATA_VALID」のような説明的な名前を使用する。

- 重要なポイントをマークする: 設定時間とホールド時間のウィンドウを、塗りつぶしや注記で明確に強調する。

- クロックドメインを含める: 複数のクロックが存在する場合は、明確に区別する。該当する場合は、非同期クロック間の関係を示す。

- アクティブハイ/ローを表示する: アクティブ状態がHigh(1)かLow(0)かを明確にし、極性エラーを避ける。

- 未定義状態を示す: 空白にしないで、未定義または高インピーダンス状態をXまたはZで表す。

非同期信号の扱い 🔄

タイミング図の最も難しい点の一つが、非同期信号の扱いです。これらはメインシステムクロックと同期していない信号であり、管理しなければならない不確実性をもたらします。

- メタスタビリティ: 異種信号がクロックエッジの近くに到着すると、フリップフロップはメタスタビリティ状態に入ることがあります。最終的には0または1に収束しますが、その時間は予測できません。

- 同期器: メタスタビリティを解消するためにフリップフロップのチェーンを使用する。タイミング図では、次のクロックエッジより前にメタスタビリティ領域が解消されていることを示す必要がある。

- ハンドシェイキング: I2CやSPIなどのプロトコルは非同期的なハンドシェイキングを使用する。タイミング図には、マスターがスレーブの応答を待つ待機状態を示す必要がある。

実世界の応用:レースコンディションのデバッグ 🐞

データバスが正しく読み込まれていない状況を想像してみよう。システムは時折フリーズする。タイミング図の分析により、問題が明らかになる。

- 観察: 「Ready」信号は、「Read」ストローブのわずか後にアサートされている。

- 図の確認: タイミング図では、「Ready」エッジが「Read」ストローブのセットアップウィンドウ内に落ちていることが示されている。

- 結論: データが有効になる前に読み込まれている。

- 修正: 「Read」ストローブを遅らせるか、「Ready」パルスを延長するようにロジックを調整する。

この例は、タイムラインを可視化することが重要であることを強調している。図がなければ、レースコンディションはコードの論理の中に隠れたままになる。

ツールと分析手法 🔍

特定のソフトウェア名は焦点ではないが、分析の手法は常に一定である。現代のエンジニアリングは、シミュレーションと波形ビューアを用いてタイミング図の妥当性を検証している。

- シミュレーション: テストベンチを実行して、設計意図に合致する波形を生成する。

- 静的タイミング解析(STA): シミュレーションなしで遅延を計算し、すべてのパスで違反がないか確認する。

- ハードウェアデバッグ: オシロスコープを用いて実世界の波形をキャプチャし、理論的な図と比較する。

- バージョン管理: タイミング図をバージョン管理に保つ。ハードウェアの変更は、タイミング仕様の更新を伴うことが多い。

ジッターとスケューの影響 📉

タイミング図はしばしば完璧で直線的な線で描かれる。現実はより複雑である。ジッターとスケューはタイミングの正確性に影響を与えるノイズ源である。

- ジッター: シグナルのエッジのタイミングのばらつき。クロックジッターにより、サンプリングウィンドウがずれる。

- S スキュー: 回路内の異なる点における同じクロック信号の到着時間の差。

- 影響: 両方ともタイミングマージンを減少させる。理想的なエッジだけでなく、マージンを示すことが理想的である。

主な教訓の要約 📝

タイミング図は単なる図面以上のものである。それは動作の仕様である。それらを取り巻く誤解と事実を理解することで、エンジニアはより強固なシステムを設計できる。

- 仮定を避ける: 瞬時の遷移や完全な同期を仮定してはならない。

- マージンに注目する: ライズ時間とホールド時間は、失敗を防ぐための安全なバッファである。

- 明確に伝える: 図を用いてハードウェアチームとソフトウェアチームのギャップを埋める。

- ばらつきを文書化する: 環境やプロセスに応じてタイミングが変化することを認識する。

タイミング図を見たとき、時間を意識する。制約を意識する。信頼性を意識する。この視点により、静的な画像がエンジニアリングの優れたツールに変化する。