タイミング図は、特定の期間におけるデジタル信号の挙動を可視化するための必須ツールです。デジタル電子工学およびコンピュータ工学の分野では、信号の相互作用を理解することは、システムの安定性と性能にとって不可欠です。このガイドでは、タイミング図の表記法について詳細に検討し、正確に波形を読み取り、作成し、解釈できるようにします。ソフトウェアツールに依存せずに、信号レベル、時間軸、遷移、および重要なタイミングパラメータについて検討します。

🔍 タイミング図の主要構成要素の理解

根本的には、タイミング図は信号の論理状態を時間に対して表現したものです。これはデータがシステム内をどのように移動するかを示す設計図のような役割を果たします。これらの図を正しく解釈するためには、基本的な軸と信号の表現方法を理解する必要があります。

- 水平軸:時間を表します。この軸は左から右へと流れ、出来事の順序を示しています。

- 垂直軸:特定の信号ラインの論理状態または電圧レベルを表します。

- 信号線:各水平線は、回路内の特定のワイヤ、ネット、または論理変数に対応します。

- 論理レベル:信号は一般的に、High(高)とLow(低)と呼ばれる2つの状態の間で切り替わります。

タイミング図を分析する際、視者は1つの信号の変化と別の信号の変化との関係を探ります。この関係が、データが正しくキャプチャされるか、エラーが発生するかを決定します。適切な表記により、設計を検証するエンジニアにとってこれらの関係が明確になるようにします。

⚡ 信号の論理レベルと状態

デジタルシステムは2進法の原理に基づいて動作しますが、物理的な表現は異なります。表記は、論理1と論理0を何が構成するかを明確に定義する必要があります。これらのレベルを誤解すると、深刻な設計失敗につながる可能性があります。

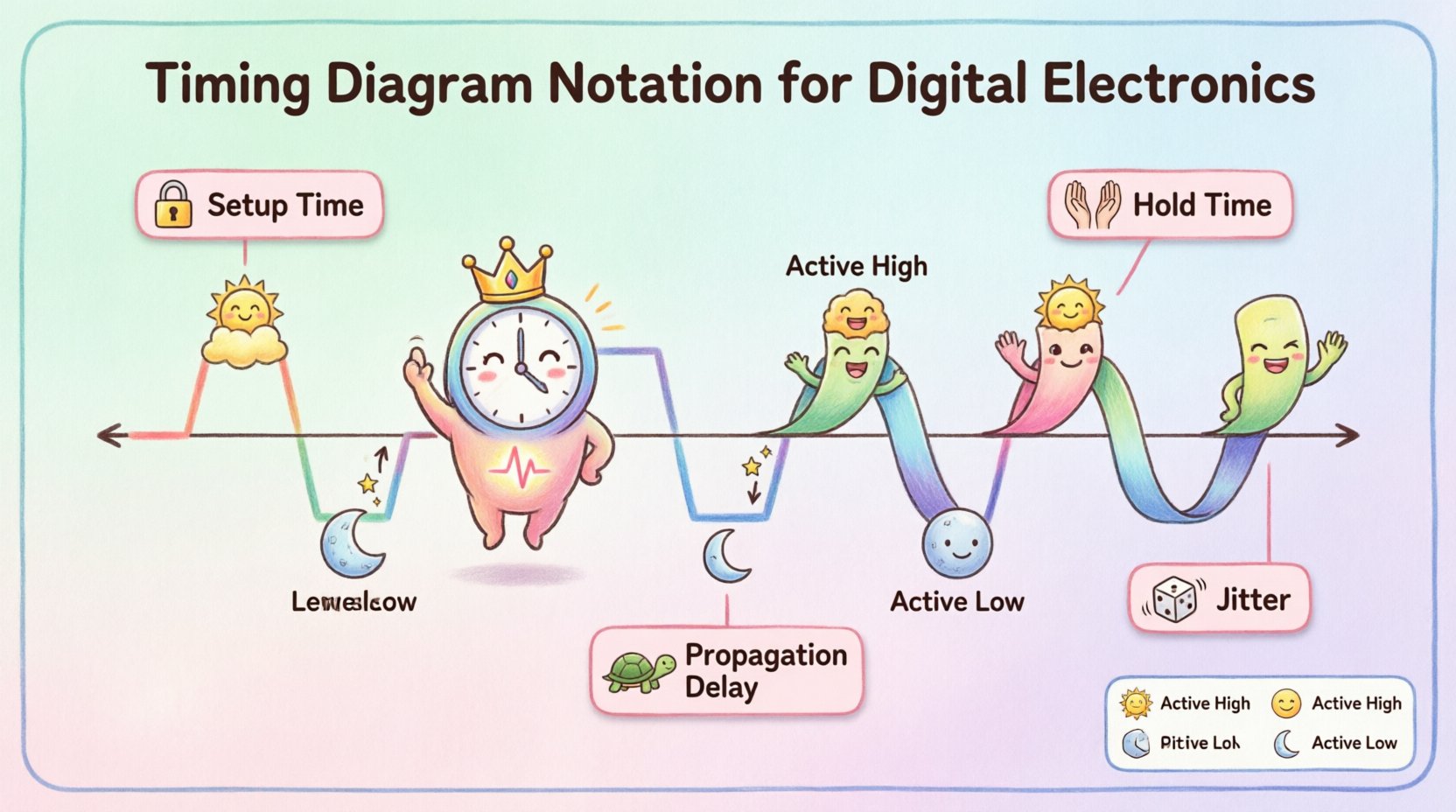

アクティブハイ対アクティブロウ

信号は高電圧のときにアクティブになる場合と、低電圧のときにアクティブになる場合があります。この概念はリセットやイネーブルなどの制御信号において非常に重要です。

- アクティブハイ:信号が高電圧(論理1)のときにその機能を果たします。これはほとんどのデータラインの標準です。

- アクティブロウ:信号が低電圧(論理0)のときにその機能を果たします。制御信号は、ノイズを低減したり、特定のハードウェア要件に適合させたりするために、この表記をよく使用します。

- 表記のインジケータ:アクティブロウの信号は、しばしば名前の上にバーを付けるか、回路図の線の端にバブルを付けることで示されます。

論理電圧レベル

論理0と1は抽象的な概念ですが、タイミング図は物理的な電圧を表します。表記は理想的には電圧のしきい値を明示すべきです。

- 論理高:通常、特定のしきい値(例:3.3Vまたは5V)を超える電圧で表されます。

- 論理低:通常、特定のしきい値(例:0V)未満の電圧で表されます。

- 未定義領域: 高閾値と低閾値の間の領域で、信号の状態が不定となる。図はこの領域に留まらないようにするべきである。

⏱️ 時間軸と同期

時間の表現は、タイミング図において二番目に重要な側面である。電圧とは異なり、時間は連続的であるが、デジタル信号は離散的な瞬間に変化する。表記法は同期的および非同期的なイベントの両方を扱わなければならない。

クロック信号

ほとんどのデジタルシステムは、動作の同期にクロックに依存している。クロック信号はシステムの鼓動である。

- 周期:クロックの1周期分の時間。

- 周波数:1秒あたりの周期数で、通常はヘルツ(Hz)で測定される。

- デューティーサイクル:信号がハイ状態にある周期の割合。

- 表記法:クロック信号は、しばしば方形波のパターンで描かれる。

相対時間と絶対時間

タイミング図は、相対時間または絶対時間を使用できる。

- 相対時間:測定は、特定のクロックエッジなどの基準点から行われる。これは、セットアップ時間およびホールド時間の解析で一般的である。

- 絶対時間:イベントに特定のタイムスタンプが割り当てられる。これは、長期間にわたる通信プロトコルのデバッグに有用である。

時間スケール

適切な時間スケールを選択することは、明確さにとって不可欠である。

- ナノ秒:信号が急速に変化する高速論理で使用される。

- マイクロ秒:遅い周辺機器とのインタラクションで使用される。

- ミリ秒:システムレベルの電力管理や低周波イベントで使用される。

🔄 エッジ遷移と表記法

信号が状態を変化させる瞬間は、状態そのものと同じくらい重要である。表記法は、これらの遷移がどのように、いつ発生するかを明確に示さなければならない。

立ち上がりエッジと立ち下がりエッジ

エッジは論理レベル間の遷移を表します。

- 立ち上がりエッジ:ローからハイへの遷移。通常、垂直線または上向きの矢印で示される。

- 立ち下がりエッジ:ハイからローへの遷移。通常、垂直線または下向きの矢印で示される。

- 傾斜:理想的な図ではエッジは垂直である。実際の図ではエッジは立ち上がり時間または立ち下がり時間を表す傾斜を持つ。

遷移遅延

信号は即座に切り替わらない。表記は伝播遅延を考慮しなければならない。

- 伝播遅延:入力での変化が出力での変化を引き起こすまでにかかる時間。

- 表記:入力の遷移と出力の遷移の間にギャップがあることで示されることが多い。

グリッチとハザード

回路の遅延により、意図しない遷移が発生する可能性がある。これらはしばしば短いスパイクとして示される。

- グリッチ:存在してはいけない短いパルス。表記では破線や異なる色が使われる場合がある。

- ハザード:タイミングの違いによって、誤った出力が生じる可能性。

📏 重要なタイミングパラメータ

特定のパラメータがデジタルインターフェースの信頼性を定義する。これらはデータ整合性を確保するためにエンジニアが測定する指標である。

| パラメータ | 説明 | 単位 |

|---|---|---|

| セットアップ時間 | データはクロックエッジの前に安定している必要がある時間。 | 時間(ns) |

| ホールド時間 | データはクロックエッジの後に安定したまま維持される必要がある時間。 | 時間(ns) |

| 伝播遅延 | 入力の変化から出力の変化までの時間。 | 時間(ns) |

| クロックからQ | クロックエッジから出力の変化までの時間。 | 時間(ns) |

| ジッター | 信号エッジのタイミングのばらつき。 | 時間(ps/ns) |

セットアップ時間とホールド時間

これらは同期システムにおいて最も重要な制約条件です。

- セットアップ時間の違反:データがクロックエッジに近すぎるように変化すると、システムは正しい値をキャプチャできなくなる可能性があります。

- ホールド時間の違反:データがクロックエッジの直後に早すぎるように変化すると、システムはその値を失う可能性があります。

- 表記:これらは、データラインが変化してはならないクロックエッジ周辺の時間窓として通常表示されます。

伝播遅延

この遅延はシステムの最大周波数に影響します。

- 高から低:信号が高から低に変化するのにかかる時間。

- 低から高:信号が低から高に変化するのにかかる時間。

- 表記:入力波形と出力波形の間に水平なギャップとして示されることが多いです。

🛠️ コントロール信号とアクティブ状態

コントロール信号はデータの流れを管理します。その表記は、いつアクティブであるかを明確に示す必要があります。

| 信号タイプ | アクティブ状態 | 表記例 |

|---|---|---|

| リセット | アクティブロー | リセット# または リセットバー |

| 有効 | アクティブハイ | 有効 |

| 割り込み | アクティブハイまたはロー | IRQ または IRQバー |

| チップセレクト | アクティブロー | CS# |

リセット信号

リセット信号はシステムを初期化します。非同期または同期のどちらかです。

- 非同期リセット:クロックにかかわらず即座に効果を発揮します。記号はリセット線が任意のタイミングでアクティブになることを示します。

- 同期リセット:クロックエッジでのみ効果を発揮します。記号はリセット線がクロックエッジの前にアクティブであることを示します。

有効信号

有効信号は操作の許可またはブロックを行います。

- ハイ有効:信号がハイのときに操作が発生します。

- ロー有効:信号がローのときに操作が発生します。

📖 波形の読み方と解析

タイミング図の読み取りには体系的なアプローチが必要です。エンジニアは誤解を避けるために特定の手順に従うべきです。

ステップバイステップの解析

- クロックを特定する:主なタイミングリファレンスを特定する。すべての同期イベントはこれに関連する。

- データフローを追跡する: ソースから宛先までデータラインを追跡してください。

- タイミングウィンドウを確認する: クロックエッジに対してセットアップ時間およびホールド時間を確認する。

- 異常を確認する: グリッチ、スパイク、または予期しない遷移を特定する。

- 論理レベルを確認する: アクティブ状態がコンポーネント仕様と一致していることを確認する。

一般的な誤解

- 即時変化を仮定する: 実際の信号には立ち上がり時間および立ち下がり時間が存在する。垂直なエッジを仮定すると、タイミング違反が隠れてしまうことがある。

- 非同期信号を無視する: クロックされていない制御信号はいつでも出現する可能性があり、個別に確認する必要がある。

- アクティブ状態を誤読する: アクティブハイとアクティブローを混同することは、設計エラーの一般的な原因である。

🚀 高度なタイミングに関する考慮事項

システムが高速化するにつれて、タイミング解析はより複雑になる。高度な表記法がこれらの課題に対処する。

メタスタビリティ

シグナルがセットアップ時間またはホールド時間中に変化すると、出力がメタスタビリティ状態に入ることがある。

- 定義: シグナルは中間の電圧レベルに安定する。

- 表記: 通常、質問マークまたはHighとLowの間の陰影領域として表示される。

- 解消: シグナルは最終的にHighまたはLowに解消するが、その時間は予測できない。

同期遅延

異なるパスは、宛先に到達するまでに異なる時間が必要になることがある。

- クロック遅延: クロック信号は、異なるコンポーネントに異なるタイミングで到達する。

- データ遅延: データ信号は、異なる宛先に異なるタイミングで到達する。

- 表記:予想到着時刻と実際の到着時刻の間の水平方向のオフセットとして表示される。

ジッター

ジッターは、信号エッジが理想位置からずれる度合いを指す。

- サイクル間ジッター:1つのクロックサイクルと次のサイクルとの間の変動。

- 周期ジッター:クロックサイクルの全体的な持続時間の変動。

- 表記:通常、理想エッジ位置の周囲に陰影付き領域として表示される。

📝 ドキュメント作成のベストプラクティス

明確なタイミング図を作成することで、他者が設計を理解できるようになる。ベストプラクティスに従うことで、曖昧さが軽減される。

- 一貫した命名:すべての信号に明確で一意の名前を付ける。Signal1やSignal2のような一般的な名前は避ける。

- 標準記号:エッジ、レベル、遅延について標準的な表記を使用し、業界間の互換性を確保する。

- 明確な時間スケール:時間軸に単位(ns、µs、ms)を明示的にラベルする。

- 関連する信号をグループ化する:同じプロトコルまたはサブシステムに属する信号をまとめてグループ化する。

- 重要なタイミングを強調する:太線や色を使用して、セットアップ時間とホールド時間のウィンドウを強調する。

- 凡例を提供する:図に使用したカスタム記号や略語のキーを含める。

🔚 主なポイントのまとめ

タイミング図の表記は、デジタル設計に従事するすべての人にとって基本的なスキルである。コアコンポーネント、信号レベル、タイミングパラメータを理解することで、エンジニアは堅牢なシステム性能を確保できる。適切な表記は曖昧さを排除し、高コストな設計ミスを防ぐ。セットアップ時間とホールド時間に注目し、アクティブ状態を明確に定義し、伝播遅延やジッターなどの現実世界の信号特性を考慮することが重要である。これらのガイドラインに従うことで、明確で効果的なドキュメントが作成できる。

これらの図を作成またはレビューする際は、常に論理レベルをハードウェア仕様と照合すること。時間軸がシステムの実際の動作周波数を反映していることを確認する。最後に、すべてのドキュメントにおいて表記スタイルの一貫性を保つことで、協働を容易にする。練習を重ねることで、これらの図の解釈と作成は設計ワークフローの自然な一部となる。

実装に関する最終的な注意点

このガイドは理論的および表記的な側面をカバーしているが、実際の実装には物理層への注意が必要である。信号整合性、ノイズマージン、電源供給はすべてタイミング特性に影響を与える。常にタイミング図をデータシートやシミュレーション結果と照合して設計を検証する。継続的な学習と業界標準への準拠により、設計の信頼性と効率性を維持できる。