デジタル電子工学およびハードウェア工学の世界では、部品間の通信は正確な調整に依存しています。信号の状態がいつ変化するかを明確に理解しないと、システムは失敗します。タイミング図はこの調整のための設計図として機能します。時間の経過とともに信号間の関係を可視化し、データが有効で安定しており、処理の準備ができているかどうかを明らかにします。このガイドは、エンジニアや学生がこれらの重要な視覚的ツールを分析する際に直面する基本的な疑問に答えるものです。

マイコンインターフェースの設計、通信プロトコルのデバッグ、またはデジタル論理の学習を行っているかどうかに関わらず、設計の時間的側面を理解することは不可欠です。この記事では、タイミング図の構造を解説し、重要なパラメータを説明し、信号の整合性と同期に関する一般的な疑問に答えます。

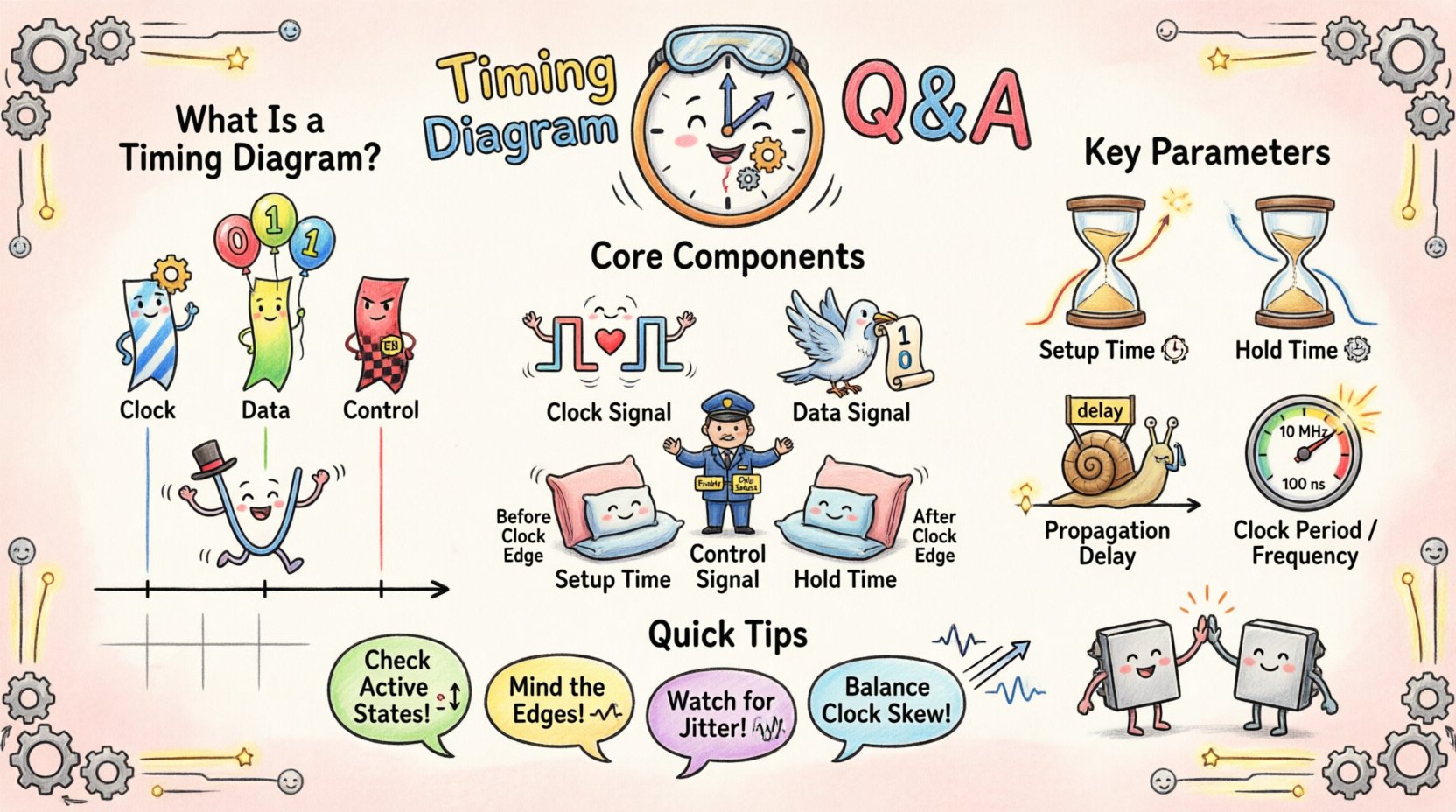

そもそもタイミング図とは何か? 📊

タイミング図は、システム内のイベントの順序をグラフィカルに表現したものです。信号レベルを水平方向の時間軸に対してプロットします。論理図が接続関係を示すのに対し、タイミング図は動作を示します。ある信号が他の信号よりも前または後に高または低に遷移するかどうかを確認できます。この視覚的な文脈は、次のクロックエッジが到着する前に受信機がデータを読み取るのに十分な時間が確保されているかどうかを検証するために不可欠です。

主な特徴には以下が含まれます:

- 時間軸:通常、左から右へ水平に進行する。

- 信号線:個々のワイヤーやデータバスを表す水平線。

- 論理レベル:高(1)および低(0)の状態は、明確な電圧の平坦部として描かれる。

- エッジ:一つの状態から別の状態への遷移を示す垂直線。

タイミング図の核心的な構成要素 🧩

これらの図を効果的に読み取るには、波形を構成する標準的な要素を特定する必要があります。各要素はシステムの同期において特定の役割を果たします。

| 構成要素 | 説明 | 視覚的インジケータ |

|---|---|---|

| クロック信号 | システムのハートビートを提供する。他の信号は通常、この信号を基準にサンプリングされる。 | 規則的な方形波パターン |

| データ信号 | 実際に転送されている情報を持ち運ぶ。 | 入力に基づく不規則な遷移 |

| 制御信号 | データの流れを管理する(例:Enable、チップ選択、Write)。 | アクティブハイまたはアクティブローパルス |

| セットアップ時間 | クロックエッジの前にデータが安定している必要がある期間。 | エッジ前の水平距離 |

| ホールド時間 | データはクロックエッジの後に安定した状態を維持しなければならない。 | エッジ後の水平距離 |

重要なタイミングパラメータの理解 ⚙️

タイミングパラメータは、デジタル回路が正しく動作する制約を定義する。これらのパラメータを違反すると、予測不能な動作が生じることが多い。以下の項目では、最も重要な指標の定義とその意味を説明する。

1. セットアップ時間 ⏳

セットアップ時間は、クロック信号のトリガーエッジの前にデータ信号が安定して保持される必要がある最小時間である。データがクロックエッジに近すぎるように変化すると、フリップフロップが値を正しくキャプチャできなくなる可能性がある。これは高速設計において最も重要な制約であり、動作の最大周波数を決定するためである。

2. ホールド時間 ⏳

ホールド時間は、クロック信号のトリガーエッジの後にデータ信号が安定して保持される必要がある最小時間である。セットアップ時間とは異なり、ホールド時間は一般的にクロック周波数に依存しない。これはフリップフロップの内部遅延とデータパスの外部伝播遅延に依存する。

3. 伝播遅延 ⏳

これは、信号がコンポーネントの入力から出力まで到達するまでの時間である。温度、電圧、製造公差によって変化する。タイミング図では、ある信号の変化とそれに伴う別の信号の変化との間の遅れとして現れる。

4. クロック周期と周波数 ⏳

クロック周期は、クロック信号の1回の完全なサイクルにかかる時間である。周波数は周期の逆数である。周期が短いほど周波数が高くなり、処理速度が向上するが、信号の安定性を保つための時間窓が狭くなる。

よくある質問 ❓

エンジニアはしばしば混乱を招く特定の状況に直面する。以下に、タイミング解析に関する最も重要な質問に対する詳細な回答を示す。

Q: セットアップ時間が違反されたらどうなるか? 🛑

セットアップ時間の要件を満たさない場合、フリップフロップは次のような状態に入る。メタスタビリティこの状態では、出力がすぐに有効な論理高または論理低に安定しない。代わりに、予測不能な時間にわたり振動したり、中間の電圧レベルに留まったりする可能性がある。これにより、下流の論理回路が破損した値を読み取る可能性があり、システムエラーまたはクラッシュを引き起こす。深刻な場合には、メタスタビリティが回路全体に伝播し、デバッグが困難な機能障害を引き起こすことがある。

Q: クロックスキーをどう扱うか? 🔄

クロックスキーとは、クロック信号が異なるコンポーネントに異なるタイミングで到達する現象である。これはパス長の違いや負荷の違いによって生じる。スキーを管理するためには、以下の対策を取る。

- ルーティングのバランス調整:クロックトレースが類似した長さと幅になるようにルーティングを確保する。

- バッファリング:クロックバッファを使用して、複数の負荷を均等に駆動する。

- タイミングマージン:セットアップ時間とホールド時間に十分な余裕を設けることで、微小なスキー変動を吸収できるようにシステムを設計する。

Q: 同期タイミングと非同期タイミングの違いは何ですか? ⚖️

In 同期システムでは、すべての操作が単一のクロック信号によって調整されます。これらのシステムのタイミング図では、規則的で繰り返されるクロックエッジが示されます。非同期システムでは、グローバルクロックなしで信号が動作をトリガーします。これらのシステムのタイミング図では、イベント駆動の遷移が示され、信号間の間隔に多くの変動が見られることがよくあります。非同期設計は分析が難しいですが、特定の低消費電力アプリケーションではより電力効率が良いことがあります。

Q: ジッタはタイミング図にどのように影響しますか? 📉

ジッタとは、信号が時間的に理想位置から短期間でずれる現象です。タイミング図では、クロック信号のエッジが本来の位置よりわずかに早くまたは遅く表示される形で現れます。過度なジッタはデータをキャプチャするための有効な時間窓を小さくします。結果として、セットアップ時間とホールド時間のマージンが狭くなり、タイミング違反のリスクが高まります。高速インターフェースでは、データ整合性を維持するために厳密なジッタ制御が必要です。

Q: クロックなしでタイミング図を読むことは可能ですか? 🕵️

はい、ただし別のアプローチが必要です。I2CやUARTなどの非同期プロトコルは、必ずしも共有クロックラインを使用するわけではありません。代わりに、事前に定義されたボーレートまたはハンドシェイキング信号に依存します。これらの図では、パルス幅や遷移間の時間を確認することで、データレートを推測しなければなりません。たとえばUARTでは、スタートビットの持続時間が、その後のデータビットのタイミングを定義します。

波形の読み方と解釈 🔍

タイミング図の解釈には体系的なアプローチが必要です。線をランダムにスキャンすると、詳細を見逃すことがあります。正確な分析を行うには、以下の手順に従ってください。

- 基準を特定する:クロック信号または主要な制御信号を見つけます。他のすべてのタイミングは、これに対して相対的に評価されます。

- アクティブ状態を確認する:信号がアクティブハイかアクティブローかを確認します。低パルスが「有効」を意味する場合もあり、高パルスが「無効」を意味する場合もあります。これは、回路図におけるピン名にバブル記号が付いていることで示されることがよくあります。

- エッジの同期を分析する:データエッジがクロックエッジとどのように一致しているかをよく観察します。データは理想的には、クロックが安定しているとき(例:ロー段階)に変化し、アクティブエッジの間に安定している必要があります。

- 依存関係をたどる:因果関係をたどります。信号Aが信号Bをトリガーする場合、それらの間に伝播遅延に対応する明確な遅延が存在するはずです。

- パルス幅を確認する:アクティブなパルスが受信部品によって検出できるほど十分に広いことを確認します。パルスがしすぎるとノイズとしてフィルタリングされる可能性があります。

図の解釈における一般的なミス ❌

経験豊富なエンジニアでも、特定の詳細を見落とすと図を誤解する可能性があります。これらの一般的な落とし穴を避けてください。

- 論理レベルを無視する:確認せずにすべての信号がアクティブハイであると仮定すること。常にデータシートや回路図を確認してください。

- 伝播遅延を無視する:信号が即座に変化すると仮定すること。現実の部品には有限の応答時間があります。

- 時間スケールを誤読する:時間単位(ナノ秒 vs マイクロ秒)に気づかないこと。ゆっくりズームしたときに安定しているように見える信号が、高速ズームではゴーストを示すことがあります。

- 電源状態を無視する:デバイスがスリープモードに入ると、タイミング図が変化することがよくあります。アクティブなタイミングシーケンスを見ていることを確認してください。

正確な分析のための戦略 🛠️

タイミング解析が堅牢であることを確実にするために、これらの戦略を採用してください。これらの手法は一貫性を保ち、誤りの可能性を低減します。

- グリッド線を使用する:図のグリッド線とカーソルまたはマーカーを合わせて、時間間隔を正確に測定します。

- 仮定を文書化する:解析を開始する前に、想定するクロック周波数と論理レベルを記録してください。これにより、後で混乱が生じるのを防ぎます。

- 相互確認する:タイミング図をステートマシンの論理と照合してください。すべてのステート遷移には対応するタイミングイベントが存在する必要があります。

- 変動をシミュレートする:最悪ケースを検討してください。温度が上昇して遅延が増加した場合、どうなるでしょうか?電圧が低下して駆動力が減少した場合、どうなるでしょうか?

- クリティカルパスに注目する:論理回路内の最長パスを特定してください。このパスがシステムの最大クロック周波数を決定します。これらの特定ルートに対してタイミング解析を優先してください。

タイミング違反の影響 ⚠️

タイミングがなぜ重要なのかを理解することは不可欠です。タイミング違反が発生すると、回路の物理的動作が変化します。最も一般的な結果はデータ破損です。レジスタが『0』をキャプチャすべきときに『1』をキャプチャする可能性があります。通信プロトコルでは、フレーミングエラーやパケット損失が発生します。制御システムでは、誤ったアクチュエータコマンドを引き起こす可能性があり、物理的損傷や安全上の危険を招くことがあります。

さらに、タイミング違反は間欠的な故障を引き起こすことがあります。システムが室温では完璧に動作するが、加熱すると故障するという状況が発生します。これは、伝播遅延が温度上昇とともに増加するためです。十分なタイミングマージンを確保して設計することで、こうした環境変化に対応できます。

タイミング図のベストプラクティス 📝

明確で正確なタイミング図を作成することは、練習を重ねるほど向上するスキルです。他の人が理解しやすい図を作成するために、以下のガイドラインに従ってください。

- すべてにラベルを付ける:すべての信号ラインには明確な名前を付ける必要があります。『Signal 1』のような一般的なラベルは避けてください。

- 一貫したスケールを使用する:特定のイベントをズームインする必要がある場合を除き、図全体で均一な時間スケールを維持してください。

- クリティカルイベントを強調する:セットアップ時間とホールド時間のウィンドウを、異なる色や太い線でマークしてください。

- 注釈を含める:複雑な相互作用や特定の制約を説明するために、テキストノートを追加してください。

- データシートで検証する:常に図のパラメータを、公式な部品仕様と照合してください。

高度な考慮事項:マルチクロックドメイン 🌐

現代のシステムはしばしば複数のクロックドメインを使用します。たとえば、プロセッサが2 GHzで動作している一方で、メモリコントローラーは400 MHzで動作していることがあります。こうしたシステムのタイミング図は、はるかに複雑になります。以下の点を考慮しなければなりません:

- クロスクロックサンプリング: データが一つの周波数から別の周波数へどのように移動するか。

- FIFOバッファ:非同期クロック間のデータフローを同期する方法。

- リセット同期:すべてのドメインが連携してリセットされるようにし、状態の不整合を回避する。

これらの図を分析する際は、ハンドシェイク信号や同期器チェーンなどの同期論理を探してください。これらのコンポーネントは、異なるタイミングドメインの間を安全に橋渡しするように設計されています。

結論:正確さが鍵です 🔑

タイミング図は単なる図面以上のものであり、動作するシステムの数学的証明です。信頼性と性能の限界を定義します。基本的なコンポーネント、パラメータ、および潜在的な落とし穴を理解することで、現実世界の条件下でも正しく動作するシステムを設計できます。セットアップ時間、ホールド時間、伝播遅延への注意は、機能するプロトタイプと量産可能な製品を分けるものです。これらの図を読み書きする継続的な練習は、技術的直感を鋭くし、エンジニアリングの成果を向上させます。

すべてのエッジが情報の流れについて物語を語っていることを思い出してください。その情報が伝わるのにかかる時間を尊重すれば、あなたの設計は時代の試練に耐えるでしょう。