組み込み工学の複雑な世界において、正確さは単なる好みではなく、必須である。タイミング図は、信号が時間とともにどのように相互作用するかを理解するための視覚的設計図として機能する。これらの図形的表現は、電圧レベル、クロックサイクル、データ遷移を時間軸に対してマッピングする。マイコン、センサ、通信インターフェースを設計するエンジニアにとって、これらの図の読み方と作成方法を習得することは、システムの信頼性を確保するために不可欠である。

時間的関係を明確に把握できない場合、ハードウェア部品同士が通信できず、データ破損やシステムクラッシュを引き起こす可能性がある。このガイドでは、組み込み開発のさまざまな分野におけるタイミング図の実用的応用を検討し、特定のソフトウェアツールに依存せずにその有用性を深く掘り下げる。

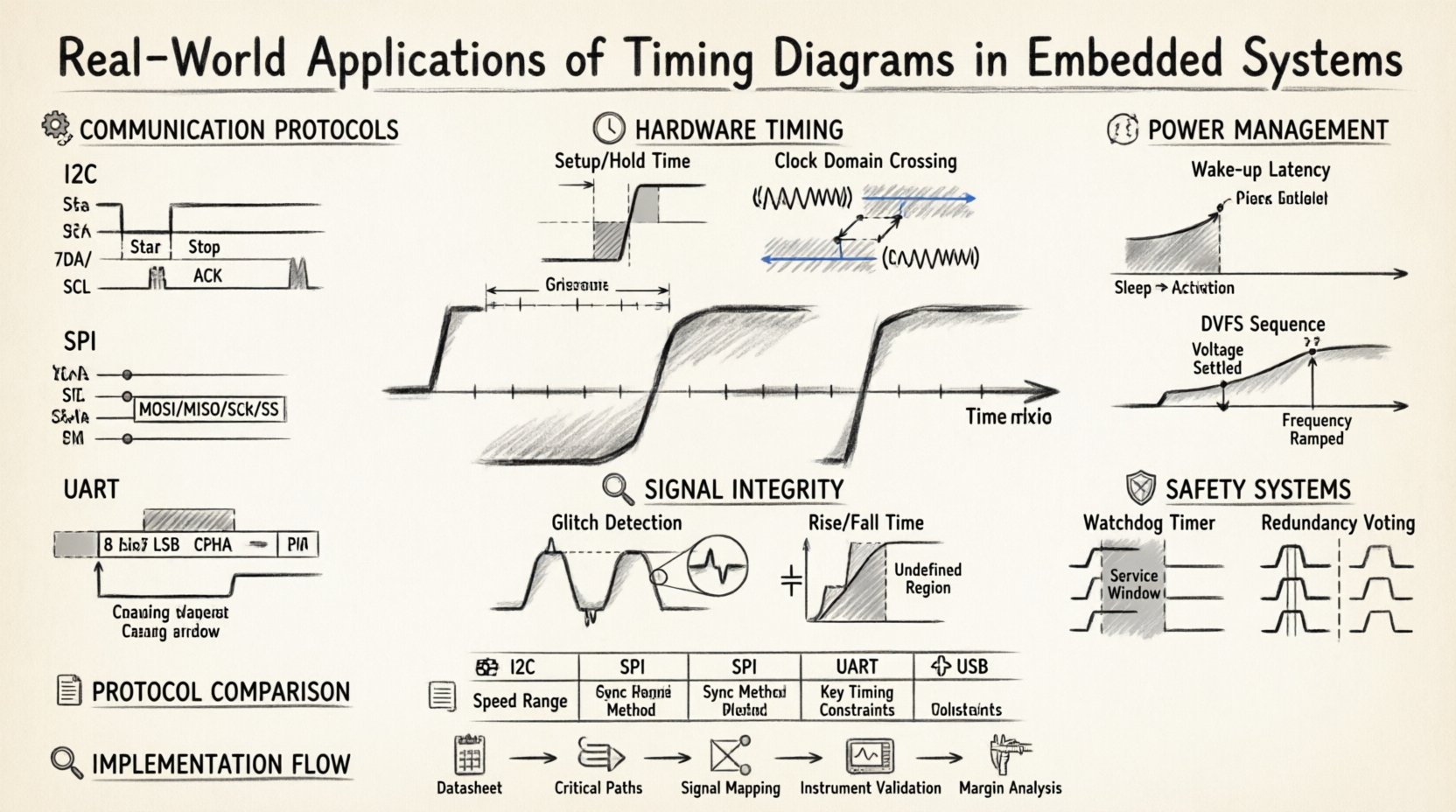

🔌 通信プロトコルの解析

シリアル通信は現代の組み込みシステムの基盤である。データはほとんど常に1つのチップ内に留まらず、プロセッサ、メモリ、周辺機器の間を移動する。タイミング図は、これらの相互作用を定義し、検証するために不可欠である。

相互統合回路(I2C)

I2Cプロトコルは、2線式インターフェース(シリアルデータ(SDA)とシリアルクロック(SCL))を用いる。I2Cのタイミング図は、データ送信に必要な特定のシーケンスを明らかにする。

- 開始条件: SDAラインが高から低に遷移する際、SCLラインは高のまま維持される。これによりバスがトランザクションの開始を示す。

- アドレスフレーム: 送信される最初のバイトには、ターゲットデバイスの7ビットアドレスに加えて、読み取り/書き込みビットが含まれる。

- アックノリージメント: 受信側は、9番目のクロックパルス中にSDAラインを低に引き下げることで、受信を確認する。

- 停止条件: SCLが高の間にSDAラインが低から高に遷移し、バスを解放する。

エンジニアはこれらの図を、クロックストレッチのような問題を検出するために使用する。スレーブデバイスがデータを十分に速く処理できない場合、SCLラインを低に保持する。タイミング図はこの延長を示し、設計者が処理ループやバッファサイズを調整できるようにする。

シリアル周辺インターフェース(SPI)

SPIは、高速通信に頻繁に使用される同期プロトコルである。4本のラインを用いる:マスター出力スレーブ入力(MOSI)、マスター入力スレーブ出力(MISO)、シリアルクロック(SCK)、スレーブ選択(SS)。

- クロック極性(CPOL): クロックラインのアイドル状態を決定する。データ送信が始まる前に、高か低か?

- クロックフェーズ(CPHA): データがサンプリングされるタイミングを定義する。最初のクロックエッジか、2番目のクロックエッジか?

- チップ選択タイミング: SSラインは、トランザクション全体の間、低のまま維持されなければならない。もし高に誤動作(グリッチ)すると、トランザクションは中止される。

これらのフェーズを理解することは非常に重要である。マスターとスレーブの間でCPOLまたはCPHAが不一致になると、ゴミデータが発生する。タイミング図はこれらのエッジを可視化するため、ハードウェア起動時に不一致を簡単に発見できる。

汎用非同期受信送信機(UART)

SPIやI2Cとは異なり、UARTはクロックラインを使用しない。同期は合意されたボーレートに依存する。ここでのタイミング図は、ビット持続時間とフレー�밍に焦点を当てる。

- スタートビット: 低パルスはバイトの開始を示す。

- データビット: 通常8ビットで、最下位ビット(LSB)から先に送信される。

- ストップビット: 高電位のパルスがバイトの終了を示す。

時系列図はエンジニアが許容範囲を計算するのを助けます。2つのデバイスのクロックが離れすぎると、サンプリングポイントがずれ、誤りが生じます。図はサンプリングウィンドウを示しており、通常ビット時間の中央に位置します。

⏱️ ハードウェア同期とセットアップ時間

通信を超えて、時系列図は論理ゲートやフリップフロップの相互作用を理解するために不可欠です。デジタル論理は正確なタイミング制約に依存して正しく動作します。

セットアップ時間とホールド時間

データがレジスタやフリップフロップに入力される際、クロックエッジに対して特定のタイミング要件を満たす必要がある。

- セットアップ時間: データが安定している必要がある最小時間クロックエッジが到着する後

- ホールド時間: データが安定したまま維持される必要がある最小時間クロックエッジが到着した後後

信号がセットアップ時間を違反すると、レジスタが誤った値をキャプチャする可能性がある。ホールド時間を違反すると、メタスタビリティが発生する。時系列図はデータ信号とクロックエッジの関係を可視化し、データの変化が許されない禁止領域を強調する。

クロックドメインクロッシング(CDC)

複雑なシステムでは、論理の異なる部分が異なるクロック周波数で動作することが多い。高速なクロックドメインから低速なドメインへ、またはその逆にデータを移動するとリスクが生じる。

- 同期: 使用する前に信号が安定していることを保証するために、フリップフロップのチェーンを使用する。

- ハンドシェイキング: 共通のクロックなしでデータ転送を調整するために、リクエスト信号とアックノリッジ信号を使用する。

CDC用の時系列図はハンドシェイクの順序を示す。受信ドメインが確認する前にデータが有効であることを保証する。これにより、非同期転送におけるデータ損失を防ぐ。

🔍 デバッグと信号整合性

組み込みシステムが予期しない動作をした場合、エンジニアはしばしば時系列図を最初に確認する。静的テストでは捉えきれない信号の動作履歴を提供する。

ギャップの特定

ギャップとは、信号ライン上に発生する短時間の意図しないパルスである。数ナノ秒しか持続しないこともあるが、フリップフロップの状態変化を引き起こす可能性がある。

- レースコンディション: イベントの順序が重要であり、タイミングが極めてタイトな場合に発生する。

- 伝播遅延:信号は論理ゲートを通過するのに時間がかかります。タイミング図はこれらの遅延を明確に示します。

想定されるタイミング図とキャプチャされた実際の信号を重ね合わせることで、エンジニアはずれが発生する正確な場所を特定できます。これにより、ファームウェアまたはハードウェア設計における的確な修正が可能になります。

ノイズマージンと立ち上がり/立ち下がり時間

実際の信号は完璧な矩形波ではありません。配線の静電容量やインダクタンスにより、立ち上がり時間と立ち下がり時間が生じます。

- 立ち上がり時間:信号が低電位から高電位へ遷移するのに要する時間。

- 立ち下がり時間:信号が高電位から低電位へ遷移するのに要する時間。

これらの遷移が遅すぎると、信号が論理0と論理1の間の定義されていない電圧領域に長く滞在する可能性があります。これにより、複数のクロックエッジが発生するか、論理エラーが生じる恐れがあります。タイミング図はこれらの傾斜を測定し、受信チップの仕様を満たしているかを確認するのに役立ちます。

💤 電源管理と低消費電力状態

エネルギー効率は、バッテリー駆動の組み込みデバイスにおいて大きな関心事です。タイミング図は電力消費の最適化に役立ちます。

ウェイクアップ遅延

デバイスがスリープモードに入ると、電力を節約するためにクロックを停止します。ウェイクアップにはクロックの復元と電圧の安定化が必要です。

- 遷移時間:スリープ状態からアクティブ状態へ移行するのに要する時間。

- 遅延:ウェイクアップイベントとプロセッサがコードを実行するまでの遅延。

電源投入シーケンスのタイミング図は、トリガ信号とシステムクロックが安定するまでの遅延を示します。この情報は、数ミリ秒の遅延が問題となるリアルタイムアプリケーションにおいて極めて重要です。

動的電圧・周波数スケーリング(DVFS)

システムは負荷に応じて電圧と周波数を調整する場合があります。タイミング図は、異なる性能状態間の遷移を検証するのに役立ちます。

- 周波数ラムプ:クロックは滑らかに変化するか、急激に変化するか?

- 電圧安定化:新しい周波数が適用される前に、電圧は安定していますか?

DVFS中にシーケンスが誤ると、ブラウンアウトや論理エラーが発生する可能性があります。タイミング図は安全な遷移を確保するために必要なシーケンスの検証を提供します。

🛡️ セーフティクリティカルシステム

自動車、医療、産業分野において、安全性は最優先事項です。タイミング図は、セーフティメカニズムが要求される時間制限内に機能していることを検証するために使用されます。

ウォッチドッグタイマー

ソフトウェアがフリーズした場合、ウォッチドッグタイマーがシステムをリセットします。タイミング図はタイムアウト期間を定義します。

- タイムアウト期間:リセット間で許容される最大時間。

- サービスウィンドウ:ソフトウェアがタイマーをリセットする時間。

サービスウィンドウが長すぎると、ウォッチドッグが不要なタイミングでトリガーされる可能性があります。逆に短すぎると、遅延した割り込みが誤ったリセットを引き起こす可能性があります。図はタイミングが安全基準の要件と整合していることを保証します。

冗長性と投票

一部のシステムでは、複数のプロセッサを使用して正しい出力を投票します。タイミング図により、すべてのプロセッサが同時に投票段階に到達することを確認します。

- 同期:すべてのチャネルがデータを同期させる必要があります。

- タイムアウト:1つのチャネルが遅れると、システムはその差異を検出しなければなりません。

ブレーキ制御やステアリングシステムでは、遅延が危険な場合があるため、これが非常に重要です。タイミング図により、各チャネルの遅延をマッピングし、投票論理が正しく動作することを確認します。

📋 プロトコル比較概要

以下の表は、一般的な組み込みインターフェースの主要なタイミング特性を要約し、選定や設計を支援します。

| プロトコル | 速度範囲 | 同期方法 | 代表的な使用例 | 主要なタイミング制約 |

|---|---|---|---|---|

| I2C | 100 kHz ~ 3.4 MHz | 共有クロック | センサー、EEPROM | クロックストレッチング |

| SPI | 1 MHz ~ 50 MHz以上 | マスタクロック | フラッシュメモリ、ディスプレイ | チップセレクトのセットアップ |

| UART | 9600 から 921600 bps | 非同期 | デバッグ、GPS、Bluetooth | ボーレート許容範囲 |

| USB | 1.5 Mbps から 20 Gbps | パケットベース | 周辺機器、ストレージ | トークン/ハンドシェイクタイミング |

🛠️ 実用的な実装ステップ

タイミング図を作成するには体系的なアプローチが必要です。仕様の理解から始まり、検証で終わります。

- データシートを確認する:すべてのコンポーネントにはタイミングセクションがあります。AC特性テーブルを探してください。

- 重要なパスを特定する:システムの最大速度を決定する信号を特定します。

- 依存関係をマッピングする:信号間の関係を図示します。どちらがどちらをトリガーするのですか?

- 計測機器で検証する:ロジックアナライザーやオシロスコープを使用して、実際の波形をキャプチャします。

- マージンを分析する:温度や電圧の変動を考慮するため、信号間に十分な時間が確保されているか確認します。

ドキュメント作成が重要です。適切に注釈が付けられたタイミング図は、将来の保守作業の参考になります。特定の遅延が追加された理由や、特定のプルアップ抵抗が選ばれた理由を説明します。

🚀 レベルの高い考慮事項

システムがより複雑になると、タイミング解析にはより深い注意が必要になります。

ジッターと位相ノイズ

クロックは完全に安定しているわけではありません。ジッターとは、クロックエッジが理想位置からずれる量です。タイミング図は、複数サイクルにわたるエッジ配置の変動を示します。

- 周期ジッター:クロック周期の変動。

- サイクル間ジッター:1サイクルから次のサイクルへの変動。

高いジッターはセットアップ時間とホールド時間の余裕を減少させる。DDRメモリのような高速インターフェースでは、これにより読み取り/書き込みエラーが発生する可能性がある。タイミング図はこのジッターを定量化するのに役立ち、許容範囲内に保つことを確認する。

熱的影響

温度はトランジスタの速度に影響を与える。チップが加熱されると、信号の伝搬が遅くなる。

- 最悪ケース解析:最大動作温度を想定して設計する。

- 熱制限(Thermal Throttling):高速動作中にシステムが安全な熱限界を超えないようにする。

室温で作成されたタイミング図が85°Cでは成立しないことがある。エンジニアはこれらの熱的シフトを考慮し、システムの信頼性を確保しなければならない。

📝 最後の考察

タイミング図は単なる図面以上のものである。それは同期の言語である。理論的な論理と物理的な現実の間の橋渡しを行う。ハードウェアとソフトウェアが複雑に絡み合う埋め込みシステムにおいて、信号タイミングの明確な理解は高コストな再設計を防ぎ、信頼性を確保する。

通信プロトコルのデバッグ、電力消費の最適化、あるいは重要なシステムにおける安全性の確保にかかわらず、これらの図は情報に基づいた意思決定に必要な明確さを提供する。セットアップ時間、伝播遅延、信号整合性に注目することで、エンジニアは現実の環境下でも一貫した性能を発揮するシステムを構築できる。

タイミング関係を理解するための投資は、安定性と性能の向上という形で報われる。技術が進化しても、その原理は変わらない。時間は常に一定であり、その測定を習得することが、成功した埋め込み設計の鍵となる。