デジタルシステムの複雑なアーキテクチャにおいて、信号の状態が変化する正確な瞬間を理解することは極めて重要です。タイミング図は、信号が時間とともにどのように変化するかを視覚的に表現するものです。コンポーネントが正しく相互作用しているかを検証する必要があるエンジニア、開発者、デザイナーにとって、これらは不可欠なツールです。これらの視覚的補助がなければ、非同期通信のデバッグやクロックドメインの検証は、当てずっぽうの作業になってしまいます。このガイドでは、タイミング図のメカニズム、利点、およびシステム設計における応用について探ります。

タイミング図とは何か? ⚙️

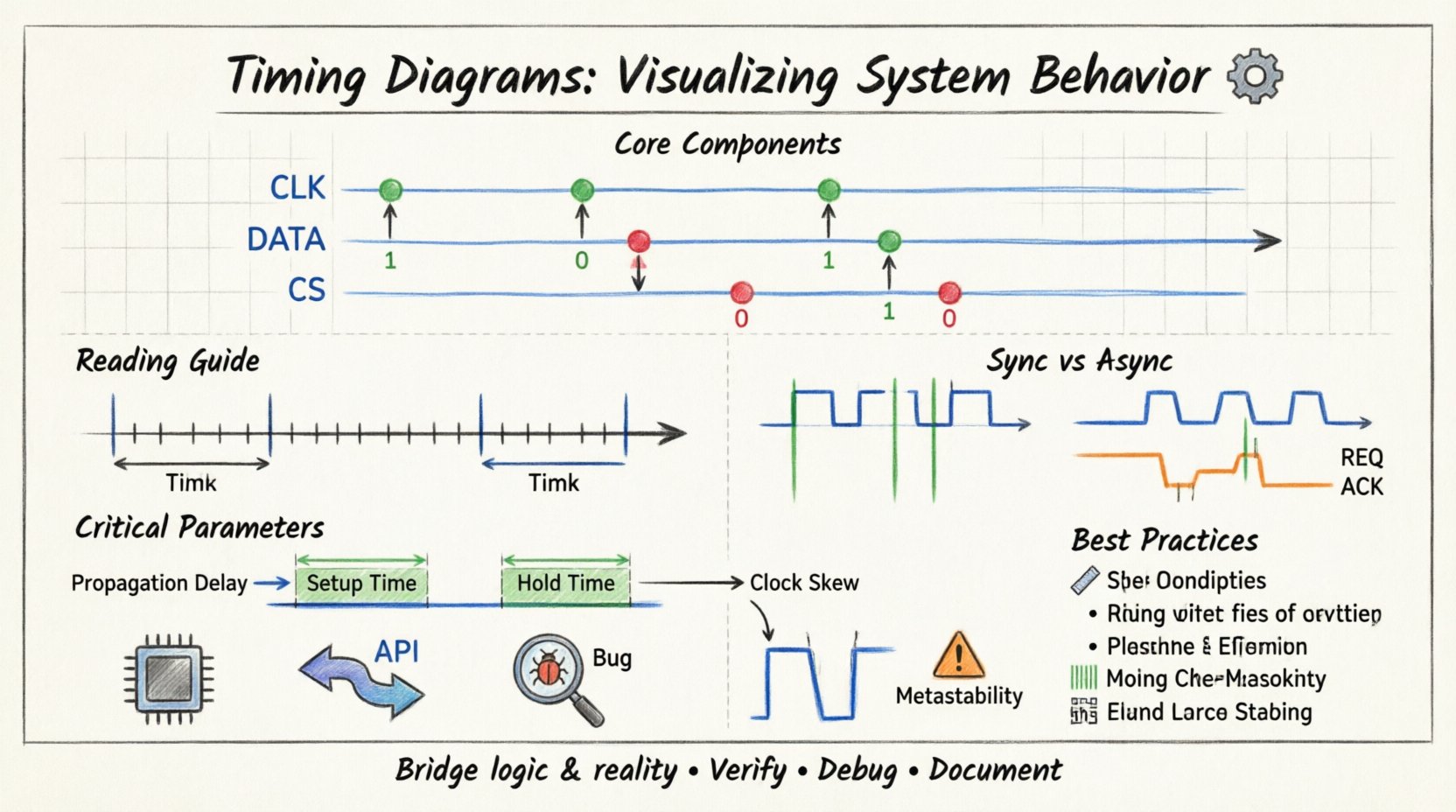

タイミング図は、一定期間における信号の動作を表示するグラフです。信号の論理状態をタイムラインに対してマッピングします。回路図が物理的な接続を示すのに対し、タイミング図はイベント間の時間的関係に注目します。たとえば、信号Aが信号Bより先に変化するか?クロックパルスは十分に広いのか?データが安定するまでにどれくらいの時間がかかるか?といった質問に答えることができます。

これらの図は、以下のような場面で基本的です:

- ハードウェアプロトコルの検証

- ソフトウェア論理の相互作用の文書化

- ラ race条件のデバッグ

- クロックとデータの同期の検証

タイミング図の核心的な構成要素 🧩

タイミング図を効果的に解釈するためには、その構成要素を理解する必要があります。すべての図は、システムの動作に関する情報を伝える特定の要素で構成されています。

1. 時間軸 📏

水平軸は時間を表します。通常、左から右へと流れます。スケールは絶対的(ナノ秒、マイクロ秒)または相対的(クロックサイクル)です。同期システムでは、時間はクロックエッジに対応する離散的なステップに分けられることが多いです。

2. シグナルライン 📡

各ラインは特定の信号、配線、またはデータバスを表します。これらのラインは「CLK」、「DATA」、「CS」(チップセレクト)や「RST」(リセット)などの名前でラベル付けされます。CLK, DATA, CS(チップセレクト)、またはRST(リセット)。ラインの垂直方向の位置によって、異なる信号を明確に区別し、混乱を避けています。

3. ロジックレベル 🟢🔴

信号は通常、離散的な状態にあります。デジタル論理では、これらはハイ(論理1)とロー(論理0)です。タイミング図はこれらの状態間の遷移を示します。ローからハイへの遷移はリジングエッジ、ハイからローへの遷移はフェーリングエッジと呼ばれます。

4. イベントと遷移 🔄

イベントは、信号の状態が変化する特定の瞬間を指します。これらはしばしば垂直線や矢印で示されます。重要なイベントにはクロックエッジ、データラッチ、確認信号などが含まれます。これらのイベント間の間隔が、持続時間を示しています。

タイミング図の効果的な読み方 👁️

これらの図を読むには体系的なアプローチが必要です。イベントの順序を誤解すると、設計上の欠陥につながります。正確さを確保するために、以下の原則に従いましょう。

- 左から右へ: 時系列図は常に左端(開始)から右端(終了)へと読み進めてください。これは操作の時系列的な流れを表しています。

- 垂直方向の揃え: 垂直方向に揃っているイベントは同時に発生します。2つの信号が同じ垂直線上で変化する場合、それらは並行して発生しています。

- 持続時間: シグナルの状態の水平方向の長さは、その状態がどのくらい続くかを示します。広いパルスは、長い持続時間であることを意味します。

- 依存関係: 因果関係を探してください。あるシグナルの変化が、別のシグナルの変化を引き起こすことがよくあります。図はこれらのトリガー間の遅延を示しています。

同期型と非同期型のシステム 🔄

タイミング図は、システムが同期型か非同期型かによって大きく異なります。この違いを理解することは、正確な解析にとって不可欠です。

同期型システム ⏰

これらのシステムはグローバルなクロック信号に依存しています。すべての状態変化は特定のクロックエッジ(立ち上がりまたは立ち下がり)で発生します。図には規則的なクロックパターンが表示されます。データはクロックが許可するときのみサンプリングされます。これによりタイミングが予測可能になりますが、セットアップ時間やホールド時間といった制約が生じます。

非同期型システム 🕰️

これらのシステムはグローバルクロックに依存しません。状態変化は入力信号が変化したときに発生します。ここでのタイミング図は比較的不規則です。ハンドシェイキングプロトコルに注目します。1つの信号がハイになる、次に別の信号がハイになる、その後両方ともローに戻る必要があります。これにより、ラス条件を防ぐために遅延の詳細な分析が必要です。

タイミング解析における重要なパラメータ ⚙️

単に線を引くだけではなく、エンジニアは信頼性を確保するために特定のパラメータを分析します。これらのパラメータは、システムが正しく動作するための時間窓を定義します。

- 伝播遅延: シグナルがコンポーネントを介して入力から出力へと伝わるまでの時間です。この遅延は論理ゲートを跨いで蓄積されます。

- セットアップ時間: クロックエッジの直前、データが安定している必要がある最小時間です。データが遅れて変化すると、フリップフロップは正しくそれをキャプチャできません。

- ホールド時間: クロックエッジの直後、データが安定したまま維持される必要がある最小時間です。データが早すぎると、現在の値が失われます。

- クロックスキュー: クロック信号が異なるコンポーネントに到着する時間の差です。高いスキーはセットアップまたはホールド違反を引き起こす可能性があります。

- メタスタビリティ: フリップフロップの出力がハイでもローでもない状態です。セットアップ時間またはホールド時間が違反されたときに発生します。タイミング図は、メタスタビリティのリスクを可視化するのに役立ちます。

ハードウェアおよびソフトウェアにおける応用 🔌

タイミング図はハードウェアに限定されるものではありません。ソフトウェアアーキテクチャやプロトコル設計においても広く使用されています。

ハードウェア設計

ハードウェアでは、これらの図はバスプロトコルの検証に使用されます。たとえば、リードストローブがアクティブになる前にアドレスバスが安定していることを確認するなどです。メモリアクセス時間とプロセッサのクロック速度が一致していることを保証します。また、信号遷移中の電力消費のピークを分析するのにも使用されます。

ソフトウェアとプロトコル

ソフトウェアでは、タイミング図はAPI呼び出しやメッセージの交換をマッピングします。サービス間のリクエストとレスポンスの順序を示します。これにより分散システムにおけるレイテンシの問題を特定するのに役立ちます。マルチスレッド環境における操作の順序を明確にします。

一般的な落とし穴とエラー 🛑

タイミング図を作成したり読んだりする際には、注意が足りないとエラーを引き起こすことがあります。一般的なミスに注意を払うことで、正確性が向上します。

- アクティブローを無視する:多くの信号はアクティブロー論理(反転)を使用しています。ラインがローに下がる場合、信号がアクティブであることを意味することがあります。常に凡例やラベルを確認してください。

- 瞬時遷移を仮定する:実際の信号には立ち上がり時間と立ち下がり時間が存在します。理想的な図では垂直線が描かれますが、物理的な信号は傾斜します。この傾斜は信号整合性に影響を与えます。

- ゴーストを無視する:最小幅要件を満たさない短いパルスは、誤動作を引き起こすことがあります。これらはしばしばゴーストと呼ばれます。

- ハイインピーダンスを誤解する:ハイインピーダンス状態は、信号が接続解除されていることを意味します。図では破線や特定の記号として表示されます。これを無視すると、バス競合エラーが発生する可能性があります。

- クロックの誤った同期:すべてのクロックが位相同期していると仮定するが、実際はそうではない。スケューにより、データが誤ってサンプリングされることがあります。

図の種類の比較 📊

異なる文脈には、異なる可視化手法が必要です。タイミング図は強力ですが、唯一のツールではありません。

| 図の種類 | 主な焦点 | 最も適した用途 |

|---|---|---|

| タイミング図 | 時間と信号状態 | クロック/データ関係の検証 |

| ステート図 | システム状態 | 論理フローと条件の定義 |

| シーケンス図 | メッセージの順序 | ソフトウェア間の相互作用とAPI呼び出し |

| 回路図 | 物理的接続 | 配線と部品配置 |

| 波形ビューア | リアルタイム信号 | 実際のハードウェア動作のデバッグ |

ドキュメント作成のベストプラクティス 📝

タイミング図をチームや将来の参照に役立つものにするためには、以下のベストプラクティスに従ってください。明確なドキュメント作成は曖昧さを減らし、デバッグを迅速化します。

- すべてにラベルを付ける: すべての信号ラインには明確な名前を付ける必要があります。「Sig1」のような一般的なラベルは避けてください。Sig1.

- 単位を含める: 軸に時間の単位を明記してください。ミリ秒かクロックサイクルのどちらを参照しているのでしょうか?

- 重要なポイントをマークする: ライズとホールドのウィンドウを明確に強調してください。重要なタイミングウィンドウを示すために、陰影や異なる色を使用してください。

- 整理整頓する: 関連する信号をまとめて配置してください。たとえば、すべての制御信号を上部に、データ信号を下部に配置します。

- 仮定をドキュメント化する: 作成中に仮定した内容を記録してください。たとえば、伝播遅延をゼロと仮定する、または特定の負荷条件を想定するなどです。

- 一貫した表記を使用する: 上昇エッジ、下降エッジ、高インピーダンス状態には標準的な記号を使用してください。

図の作成手順ガイド 🛠️

タイミング図をゼロから作成するには、構造的なアプローチが必要です。完全性を確保するために、以下のステップに従ってください。

- 信号を特定する: 連携に関与するすべての入力と出力をリストアップしてください。

- 順序を決定する: イベントの順序を定義してください。プロセスを開始するのは何ですか?

- 時間スケールを設定する: 時間軸の細かさを決定してください。

- クロックを描く: 同期の場合、まずクロック信号を描いてください。これにより図の他の部分が固定されます。

- データを追加する: データ信号をクロックエッジに対してプロットする。

- 制約の確認: 図示された信号に対して、セットアップ時間およびホールド時間を確認する。

- レビュー: タイムラインを確認して、論理的なギャップがないことを確認する。

デバッグにおけるタイミングの役割 🐞

システムが故障したとき、タイミング図はしばしばエンジニアが最初に確認する場所である。これは問題が論理的か時間的かを特定するのに役立つ。論理は正しいがタイミングがずれている場合、システムは間欠的に故障する。これはハードな論理エラーよりも再現が難しいことが多い。

デバッグのシナリオには以下が含まれる:

- データ破損: 読み取り中に信号が変化している。

- ミスした割り込み: 検出できないほど短い割り込み信号。

- バス競合: 2つのデバイスが同時にバスを駆動している。

- クロックドメイン遷移: 適切な同期なしに、異なるクロック周波数間を信号が移動している。

データ幅とアラインメントの理解 📐

タイミング図はデータ幅も可視化する。並列バスは複数のラインを必要とする。各ラインは同期して遷移しなければならない。アラインメントのずれはデータエラーを引き起こす可能性がある。図は、クロックサイクル内でのビットのアラインメントを示す。シリアル通信では、タイミング図はビットストリームを示す。ビット期間とサンプリングポイントを強調する。

応用トピック:ジッターとノイズ 📉

現実の信号は完璧ではない。ジッターとは、クロックエッジが理想位置からずれる現象である。ノイズとは、信号レベルのランダムな変動である。タイミング図では、鋭い線ではなく太い帯をエッジの周囲に表示することでジッターを表現できる。これは不確実性を示す。設計者は、システムがこの不確実性を許容できることを確認しなければならない。ジッター帯とセットアップ/ホールドウィンドウとの間の余裕が、安全余裕である。

テストスイートとの統合 🧪

タイミング図は設計だけに使われるわけではない。テストケースの生成にも使われる。自動テストスイートは、実際のシステム動作が図と一致しているかを確認できる。測定されたタイミングが許容範囲を超えてずれている場合、テストは失敗する。これにより、ハードウェアまたはソフトウェアがライフサイクル全体を通じて仕様を満たしていることが保証される。

システム可視化に関する結論 🎯

タイミング図はシステムエンジニアリングの基盤のままである。抽象的な論理と物理的な現実の間の橋渡しを行う。時間と信号の流れを可視化することで、エンジニアは故障を発生する前に予測できる。ハードウェアチームとソフトウェアチーム間のコミュニケーションを促進する。よく描かれた図は、何ページものテキストよりも多くの情報を伝える。システムがより高速かつ複雑になるにつれて、正確なタイミング解析の必要性が高まる。これらの図の習得は、堅牢で信頼性の高い設計を保証する。

明確さと正確さを最優先にすることを忘れないでください。仮定を避ける。すべての遷移を確認する。練習を重ねることで、これらの図の読み取りと作成は設計プロセスの直感的な一部になる。それらは、デジタル論理の風景を旅する旅人を導く地図である。