W świecie elektroniki cyfrowej i projektowania systemów czas nie jest tylko wymiarem; jest kluczowym parametrem, który decyduje o tym, czy układ działa poprawnie, czy katastrofalnie się zawiesza.Schematy czasowesłużą jako język wizualny, którego inżynierowie używają do komunikowania się o zachowaniu sygnałów w czasie. Niezależnie od tego, czy projektujesz interfejs mikrokontrolera, debugujesz magistralę pamięci, czy analizujesz transmisję danych o wysokiej prędkości, zrozumienie tych schematów jest nie do odmówienia.

Ten przewodnik bada mechanizmy schematów czasowych, rozkładając złożone zachowania sygnałów na zrozumiałe elementy. Przejdziemy od podstawowych definicji do zaawansowanych technik analizy, zapewniając Ci narzędzia do precyzyjnego interpretowania przebiegów sygnałów.

🔍 Co to jest schemat czasowy?

Schemat czasowy to graficzne przedstawienie sekwencji zmian sygnałów w systemie cyfrowym. W przeciwieństwie do schematu, który pokazuje, jak komponenty są połączone, schemat czasowy ilustrujekiedy te połączenia zmieniają stan. Mapuje aktywność sygnałów wzdłuż poziomej osi czasu, umożliwiając projektantom weryfikację, czy dane są stabilne przed krawędzią zegara, czy sygnały sterujące są aktywne w odpowiednim momencie.

Te schematy są niezbędne do:

- Weryfikacji interakcji między sprzętem a oprogramowaniem.

- Debugowania protokołów komunikacji.

- Zapewnienia spełnienia wymagań czasu ustawienia i czasu utrzymania.

- Dokumentowania zachowania systemu w celu późniejszej konserwacji.

Bez jasnego zrozumienia czasu nawet układ logicznie poprawny może zawieść z powodu wyścigów sygnałów lub metastabilności.

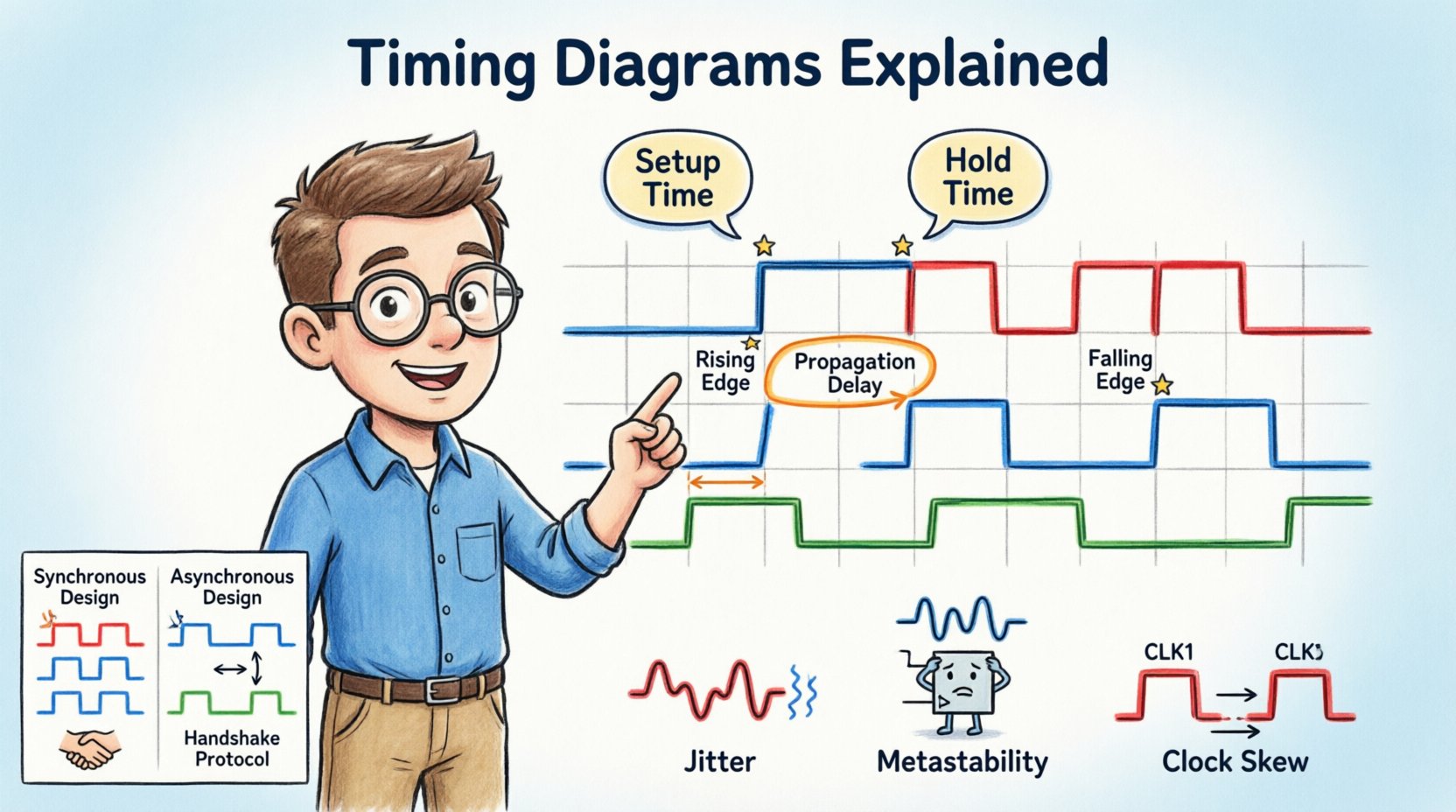

🛠️ Podstawowe elementy schematu czasowego

Aby skutecznie odczytywać schemat czasowy, musisz zidentyfikować jego podstawowe elementy budowlane. Każdy element zawiera określoną informację dotyczącą stanu i przepływu systemu cyfrowego.

1. Oś czasu

Pozioma linia reprezentuje postęp czasu. Zazwyczaj przepływa od lewej do prawej. W szczegółowych dokumentach technicznych oś ta może być oznaczona konkretnymi jednostkami czasu (nanosekundy, pikosekundy) lub cyklami zegara.

2. Linie sygnałów

Linie pionowe reprezentują poszczególne sygnały, takie jak linie zegara, magistrale danych lub linie sterujące (np. wybór mikrochipu lub odczyt/zapis). Każda linia odpowiada konkretnemu węzłowi w obwodzie.

3. Poziomy logiczne

Sygnały zazwyczaj istnieją w jednym z dwóch stanów:

- Wysoki (logika 1 / VCC):Często reprezentowany linią na szczycie toru sygnału.

- Niski (logika 0 / GND):Reprezentowany linią na dole toru sygnału.

Niektóre systemy używająaktywnego niskiegologiki, w której sygnał wykonuje swoją funkcję, gdy napięcie jest niskie. W schematach często oznacza się to kropką przy nazwie sygnału lub specjalnym oznaczeniem.

4. Przejścia

Przejścia to chwile, w których sygnał zmienia się z wysokiego na niski lub z niskiego na wysoki.

- Krawędź narastająca:Przejście od niskiego do wysokiego. Kluczowe do wyzwalania zdarzeń.

- Krawędź spadająca:Przejście od wysokiego do niskiego. Używane do określonych sekwencji sterowania.

- Wyzwalane krawędzią:Sygnał jest oceniany tylko podczas przejścia, a nie w stanie ustalonym.

⚙️ Kluczowe parametry czasowe

Dokładny projekt cyfrowy opiera się na ilościowym określeniu związku między sygnałami. Poniższe parametry są fundamentem analizy czasowej.

1. Opóźnienie propagacji (tpd)

Jest to czas potrzebny sygnałowi na przejście od wejścia bramki logicznej lub komponentu do jego wyjścia. Żaden sygnał nie zmienia się natychmiast; ograniczenia fizyczne powodują opóźnienie.

- Znaczenie:Jeśli opóźnienie jest zbyt duże, kolejna logika może otrzymać dane zbyt późno, co powoduje błędy.

- Pomiar:Mierzone od punktu napięcia 50% przejścia wejściowego do punktu napięcia 50% przejścia wyjściowego.

2. Czas ustalania (tsu)

Czas ustalania to minimalny czas, przez który sygnały danych muszą być stabilneprzedprzyjście krawędzi zegara.

- Scenariusz:Jeśli przerzutnik wymaga, by dane były gotowe 5 nanosekund przed wyzwoleniem zegara, to jest czas ustalania.

- Naruszenie:Jeśli dane zmieniają się zbyt blisko krawędzi zegara, system nie może poprawnie zarejestrować wartości.

3. Czas utrzymania (th)

Czas utrzymania to minimalny czas, przez który sygnały danych muszą pozostawać stabilnepoprzyjście krawędzi zegara.

- Scenariusz:Pamięć typu flip-flop musi „widzieć” dane przez krótki okres po wyzwoleniu, aby bezpiecznie je zatrzymać.

- Naruszenie:Jeśli dane zmieniają się natychmiast po krawędzi zegara, wejście może nie zostać poprawnie zatrzymane.

4. Zniekształcenie zegara (clock skew)

Zniekształcenie zegara występuje, gdy sygnał zegara przychodzi do różnych komponentów w różnych momentach. Jest to często spowodowane różnicami długości ścieżek na płytkach drukowanych.

- Zniekształcenie dodatnie:Zegar przychodzi później w miejscu docelowym.

- Zniekształcenie ujemne:Zegar przychodzi wcześniej w miejscu docelowym.

5. Jitter

Jitter to krótkoterminowa zmienność istotnych chwil sygnału względem ich idealnych pozycji w czasie. Dodaje niepewność analizie czasowej.

📊 Porównanie: Projektowanie synchroniczne vs. asynchroniczne

Zrozumienie różnicy między tymi dwoma filozofiami projektowania jest kluczowe do poprawnego interpretowania diagramów czasowych.

| Cecha | Czasowanie synchroniczne | Czasowanie asynchroniczne |

|---|---|---|

| Sygnał sterujący | Wykorzystuje globalny zegar | Wykorzystuje sygnały wymiany zdań (handshaking) |

| Przewidywalność | Wysoko przewidywalne | Zmienne w zależności od obciążenia |

| Złożoność | Wymaga dystrybucji zegara | Wymaga skomplikowanej logiki wymiany zdań |

| Zużycie mocy | Może być wysokie (przełączanie zegara) | Często niższe (zależne od aktywności) |

| Diagram czasowy | Wyrównane do krawędzi zegara | Zależne od zakończenia poprzedniego stanu |

🧐 Jak odczytywać i analizować diagramy czasowe

Analiza przebiegu wymaga systematycznego podejścia. Postępuj zgodnie z poniższymi krokami, aby upewnić się, że nie przeoczyłeś istotnych szczegółów.

Krok 1: Zidentyfikuj zegar

Znajdź główny sygnał zegarowy. Jest to zazwyczaj odniesienie dla wszystkich innych czasów. W systemach synchronicznych każda zmiana danych powinna być idealnie odniesiona do tej krawędzi zegara.

Krok 2: Sprawdź obecność zakłóceń

Szukaj krótkich, niechcianych impulsów (zakłóceń) na liniach sygnałów. Mogą one powodować fałszywe aktywacje w bramkach logicznych. W czystym diagramie przejścia powinny być czyste, choć w praktyce zapis często pokazuje szum.

Krok 3: Zweryfikuj okna ustawienia i utrzymania

Narysuj wyimaginowane pionowe linie reprezentujące okna ustawienia i utrzymania wokół aktywnej krawędzi zegara. Upewnij się, że sygnał danych jest stabilny w tych obszarach.

Krok 4: Sprawdź sygnały sterujące

Upewnij się, że sygnały sterujące, takie jak Chip Select (CS) lub Enable (EN), są aktywne przez cały czas przesyłania danych. Jeśli sygnał sterujący spadnie, gdy dane wciąż są przesyłane, nastąpi uszkodzenie danych.

Krok 5: Pomiar odstępów czasowych

Oblicz czas między określonymi zdarzeniami. Na przykład zmierz opóźnienie od sygnału „Zażądanie” do sygnału „Odpowiedź”. Pomaga to zweryfikować wydajność w stosunku do specyfikacji.

🚀 Zaawansowane koncepcje analizy czasowej

Wraz z rosnącą szybkością i złożonością systemów, podstawowe diagramy czasowe ewoluują w skomplikowane wymagania analizy.

1. Metastabilność

Metastabilność występuje, gdy przerzutnik otrzymuje wejście naruszające wymagania czasu ustawienia lub utrzymania. Zamiast przejść do jasnego stanu 0 lub 1, wyjście wchodzi w stan nieokreślony na nieprzewidywalny czas.

- Przyczyna:Często występuje, gdy sygnały asynchroniczne przekraczają granice domen zegarowych.

- Zmniejszenie ryzyka:Użyj łańcuchów synchronizujących (wiele przerzutników połączonych szeregowo), aby zmniejszyć prawdopodobieństwo wystąpienia metastabilności.

- Wizualnie:Na diagramie czasowym wygląda to jak oscylacja sygnału lub bardzo długi czas ustalania się.

2. Budżety czasu ustawienia i utrzymania

Inżynierowie obliczają budżet czasowy, aby upewnić się, że system działa z maksymalną częstotliwością. Obejmuje to odjęcie wszystkich opóźnień (przewody, bramki, przesunięcie zegara) od okresu zegara.

Jeśli całkowita opóźnienie przekracza dostępny czas, maksymalna częstotliwość pracy musi zostać zmniejszona.

3. Czasowanie interfejsu wysokiej prędkości

Interfejsy takie jak pamięć DDR lub PCIe wymagają bardzo dokładnego czasowania. Te schematy często zawierają:

- Wykresy oka: Nakładanie wielu przejść sygnału w celu wizualizacji jakości sygnału.

- Zniekształcenie cyklu roboczego:Zapewnienie zrównoważonego czasu wysokiego i niskiego.

- Wyrównanie fazowe:Zapewnienie, że dane i sygnał zegarowy przychodzą w synchronizacji przez wiele bitów.

4. Stany zarządzania energią

Nowoczesne urządzenia wchodzą w tryby niskiego zużycia energii. Schematy czasowe muszą uwzględniać opóźnienie wzbudzenia. Na przykład sygnał włączający zasilanie dla urządzenia peripheralnego musi nastąpić przed tym, gdy urządzenie będzie gotowe do odbioru danych.

📝 Najlepsze praktyki dokumentacji

Jasna dokumentacja zapobiega błędom podczas tworzenia i debugowania. Przestrzegaj tych standardów podczas tworzenia lub przeglądania schematów czasowych.

- Zgodne skalowanie:Używaj zgodnych skal czasowych w powiązanych schematach, aby ułatwić ich porównanie.

- Jasne etykiety: Każdy sygnał musi być oznaczony jego funkcją i polaryzacją logiczną (np.

RESET#dla aktywnej niskiej). - Poziomy powiększenia: Zapewnij zarówno przegląd ogólny, jak i powiększony widok krytycznych przejść (np. okien ustawienia/utrzymania).

- Kodowanie kolorów: Używaj kolorów do odróżnienia różnych domen napięcia lub źródeł zegarów (np. czerwony dla zegara, niebieski dla danych).

- Kontrola wersji: Wymagania czasowe się zmieniają. Upewnij się, że schematy są wersjonowane, aby odpowiadały wersji sprzętu.

🛠️ Powszechne pułapki i rozwiązywanie problemów

Nawet doświadczeni inżynierowie napotykają problemy z czasowaniem. Oto typowe sytuacje i sposób ich rozwiązywania.

Pułapka 1: Ignorowanie opóźnienia ścieżki

Ścieżki na płytkach PCB mają długość fizyczną, co wprowadza opóźnienie. Na wysokich częstotliwościach kilka cali przewodu może odpowiadać jednemu cyklowi zegara.

- Rozwiązanie: Zwróć uwagę na długość ścieżki podczas obliczania budżetu czasowego.

Wada 2: Niepołączone wejścia

Niepołączone wejścia mogą się „płynąć” do napięcia pośredniego, powodując drgania.

- Rozwiązanie: Upewnij się, że wszystkie wejścia mają zdefiniowane rezystory podciągające lub podciągające do masy.

Wada 3: Warunki wyścigu

Gdy dwa sygnały zmieniają się jednocześnie, kolejność ich przybycia decyduje o wyniku.

- Rozwiązanie: Użyj logiki synchronizacji lub maszyn stanów do sekwencjonowania zdarzeń.

Wada 4: Przepięcie i podnapięcie

Odbicia sygnałów mogą powodować przekroczenie napięć poziomu zasilania (przepięcie) lub spadnięcie poniżej ziemi (podnapięcie).

- Rozwiązanie: Zaimplementuj odpowiednie rezystory końcowe oraz dopasowanie impedancji.

🔗 Zastosowania w świecie rzeczywistym

Diagramy czasowe są stosowane w różnych dziedzinach inżynierii.

1. Interfejsy pamięci

DRAM i SDRAM wymagają ściśle ustalonych sekwencji czasowych dla operacji odczytu/zapisu. Opóźnienie CAS oraz opóźnienie RAS do CAS to kluczowe parametry wizualizowane na tych diagramach.

2. Komunikacja mikrokontrolerów

Protokoły takie jak I2C, SPI i UART opierają się na określonych relacjach czasowych między linią zegara a linią danych. Na przykład w I2C linia danych musi być stabilna, gdy zegar jest wysoki.

3. Sekwencjonowanie zasilania

Złożone układy wymagają, aby zasilanie włączało się w określonej kolejności. Diagramy czasowe zapewniają, że napięcie jądra jest stabilne przed podaniem napięcia I/O.

🎯 Podsumowanie najważniejszych wniosków

Opanowanie diagramów czasowych wymaga cierpliwości i dokładności. Poniższe punkty podsumowują niezbędną wiedzę do skutecznego projektowania i analizy.

- Czas ma kluczowe znaczenie:Logika cyfrowa opiera się na dokładnych relacjach czasowych między sygnałami.

- Ustawienie i utrzymanie: Są to dwa najbardziej typowe ograniczenia wpływające na maksymalną szybkość pracy.

- Weryfikacja wizualna:Diagramy pozwalają zauważyć potencjalne konflikty jeszcze przed zbudowaniem sprzętu.

- Kontekst ma znaczenie: Zawsze bierz pod uwagę środowisko fizyczne (płytkę PCB, temperaturę, napięcie), które wpływa na czas przesunięcia sygnału.

- Standardyzacja: Używaj standardowych symboli i oznaczeń, aby zapewnić jasność komunikacji między zespołami.

Stosując te zasady, zapewnicasz, że Twoje układy cyfrowe są wytrzymałe, niezawodne i wydajne. Umiejętność interpretowania i tworzenia tych schematów to podstawowa umiejętność, która rozdziela działające projekty od tych, które zawodzą w polu.

📈 Postępowanie dalej

Wraz z postępem technologii ograniczenia czasowe stają się bardziej surowe. Nowoczesne układy działają z prędkościami w gigahercach, gdzie nanosekundy mają ogromne znaczenie. Inżynierowie pracujący nad nowoczesnymi układami muszą ciągle uczyć się o integralności sygnału i zamykaniu czasu.

Zacznij od analizy istniejących schematów i odpowiadających im diagramów czasowych. Ćwicz pomiar odstępów czasowych i identyfikację naruszeń. Z czasem wzory stanie się intuicyjne, umożliwiając Ci przewidywanie problemów przed ich fizycznym wystąpieniem.