Diagramy czasowe są fundamentem weryfikacji systemów cyfrowych. Przekształcają abstrakcyjną logikę w wizualne linie czasu, na których opierają się inżynierowie, projektanci i testowcy, aby zweryfikować zachowanie sygnałów. Gdy diagram czasowy zawiera błędy, skutki sięgają daleko poza rysunkiem. Niepoprawne założenia dotyczące czasu mogą prowadzić do awarii sprzętu, uszkodzenia danych lub niestabilności systemu w środowiskach produkcyjnych. Niniejszy przewodnik analizuje najczęściej spotykane pułapki w analizie czasowej i przedstawia konkretne strategie zapewniające dokładność.

Tworzenie dokładnego diagramu czasowego wymaga więcej niż tylko rysowania linii. Wymaga głębokiego zrozumienia domen zegarowych, propagacji sygnałów oraz ograniczeń fizycznych. Inżynierowie często pośpieszają się w fazie wizualizacji, pomijając subtelne detale, które stają się kluczowe podczas implementacji. Uznając te typowe błędy wczesnym etapie, zespoły mogą zaoszczędzić znaczną ilość czasu w fazach debugowania i integracji. Przyjrzyjmy się konkretnym obszarom, w których błędy najczęściej się pojawiają.

1. Nieprawidłowe rozumienie naruszeń czasu ustawienia i czasu utrzymania ⚠️

Czas ustawienia i czas utrzymania to podstawowe ograniczenia w projektowaniu cyfrowym synchronicznym. Naruszenie czasu ustawienia występuje, gdy dane przychodzą zbyt późno przed aktywnym zboczem zegara. Naruszenie czasu utrzymania ma miejsce, gdy dane zmieniają się zbyt wcześnie po zboczu zegara. To nie są tylko pojęcia teoretyczne – odzwierciedlają fizyczne limity przerzutników i bramek logicznych.

Wiele diagramów nie wskazuje jasno okna ważności sygnałów danych. Podczas rysowania tych sygnałów inżynierowie czasem pomijają krytyczne okna ustawienia i utrzymania, co prowadzi do niejasności podczas przeglądu. Dobre diagramy powinny jasno oznaczać te okna względem zbocza zegara.

- Typowy błąd: Rysowanie przejść danych ustawionych dokładnie na zboczu zegara bez uwzględnienia drgań (jitter) lub przesunięcia zegara (skew).

- Typowy błąd: Pomijanie kierunku zbocza (narastające vs. spadające) dla okien ustawienia/utrzymania.

- Typowy błąd: Zakładanie idealnych zboczy zegara o zerzym czasie przejścia.

Aby uniknąć tych problemów, zawsze oznacz marginesy ustawienia i utrzymania. Używaj odrębnych zacieniowań lub znaczników, aby wykazać zakazane strefy, w których przejścia danych są nieprawidłowe. Ten wizualny sygnał zmusza przeglądarków do sprawdzenia, czy ścieżka sygnału spełnia wymagania czasowe logiki odbiorczej.

2. Pomijanie przesunięcia zegara (skew) i drgań (jitter) 🌪️

Przesunięcie zegara (skew) odnosi się do różnicy czasów przybycia sygnału zegarowego do różnych komponentów. Drgania (jitter) reprezentują krótkoterminowe zmiany w czasie sygnału zegarowego. Oba te czynniki mogą znacznie zmienić skuteczne okna czasowe dla sygnałów danych.

Typowym błędem w diagramach jest traktowanie zegara jako idealnie pionowej linii przechodzącej przez wszystkie komponenty. W rzeczywistości sieci dystrybucji wprowadzają opóźnienia. Jeśli diagram pokazuje jedną linię zegara rozchodzącą się do trzech różnych rejestrów bez uwzględnienia różnic w ścieżkach, przedstawia on nierealistyczny obraz zachowania systemu.

- Skutki: Przesunięcie zegara może zmniejszyć czas dostępny na propagację danych, powodując fałszywe naruszenia czasu ustawienia.

- Skutki: Drgania mogą zmniejszyć margines czasu utrzymania, zwiększając ryzyko metastabilności.

Podczas tworzenia diagramów przedstawiaj ścieżki zegara jako osobne linie z względnymi przesunięciami, jeśli przesunięcie jest istotne. Jeśli przesunięcie jest zaniedbywalne, jasno zaznacz to założenie w notatkach do diagramu. Nie ukrywaj złożoności dystrybucji zegara, jeśli wpływa ona na budżet czasowy.

3. Niespójne skale czasu i jednostki 📏

Jednym z najprostszych, a jednocześnie najbardziej szkodliwych błędów jest mieszanie skal czasu w jednym diagramie. Jeden fragment może pokazywać nanosekundy, a inny mikrosekundy. Ta niespójność zmusza czytelnika do ciągłego przeliczania stosunków, zwiększając ryzyko nieprawidłowego rozumienia.

Innym problemem jest brak jasnej osi czasu. Bez paski skali lub oznaczonych podziałek długość impulsów staje się subiektywna. Krótki impuls może wynosić 10 nanosekund lub 100 nanosekund w zależności od tego, jak czytelnik rozumie odległość między liniami.

Przestrzegaj tych standardów, aby zachować spójność:

- Zdefiniuj skalę: Umieść linijkę czasu na dole lub górze diagramu.

- Używaj notacji naukowej:Jasno oznacz jednostki (ns, μs, ps) w nagłówku.

- Utrzymuj proporcje: Upewnij się, że odległość pozioma między zdarzeniami odpowiada różnicy czasowej.

Spójność buduje zaufanie. Gdy każdy inżynier spojrzy na schemat, powinien otrzymać te same wartości czasowe, nie musząc robić założeń dotyczących skali rysunku.

4. Niejasność w wyzwalaczu krawędzi 🔄

Logika cyfrowa często opiera się na określonych wyzwalaczach krawędzi, takich jak krawędź narastająca lub spadająca. Schemat czasowy musi jasno pokazywać, która krawędź wywołuje działanie. Niejasność w tym miejscu może prowadzić do zupełnie przeciwnego zachowania w sprzęcie.

Powszechnym błędem jest rysowanie sygnału zegara bez wskazania krawędzi aktywnej. Na przykład, jeśli przerzutnik wyzwalany jest krawędzią spadającą, ale schemat wygląda identycznie jak wyzwalacz krawędzią narastającą, projektant logiki może zaimplementować błędne zachowanie.

- Najlepsza praktyka: Używaj strzałek na linii zegara, aby wskazać krawędź aktywną.

- Najlepsza praktyka: Oznacz typ wyzwalacza w legendzie (np. „Posedge”, „Nedge”).

- Najlepsza praktyka: Unikaj używania podwójnych strzałek, chyba że aktywne są obie krawędzie.

Jasność jest najważniejsza. Jeśli sygnał jest asynchroniczny, upewnij się, że jest jasno oddzielony od domeny zegara, aby uniknąć nieporozumień co do tego, która krawędź go kontroluje.

5. Pomijanie opóźnień propagacji ⏳

Opóźnienie propagacji to czas potrzebny sygnałowi na przejście od wejścia do wyjścia przez bramkę logiczną lub przewód. W idealnych schematach sygnały wydają się zmieniać natychmiast. W systemach fizycznych zawsze występuje opóźnienie.

Gdy projektanci pomijają opóźnienia propagacji, schemat czasowy sugeruje, że wyjście zmienia się natychmiast po zmianie wejścia. Może to ukrywać naruszenia czasowe, które wystąpią w układzie scalonym. Na przykład, ścieżka kombinacyjna może wydawać się spełniać okres zegara na schemacie, ale rzeczywiste opóźnienie przesuwa dane poza następny brzeg zegara.

| Cecha | Idealny schemat | Wdrożenie w świecie rzeczywistym |

|---|---|---|

| Przejście sygnału | Linia pionowa | Linia nachylona z opóźnieniem |

| Propagacja | Natychmiastowe | Opóźnienie bramki + opóźnienie przewodu |

| Zapasa ustawienia | Często nie sprawdzane | Należy uwzględnić najgorszy przypadek |

Aby ograniczyć ten problem, oznacz oczekiwane opóźnienie dla kluczowych ścieżek. Jeśli opóźnienie jest istotne w stosunku do okresu zegara, narysuj przejście z nachyleniem lub jasno zaznacz wartość opóźnienia. Ta reprezentacja wizualna pomaga recenzentom wykryć potencjalne przewężenia przed produkcją.

6. Pomijanie ryzyka metastabilności 🌌

Metastabilność występuje, gdy przerzutnik otrzymuje dane w pobliżu brzegu zegara, powodując wejście w stan nieokreślony na nieprzewidywalny czas. Schematy czasowe rzadko jasno przedstawiają ten stan, ponieważ jest to tryb awaryjny, a nie normalne działanie.

Jednak ignorowanie możliwości metastabilności w interfejsach asynchronicznych to poważna pomyłka. Jeśli schemat pokazuje sygnał asynchroniczny synchronizujący się z zegarem bez łańcucha synchronizatorów, oznacza to ryzyko utraty danych lub ich uszkodzenia.

- Identyfikacja: Szukaj sygnałów przekraczających domeny zegarowe bez odpowiedniej synchronizacji.

- Dokumentacja: Zaznacz, gdzie metastabilność stanowi znane ryzyko i jak jest ograniczana.

- Wizualizacja: Używaj linii przerywanych, aby oznaczać granice asynchroniczne.

Nawet jeśli system został zaprojektowany tak, aby radzić sobie z metastabilnością, schemat powinien odzwierciedlać etapy synchronizacji. Zapewnia to, że zespół weryfikacyjny wie, że należy testować te konkretne warunki.

7. Zmiany sygnałów i zagrożenia ⚡

Zmiany sygnałów to przejściowe impulsy powstające z powodu nierównych opóźnień propagacji w równoległych ścieżkach. Mogą powodować fałszywe uruchamianie logiki, jeśli nie zostaną uwzględnione w analizie czasowej.

Powszechnym błędem jest rysowanie czystych, stałych sygnałów w miejscach, gdzie zmiany sygnałów są fizycznie nieuniknione. Na przykład w przełączniku wielokrotnym zmieniającym wejścia, wyjście może chwilowo migać przed ustabilizowaniem się. Jeśli schemat pokazuje gładką zmianę, logika w kolejnym etapie może nie być zaprojektowana do filtrowania tych zmian.

Wyróżnij potencjalne strefy zagrożeń na schemacie. Użyj adnotacji, aby ostrzec, że dany sygnał może wykazywać zachowanie przejściowe podczas zmian stanów. To informuje strategię testowania o uwzględnienie scenariuszy wykrywania zmian sygnałów.

8. Brak kontekstu dla sygnałów sterujących 🔌

Sygnały danych są bezużyteczne bez kontekstu sygnałów sterujących, takich jak włączanie, resetowanie lub wybór mikrochipu. Schemat skupiający się wyłącznie na liniach danych często pomija warunki wymagane do poprawności danych.

Na przykład magistrala danych może pokazywać poprawne wartości, ale jeśli sygnał „Włącz zapis” nie jest pokazany jako aktywny w tym oknie, dane są efektywnie ignorowane. Z kolei, jeśli sygnał „Włącz zapis” jest aktywny, ale dane są niepoprawne, system zapisuje śmieci.

- Zawartość sterowania: Zawsze wyświetlaj sygnały sterujące razem z sygnałami danych.

- Zdefiniuj poprawność: Użyj flagi „Dane poprawne” lub podobnego oznaczenia, aby wskazać, kiedy dane są wiarygodne.

- Warunki stanu: Jasną etykietą oznacz stan sygnałów sterujących (aktywne wysokie vs. aktywne niskie).

Pełność jest kluczowa. Schemat czasowy bez kontekstu sygnałów sterujących często jest źródłem zamieszania podczas debugowania. Upewnij się, że relacja między sygnałami sterującymi a danymi jest wizualnie jasna.

9. Zła obsługa adnotacji i legendy 📝

Nawet doskonale dokładny schemat może zostać źle zrozumiany, jeśli nie ma odpowiednich adnotacji. Symbole, skróty i legenda muszą być spójne i wyjaśnione.

Powszechne błędy w adnotacjach to:

- Używanie ogólnych etykiet, takich jak „Sygnał A”, zamiast opisowych nazw.

- Nie wyjaśnianie znaczenia konkretnych stylów linii (ciągła vs. przerywana).

- Pomijanie definicji poziomu aktywnego (aktywne wysokie vs. aktywne niskie).

Specjalna sekcja legendy powinna być częścią każdego schematu czasowego. Definiuje każdy symbol, styl linii i skrót używany. Zmniejsza obciążenie poznawcze czytelnika i zapewnia, że wszyscy rozumieją schemat w ten sam sposób.

10. Lista kontrolna weryfikacji i przeglądu ✅

Zanim zakończyć rysowanie diagramu czasowego, konieczna jest systematyczna kontrola. Użyj poniższej listy kontrolnej, aby zweryfikować poprawność i czytelność swojej pracy.

| Element sprawdzania | Kryteria zaliczenia |

|---|---|

| Skala czasu | Zgodne jednostki i jasny miarodajny odcinek podany |

| Krawędź zegara | Aktywna krawędź jasno oznaczona dla wszystkich zegarów |

| Zapobieganie/utrzymanie | Okna zdefiniowane dla sygnałów synchronicznych |

| Rozprzestrzenianie | Opóźnienia uwzględnione w krytycznych ścieżkach |

| Sygnały sterujące | Sygnały włączania/resetowania pokazane razem z danymi |

| Legenda | Wszystkie symbole i skróty wyjaśnione |

| Przekroczenie domeny | Punkty CDC zidentyfikowane i oznaczone |

Regularne aktualizowanie tej listy kontrolnej zapewnia, że żaden typowy błąd nie przejdzie niezauważony. Służy jako bariera jakości dla dokumentacji przed jej przekazaniem zespołowi inżynierskiemu.

11. Wyraźność wizualna i projekt układu 🎨

Układ diagramu czasowego wpływa na łatwość wykrywania błędów. Zatłoczone diagramy z nakładającymi się sygnałami są podatne na nieprawidłowe odczytanie. Pionowa wyrownanie powiązanych sygnałów pomaga oczom śledzić relacje między zdarzeniami.

Postępuj zgodnie z tymi zasadami układu:

- Grupuj sygnały: Przechowuj powiązane sygnały (takie jak adres i dane) blisko siebie.

- Wyrównaj krawędzie: Upewnij się, że krawędzie zegarów są wyrównane pionowo we wszystkich kanałach.

- Rozdziel: Pozostaw wystarczająco dużo białego miejsca, aby uniknąć nakładania się sygnałów.

- Kodowanie kolorów: Używaj różnych kolorów dla różnych domen zegarów, jeśli jest to możliwe (choć dla druku standardem jest czarno-biały kolor).

Czysty układ zmniejsza wysiłek poznawczy wymagany do zrozumienia diagramu. Ułatwia to szybkie wykrywanie anomalii i naruszeń czasowych.

12. Ograniczenia z rzeczywistego świata w porównaniu z symulacją 🖥️

Diagramy czasowe pochodzące wyłącznie z symulacji mogą nie odzwierciedlać rzeczywistości fizycznej. Narzędzia symulacyjne często zakładają idealne warunki, takie jak zerowa pojemność parazytowa i doskonała trasa sygnału.

Przy przekształcaniu wyników symulacji na dokumentację inżynierowie muszą uwzględnić zmienność produkcji. Kąty procesu, napięcia i temperatury (PVT) mogą przesunąć marginesy czasowe. Diagram pokazujący tylko wartości nominalne może być niewystarczający dla projektu odpornego.

- Najgorszy przypadek:Zważ na najwolniejszy kąt procesu podczas analizy czasowej.

- Najlepszy przypadek:Zważ na najszybszy kąt procesu podczas analizy czasu utrzymania.

- Margines:Dodaj marginesy bezpieczeństwa do diagramu, aby uwzględnić zmienność PVT.

Dokumentacja powinna odzwierciedlać odporność projektu, a nie tylko najlepsze wyniki symulacji. Przygotowuje zespół do rzeczywistych scenariuszy wdrożenia.

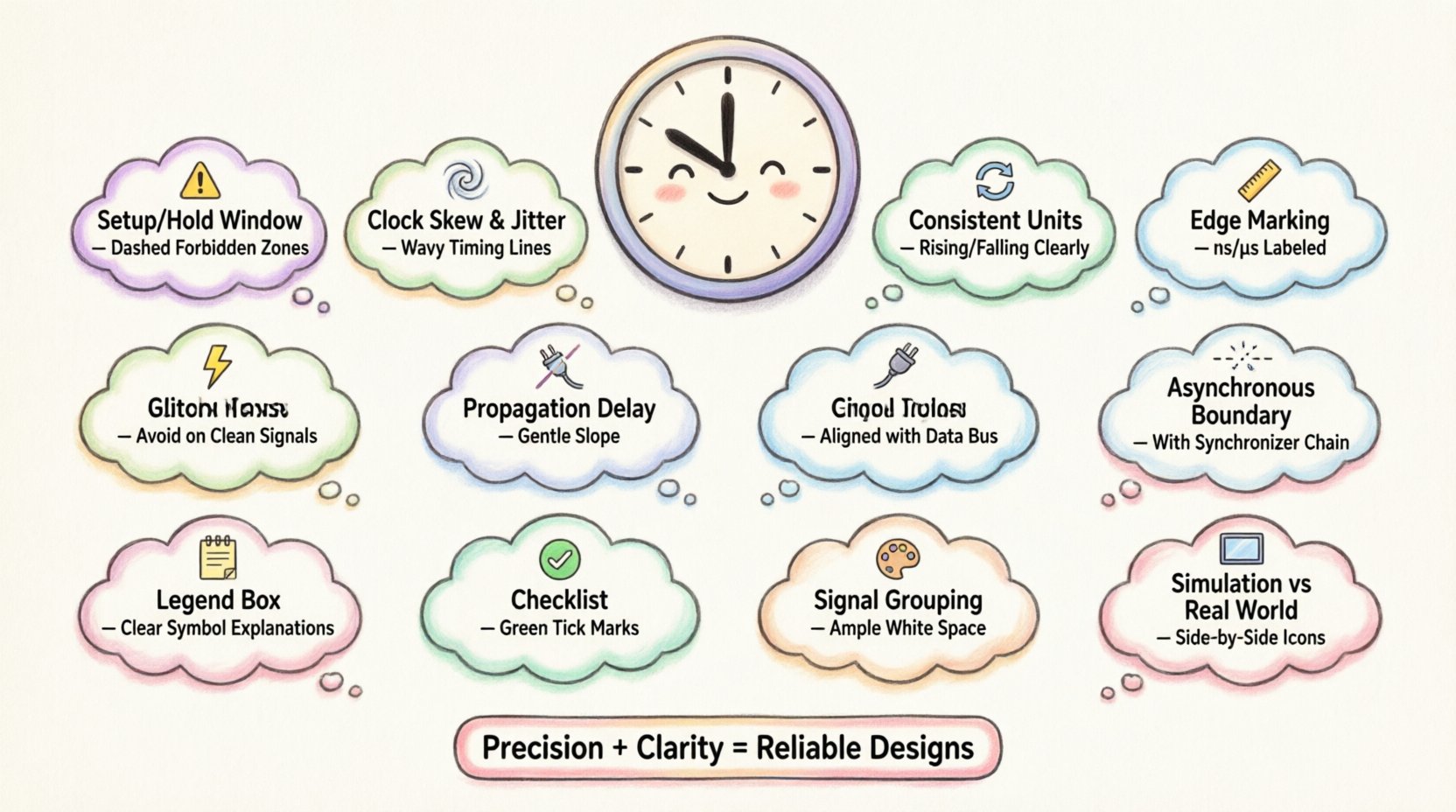

Ostateczne rozważania dotyczące dokładności czasowej 🛡️

Diagramy czasowe są narzędziem komunikacji tak samo jak specyfikacją techniczną. Ich głównym celem jest jasne przekazanie intencji i ograniczeń wszystkim zaangażowanym. Unikając typowych błędów, takich jak pomijanie zniekształceń, ignorowanie przejść sygnałów lub pomijanie sygnałów sterujących, inżynierowie zapewniają, że intencja projektu zostanie zachowana od dokumentacji po sprzęt.

Dokładność w tych diagramach zapobiega kosztownym ponownym uruchomieniom i cyklom debugowania. Dobrze skonstruowany diagram stanowi jednoznaczną źródło prawdy na całym cyklu życia projektu. Inwestuj czas, aby poprawnie przeprowadzić analizę czasową, a implementacja w kolejnych etapach przebiegnie płynnie.

Pamiętaj, że diagram czasowy to dokument żywy. Powinien być aktualizowany za każdym razem, gdy zmienia się projekt. Zachowanie integralności informacji czasowych zapewnia, że system pozostanie niezawodny przez cały okres swojego użytkowania. Skup się na precyzji, jasności i kompletności, aby zapewnić odporność projektów cyfrowych.