Diagramy czasowe są fundamentem projektowania systemów cyfrowych. Są one wizualnym kontraktem między logiką, sprzętem a oprogramowaniem, definiującym dokładnie, kiedy sygnały powinny zmieniać stan. Jednak pomimo ich powszechności w inżynierii, istnieje trwała mgła nieporozumień dotycząca sposobu tworzenia, interpretowania i wykorzystywania tych diagramów. Wiele specjalistów traktuje je jako statyczne ilustracje, a nie dynamiczne przedstawienia zachowania systemu.

Ten przewodnik ma na celu rozproszenie mgły. Przeanalizujemy powszechne błędy, zbadamy rzeczywistości propagacji sygnałów i stworzymy ramy do tworzenia dokładnej dokumentacji czasowej. Oddzielając fakt od fikcji, inżynierowie mogą skrócić czas debugowania i poprawić niezawodność systemu.

Czym jest diagram czasowy? 🤔

Diagram czasowy to graficzne przedstawienie zachowania sygnałów w obwodzie cyfrowym w czasie. W przeciwieństwie do schematu, który pokazuje połączenia, diagram czasowy przedstawia przyczynowość i relacje czasowe. Rysuje poziomy sygnałów (wysoki, niski lub niezdefiniowany) względem osi czasu, pozwalając projektantom zweryfikować, czy dane są stabilne w odpowiednim momencie.

Kluczowe cechy obejmują:

- Oś czasu: Zazwyczaj biegnie poziomo, reprezentując postęp zdarzeń.

- Linie sygnałów: Pionowe linie reprezentujące konkretne przewody, magistrale lub stany logiczne.

- Krawędzie: Przejścia od niskiego do wysokiego (narastające) lub od wysokiego do niskiego (spadające).

- Etykiety: Adnotacje wskazujące czasy ustawienia, czasy utrzymania lub opóźnienia.

Bez jasnego zrozumienia tych elementów diagram staje się źródłem zamieszania, a nie jasności.

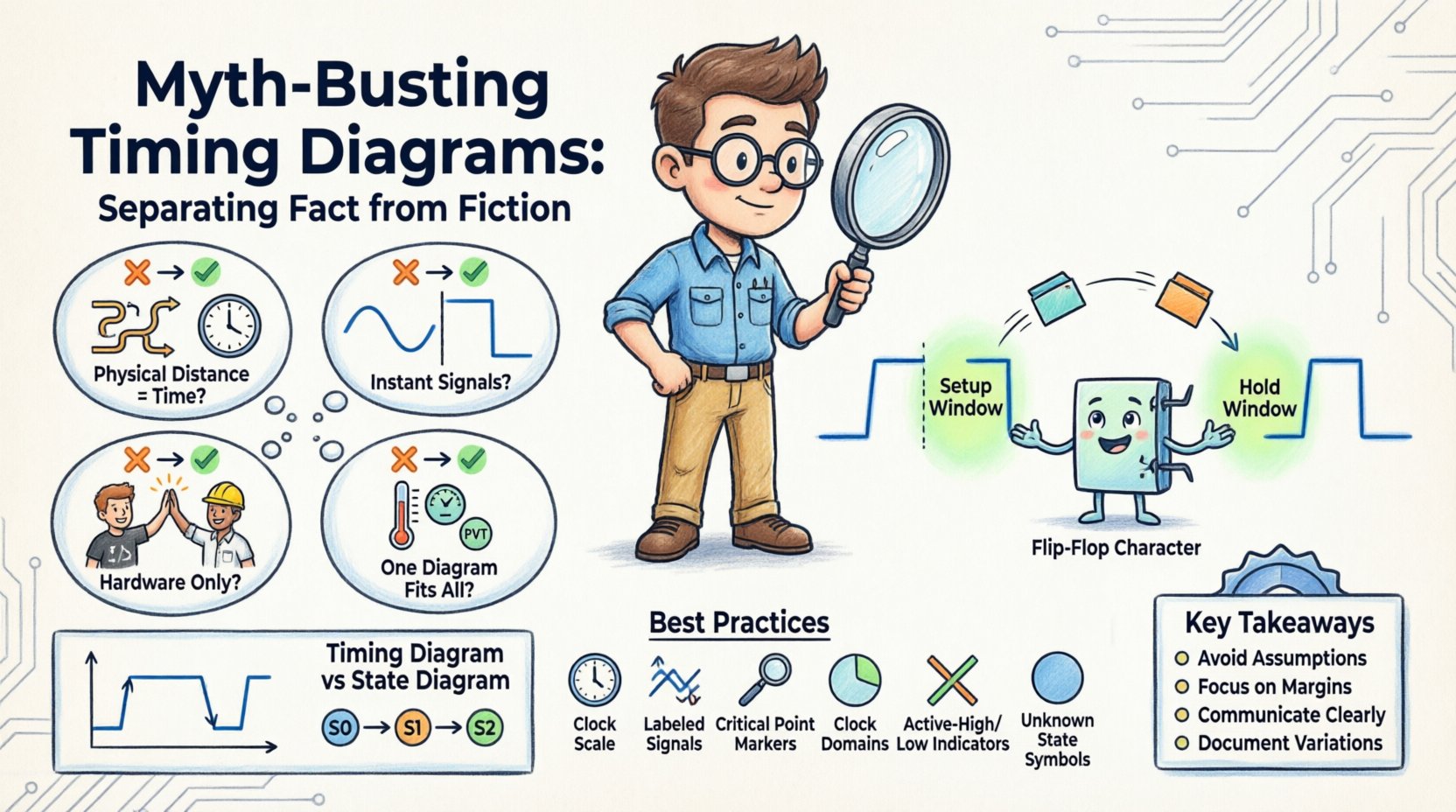

Powszechne mity dotyczące diagramów czasowych 🚫

Aby poprawić jakość projektu, najpierw musimy zidentyfikować fałszywe przekonania, które prowadzą do błędów. Poniżej znajdują się najpowszechniejsze mitu krążące w środowiskach technicznych.

Mity 1: Diagramy czasowe pokazują dokładną odległość fizyczną 📏

Fikcja: Inżynierowie często zakładają, że pozioma odległość między dwoma krawędziami na diagramie bezpośrednio odpowiada długości fizycznej ścieżki na płycie PCB.

Prawda:Diagramy czasowe przedstawiają czas logiczny lub elektryczny, a nie przestrzeń fizyczną. Choć długość ścieżki wpływa na opóźnienie propagacji, diagram skupia się na wyniku tego opóźnienia, a nie samej geometrii. Opóźnienie 1 nanosekundowe może odpowiadać ścieżce o długości 15 cm na płycie FR4 lub ścieżce o długości 10 cm na miedzianej ścieżce z innymi stałymi dielektrycznymi. Diagram abstrahuje medium fizyczne, skupiając się na oknie czasowym.

- Długość fizyczna decyduje o opóźnieniu, ale diagram pokazuje wartość opóźnienia.

- Złożoność trasy jest ukryta; istotny jest tylko końcowy wynik.

- Zakładanie skali 1:1 między czasem a odległością prowadzi do błędów w układzie.

Mity 2: Przejścia sygnałów są natychmiastowe ⚡

Fikcja:W wielu diagramach pionowe linie wskazują na natychmiastowe zmiany stanu sygnału.

Prawda:Żaden sygnał fizyczny nie zmienia stanu natychmiastowo. Zawsze istnieje czas narastania i czas spadku. Gdy na schemacie pokazuje się pionowy krawędź, oznacza to przejście, które jest szybkie w stosunku do okresu zegara, ale nie zerowe. Ignorowanie czasów przejścia może prowadzić do problemów z integralnością sygnału, takich jak drgania lub zakłócenia wzajemne, które nie są widoczne na uproszczonych schematach.

- Czas narastania to czas potrzebny do przejścia od 10% do 90% napięcia.

- Schematy często upraszczają to dla lepszej czytelności, ale symulacja musi to uwzględnić.

- Projekty o wysokiej prędkości wymagają jawnej modelowania nachylenia przejść.

Mity 3: Schematy czasowe są tylko dla inżynierów sprzętowych 🛠️

Fikcja:Programiści oprogramowania i architekci systemów często ignorują schematy czasowe, zakładając, że nie mają znaczenia dla logiki kodu.

Prawda:Oprogramowanie musi przestrzegać ograniczeń czasowych sprzętu. Przerwania, przesyłki DMA oraz wejście/wyjście pamięciowe zależą od czasu ustalonego przez sprzęt. Jeśli sterownik spróbuje odczytać dane przed tym, gdy sprzęt wyda sygnał „Gotowy”, wystąpi błąd szyny. Schematy czasowe są niezbędne do komunikacji między dyscyplinami.

- Przerwania oprogramowania muszą być zsynchronizowane z cyklami zegara sprzętu.

- Okna dostępu do pamięci są definiowane przez specyfikacje czasowe.

- Obie zespoły – sprzętowe i programistyczne – potrzebują wspólnej wiedzy o przebiegu czasu.

Mity 4: Jeden schemat pasuje do wszystkich kontekstów 🌍

Fikcja:Jeden schemat czasowy może opisać cały system, niezależnie od warunków pracy.

Prawda:Czas trwania zmienia się w zależności od temperatury, napięcia i zmian procesu (PVT). Schemat narysowany dla warunków nominalnych może zawieść w skrajnych przypadkach. Projektanci muszą uwzględnić najgorsze scenariusze. Schemat pokazujący zachowanie w najlepszych warunkach często jest mniej przydatny niż ten, który podkreśla granice działania.

- Opóźnienie w najgorszym przypadku decyduje o minimalnym okresie zegara.

- Temperatura wpływa na rezystancję i pojemność.

- Zmiany procesu wpływają na szybkość przełączania tranzystorów.

Głęboka analiza: Czas ustalania i czas utrzymania ⏱️

Zrozumienie naruszeń czasowych jest kluczowe. Dwa konkretne pojęcia dominują analizę integralności danych: Czas ustalania i Czas utrzymania. Są one często źródłem najtrudniejszych błędów w systemach cyfrowych.

Czas ustalania (Tsu)

Czas ustalania to minimalny czasprzedkrawędzi zegara, przez który dane muszą być stabilne. Jeśli dane zmieniają się zbyt blisko krawędzi zegara, przechwytywany rejestrujący układ może nie przechwycić poprawnej wartości.

- Zapewnia, że dane są ustalone przed zamknięciem okna przechwytywania.

- Naruszenia powodują metastabilność lub niepoprawne stany logiczne.

- Opóźnienie trasy musi być mniejsze niż okres zegara pomniejszony o czas ustawienia.

Czas utrzymania (Th)

Czas utrzymania to minimalna ilość czasupopo krawędzi zegara, przez którą dane muszą pozostać stabilne. Jeśli dane zmienią się zbyt szybko po krawędzi zegara, przerzutnik może stracić wcześniej przechwyconą wartość.

- Zapewnia, że dane pozostają stabilne wystarczająco długo, aby zostały przechwycone.

- Naruszenia są często trudniejsze do naprawienia niż naruszenia ustawienia.

- Opóźnienie trasy musi być większe niż wymagany czas utrzymania.

Sytuacje naruszeń czasowych

Podczas analizy diagramu czasowego szukaj następujących wzorców:

- Naruszenie ustawienia: Sygnał danych nadal się zmienia, gdy przychodzi krawędź zegara.

- Naruszenie utrzymania: Sygnał danych zmienia się natychmiast po krawędzi zegara.

- Zakłócenie: Krótki impuls, który występuje w oknie ustawienia/utrzymania, ale nie jest poprawną zmianą.

Diagram czasowy w porównaniu do diagramu stanów 🔄

Pomyłki często pojawiają się między diagramami czasowymi a diagramami stanów. Choć oba opisują zachowanie systemu, odpowiadają na różne pytania. Diagram stanów pokazujecoco system robi (przepływ logiczny), podczas gdy diagram czasowy pokazujekiedyto się dzieje (przepływ czasowy).

| Cecha | Diagram czasowy | Diagram stanów |

|---|---|---|

| Główny nacisk | Czas i poziomy sygnałów | Logika i przepływ sterowania |

| Reprezentacja osi | Pozioma = Czas | Pozioma = Stany logiczne |

| Najlepsze do | Integralność sygnału, synchronizacja | Projektowanie algorytmów, logika maszyny stanów |

| Złożoność | Wysoka szczegółowość czasowa | Wysoka złożoność logiczna |

| Szczegóły sygnału | Pokaż poziomy napięcia (Wysoki/Niski) | Pokaż abstrakcyjne stany (Nieaktywny/Uruchomiony) |

Używanie odpowiedniego diagramu dla zadania zapobiega nieporozumieniom. Maszynę stanów można zaprojektować bez diagramu czasowego, ale interfejs szybkiego magistrali nie może.

Najlepsze praktyki tworzenia dokładnych diagramów ✅

Aby upewnić się, że dokumentacja jest skuteczna, przestrzegaj tych wskazówek. Dokładność w dokumentacji zmniejsza niepewność podczas implementacji.

- Zdefiniuj skalę czasową: Zawsze określ jednostki (ns, µs, cykle). Jeśli używasz cykli, zdefiniuj częstotliwość zegara.

- Oznacz każdy sygnał: Nie używaj ogólnych nazw takich jak „Sygnał 1”. Używaj opisowych nazw takich jak „CLK_IN” lub „DATA_VALID”.

- Zaznacz kluczowe punkty: Wyraźnie zaznacz okna ustawienia i utrzymania za pomocą cieniowania lub adnotacji.

- Uwzględnij domeny zegarowe: Jeśli istnieje wiele zegarów, jasno je rozróżnij. Pokaż relację między asynchronicznymi zegarami, jeśli to stosowne.

- Pokaż stan aktywny wysoki/niski: Ustal, czy stan aktywny to wysoki (1) czy niski (0), aby uniknąć błędów polaryzacji.

- Zaznacz nieznane stany: Użyj X lub Z do oznaczenia niezdefiniowanych lub stanów o wysokim oporze zamiast pozostawiania ich pustych.

Obsługa sygnałów asynchronicznych 🔄

Jednym z najtrudniejszych aspektów diagramów czasowych jest obsługa sygnałów asynchronicznych. Są to sygnały niezgodne z głównym zegarem systemowym. Powodują one niepewność, którą należy zarządzać.

- Metastabilność: Gdy sygnał asynchroniczny przychodzi w pobliżu krawędzi zegara, przerzutnik może wejść w stan metastabilny. W końcu rozwiąże się na 0 lub 1, ale czas potrzebny na to jest nieprzewidywalny.

- Synchronizatory: Używaj łańcuchów przerzutników do rozwiązywania metastabilności. Diagramy czasowe powinny pokazywać, że obszar metastabilny rozwiązuje się przed następną krawędzią zegara.

- Uwierzytelnianie: Protokoły takie jak I2C lub SPI wykorzystują asynchroniczne uwierzytelnianie. Diagram czasowy musi pokazywać stany oczekiwania, w których master czeka na slave.

Zastosowanie w świecie rzeczywistym: debugowanie warunku wyścigu 🐞

Wyobraź sobie sytuację, w której magistrala danych nie jest odczytywana poprawnie. System czasem zawiesza się. Analiza diagramu czasowego ujawnia problem.

- Obserwacja: Sygnał „Gotowy” jest aktywowany nieco później niż sygnał „Odczyt”.

- Sprawdzenie diagramu: Diagram czasowy pokazuje, że krawędź sygnału „Gotowy” spada w oknie ustawienia sygnału „Odczyt”.

- Wnioski: Dane są odczytywane przed ich poprawnym stanem.

- Rozwiązanie: Dostosuj logikę, aby opóźnić sygnał „Odczyt” lub wydłużyć impuls sygnału „Gotowy”.

Ten przykład pokazuje, dlaczego wizualizacja przebiegu czasowego jest kluczowa. Bez diagramu warunek wyścigu pozostaje ukryty w logice kodu.

Narzędzia i metody analizy 🔍

Choć konkretne nazwy oprogramowania nie są głównym celem, metody analizy pozostają stałe. Nowoczesna inżynieria opiera się na symulacji i przeglądarce przebiegów, aby zweryfikować diagramy czasowe.

- Symulacja: Uruchamiaj testbenchy, aby wygenerować przebiegi odpowiadające celom projektu.

- Statyczna analiza czasowa (STA): Oblicz opóźnienia bez symulacji, aby sprawdzić naruszenia na wszystkich ścieżkach.

- Debugowanie sprzętu: Używaj oscyloskopów do zapisywania rzeczywistych przebiegów i porównywania ich z teoretycznym diagramem.

- Kontrola wersji: Przechowuj diagramy czasowe w kontrolie wersji. Zmiany w sprzęcie często wymagają aktualizacji specyfikacji czasowych.

Wpływ drgań i przesunięć czasowych 📉

Diagramy czasowe często rysuje się linią idealnie prostą. W rzeczywistości jest to bardziej chaotyczne. Drgania i przesunięcia czasowe to źródła szumu wpływające na dokładność czasową.

- Drgania: Zmiany w czasie przejść sygnału. Zjawisko jittera zegara powoduje przesunięcie okna próbkowania.

- S skew: Różnica w czasie przybycia tego samego sygnału zegarowego w różnych punktach obwodu.

- Skutki: Oba zmniejszają margines czasowy. Wykres czasowy powinien idealnie pokazywać margines, a nie tylko idealny przebieg.

Podsumowanie najważniejszych wniosków 📝

Wykresy czasowe to więcej niż tylko rysunki; są to specyfikacje zachowania. Zrozumienie mitów i faktów dotyczących ich pozwala inżynierom projektować bardziej odpornych systemów.

- Unikaj założeń: Nie zakładaj natychmiastowych przejść ani doskonałej synchronizacji.

- Skup się na marginesach: Czas ustalania i czas utrzymania to bufor bezpieczeństwa zapobiegający awarii.

- Komunikuj jasno: Używaj wykresów, aby zlikwidować różnicę między zespołami sprzętowymi a programistycznymi.

- Dokumentuj zmiany: Uznaj, że czas zmienia się wraz z środowiskiem i procesem.

Gdy patrzysz na wykres czasowy, widzisz czas. Widzisz ograniczenia. Widzisz niezawodność. Ten punkt widzenia przekształca statyczny obraz w potężne narzędzie doskonałości inżynierskiej.