W świecie elektroniki cyfrowej i inżynierii sprzętu komunikacja między elementami opiera się na dokładnej koordynacji. Bez jasnego zrozumienia, kiedy sygnały zmieniają stan, systemy zawodzą. Diagram czasowy pełni rolę projektu tego współdziałania. Wizualizuje zależności między sygnałami w czasie, ujawniając, czy dane są poprawne, stabilne i gotowe do przetwarzania. Niniejszy przewodnik odpowiada na podstawowe pytania, z jakimi mierzą się inżynierowie i studenci podczas analizy tych kluczowych narzędzi wizualnych.

Niezależnie od tego, czy projektujesz interfejs mikrokontrolera, debugujesz protokół komunikacyjny, czy studiujesz logikę cyfrową, zrozumienie aspektów czasowych Twojego projektu jest nie do odmówienia. Niniejszy artykuł bada budowę diagramów czasowych, wyjaśnia kluczowe parametry oraz odpowiada na typowe pytania dotyczące integralności sygnałów i synchronizacji.

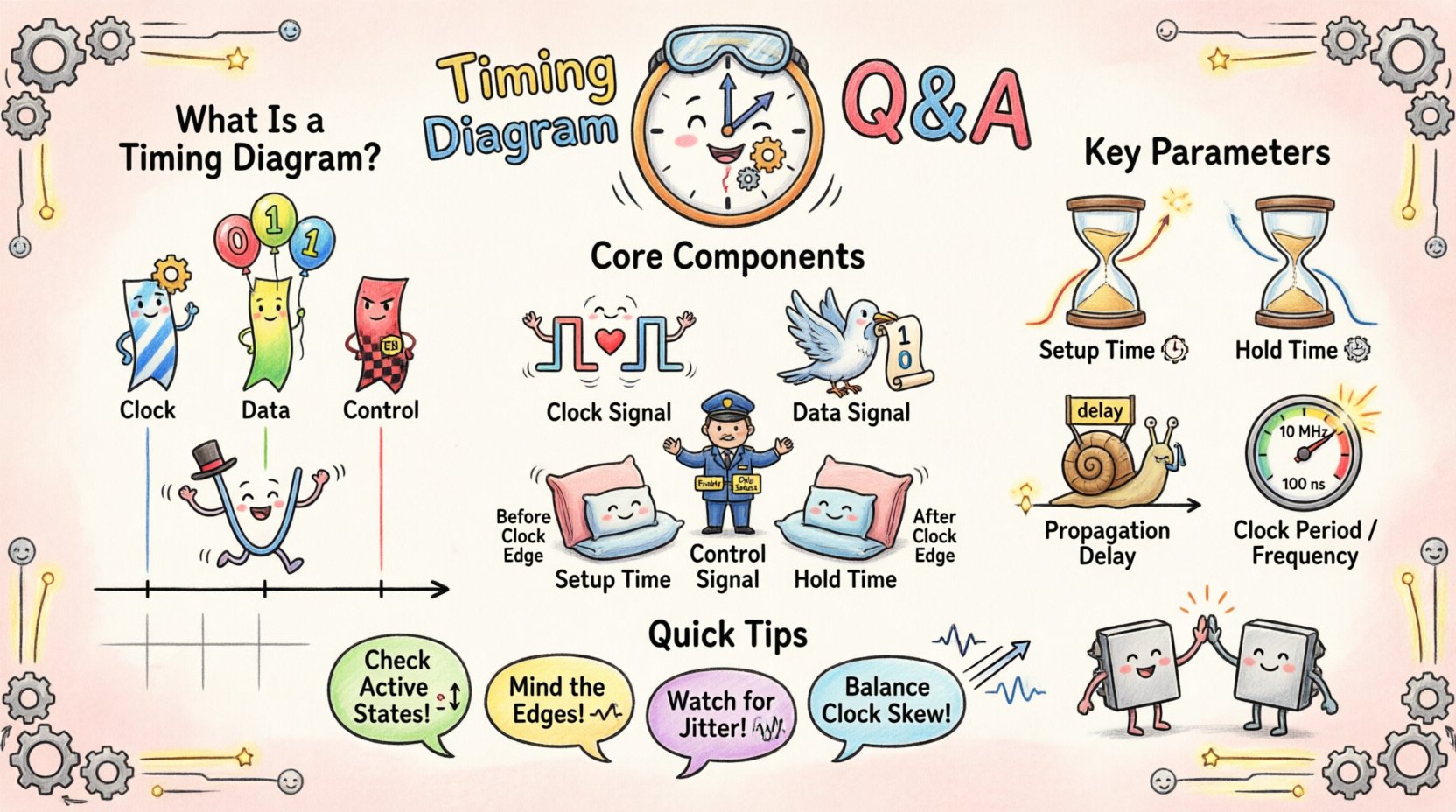

Czym dokładnie jest diagram czasowy? 📊

Diagram czasowy to graficzne przedstawienie sekwencji zdarzeń w systemie. Przedstawia poziomy sygnałów względem poziomej osi czasu. W przeciwieństwie do schematu logicznego, który pokazuje połączenia, diagram czasowy przedstawia zachowanie. Pozwala zobaczyć, czy sygnał zmienia się na wysoki lub niski przed lub po innym sygnale. To widoczne kontekst jest niezbędny do weryfikacji, czy odbiorca ma wystarczająco dużo czasu na odczyt danych przed nadchodzącym krawędzią zegara.

Kluczowe cechy obejmują:

- Oś czasu: Zazwyczaj biegnie poziomo od lewej do prawej.

- Linie sygnałów: Poziome linie reprezentujące pojedyncze przewody lub magistrale danych.

- Poziomy logiczne: Stany wysoki (1) i niski (0) są przedstawiane jako wyraźne poziomy napięcia.

- Krawędzie: Pionowe linie wskazujące przejście z jednego stanu do drugiego.

Główne elementy diagramu czasowego 🧩

Aby skutecznie odczytywać te diagramy, należy zidentyfikować standardowe elementy tworzące przebieg sygnału. Każdy z nich pełni określoną rolę w synchronizacji systemu.

| Element | Opis | Wskaźnik wizualny |

|---|---|---|

| Sygnał zegarowy | Dostarcza taktowania systemu. Inne sygnały są często próbkowane względem tego. | Regularny wzorzec fali prostokątnej |

| Sygnał danych | Przenosi rzeczywistą informację przesyłaną. | Nieregularne przejścia zależne od wejścia |

| Sygnał sterujący | Zarządza przepływem danych (np. Włącz, Wybór mikrochipu, Zapis). | Pulsy aktywne wysokie lub aktywne niskie |

| Czas ustawienia | Czas, przez który dane muszą być stabilne przed krawędzią zegara. | Odległość pozioma przed krawędzią |

| Czas utrzymania | Czas, przez który dane muszą pozostawać stabilne po krawędzi sygnału zegarowego. | Odległość pozioma po krawędzi |

Zrozumienie kluczowych parametrów czasowych ⚙️

Parametry czasowe definiują ograniczenia, w których cyfrowy układ działa poprawnie. Naruszenie tych parametrów często prowadzi do nieprzewidywalnego zachowania. Poniżej znajdują się definicje i konsekwencje najważniejszych metryk.

1. Czas ustawienia ⏳

Czas ustawienia to minimalny czas, przez który sygnał danych powinien być utrzymywany w stanie stabilnym przed krawędzią wyzwalającą sygnału zegarowego. Jeśli dane zmieniają się zbyt blisko krawędzi zegarowej, przerzutnik może nie poprawnie zarejestrować wartości. Jest to często najważniejsze ograniczenie w projektach o wysokiej prędkości, ponieważ określa maksymalną częstotliwość działania.

2. Czas utrzymania ⏳

Czas utrzymania to minimalny czas, przez który sygnał danych powinien być utrzymywany w stanie stabilnym po krawędzi wyzwalającej sygnału zegarowego. W przeciwieństwie do czasu ustawienia, czas utrzymania jest zazwyczaj niezależny od częstotliwości zegara. Zależy od opóźnienia wewnętrznych przerzutnika oraz opóźnienia propagacji sygnału w ścieżce danych.

3. Opóźnienie propagacji ⏳

Jest to czas potrzebny na przejście sygnału od wejścia komponentu do jego wyjścia. Waha się w zależności od temperatury, napięcia i tolerancji produkcyjnych. Na wykresie czasowym pojawia się jako opóźnienie między zmianą jednego sygnału a wynikającą zmianą drugiego.

4. Okres zegara i częstotliwość ⏳

Okres zegara to czas trwania jednego pełnego cyklu sygnału zegarowego. Częstotliwość to odwrotność okresu. Krótszy okres oznacza wyższą częstotliwość, co pozwala na szybsze przetwarzanie, ale zmniejsza okno stabilności sygnału.

Często zadawane pytania ❓

Inżynierowie często napotykają konkretne sytuacje, które powodują zamieszanie. Oto szczegółowe odpowiedzi na najważniejsze pytania dotyczące analizy czasowej.

Q: Co się dzieje, jeśli naruszy się czas ustawienia? 🛑

Gdy wymóg czasu ustawienia nie jest spełniony, przerzutnik wchodzi w stan znany jako metastabilność. W tym stanie wyjście nie ustala się od razu na poprawny poziom logiczny wysoki lub niski. Zamiast tego może oscylować lub pozostawać na poziomie napięcia pośrednim przez nieprzewidywalny czas. Może to spowodować, że logika w kolejnym etapie odczyta zniekształconą wartość, co prowadzi do błędów systemu lub awarii. W skrajnych przypadkach metastabilność może się rozprzestrzeniać przez całą pętlę, powodując awarię funkcjonalną, którą trudno jest zdiagnozować.

Q: Jak radzić sobie z przesunięciem zegara? 🔄

Przesunięcie zegara występuje, gdy sygnał zegarowy dociera do różnych komponentów w różnych momentach. Może to być spowodowane różnymi długościami ścieżek lub różnicami obciążenia. Aby zarządzać przesunięciem:

- Zrównoważenie trasy: Upewnij się, że ścieżki zegarowe są wykonywane z podobnymi długościami i szerokościami.

- Buforowanie: Użyj buforów zegarowych do równomiernego zasilania wielu obciążeń.

- Zapasy czasowe: Projektuj system z wystarczającym zapasem czasu w czasie ustawienia i utrzymania, aby pochłonąć niewielkie zmiany przesunięcia zegara.

Q: Jaka jest różnica między synchronicznym a asynchronicznym czasem? ⚖️

W synchroniczny systemach wszystkie operacje są koordynowane przez pojedynczy sygnał zegarowy. Diagramy czasowe dla tych systemów pokazują regularne, powtarzające się krawędzie zegara. W asynchroniczny systemach sygnały wywołują działania bez globalnego zegara. Diagramy czasowe dla tych systemów pokazują przejścia sterowane zdarzeniami, często z większą zmiennością w odstępach między sygnałami. Projektowanie asynchroniczne jest trudniejsze do analizy, ale może być bardziej wydajne pod względem zużycia energii w określonych aplikacjach o niskim zużyciu energii.

PYTANIE: Jak jitter wpływa na diagram czasowy? 📉

Jitter to krótkoterminowa zmienność sygnału względem jego idealnego położenia w czasie. W diagramie czasowym manifestuje się jako krawędzie sygnału zegarowego pojawiające się nieco wcześniej lub później niż powinny. Nadmierny jitter zmniejsza skuteczny okres przechwytywania danych. Efektywnie zmniejsza zapasy czasowe ustawienia i utrzymania, zwiększając ryzyko naruszeń czasowych. Interfejsy wysokiej prędkości wymagają ścisłego kontroli jittera w celu zachowania integralności danych.

PYTANIE: Czy mogę odczytywać diagramy czasowe bez zegara? 🕵️

Tak, ale wymaga to innego podejścia. Protokoły asynchroniczne, takie jak I2C lub UART, nie zawsze wykorzystują wspólną linię zegarową. Zamiast tego opierają się na zdefiniowanych szybkościach transmisji (baud rate) lub sygnałach wymiany danych. W tych diagramach należy analizować szerokość impulsów oraz czas między przejściami, aby wywnioskować szybkość transmisji danych. Na przykład w UART czas trwania bitu startowego określa czas trwania kolejnych bitów danych.

Odczytywanie i interpretowanie przebiegów 🔍

Interpretacja diagramu czasowego wymaga systematycznego podejścia. Losowe przeszukiwanie linii często prowadzi do pominięcia szczegółów. Postępuj zgodnie z tym procesem, aby uzyskać dokładną analizę.

- Zidentyfikuj sygnał odniesienia: Znajdź sygnał zegarowy lub główny sygnał sterujący. Wszystkie pozostałe czasy są względem tego sygnału.

- Sprawdź stany aktywne: Określ, czy sygnały są aktywne wysokim poziomem czy niskim poziomem. Niski impuls może oznaczać „włączony”, podczas gdy wysoki impuls oznacza „wyłączony”. Często oznaczenie to jest widoczne jako kółko na nazwie pinu na schematach.

- Analizuj zgodność krawędzi: Dokładnie przeanalizuj, gdzie krawędzie danych są zgodne z krawędziami zegara. Dane powinny idealnie zmieniać się, gdy zegar jest stabilny (np. w fazie niskiej), a być stabilne podczas aktywnej krawędzi.

- Śledź zależności: Śledź relację przyczyna-skutek. Jeśli sygnał A wywołuje sygnał B, pomiędzy nimi powinien występować wyraźny opóźnienie odpowiadające opóźnieniu propagacji.

- Weryfikuj szerokość impulsów: Upewnij się, że aktywne impulsy są wystarczająco szerokie, aby odbiorca mógł je wykryć. Impuls zbyt cienki może zostać odfiltrowany jako szum.

Powszechne błędy w interpretacji diagramów ❌

Nawet doświadczeni inżynierowie mogą źle interpretować diagramy, jeśli pomijają konkretne szczegóły. Unikaj tych powszechnych pułapek.

- Ignorowanie poziomów logicznych: Zakładanie, że wszystkie sygnały są aktywne wysokim poziomem bez weryfikacji. Zawsze sprawdzaj dokumentację techniczną lub schemat.

- Pomijanie opóźnień propagacji: Zakładanie, że sygnały zmieniają się natychmiast. Komponenty w rzeczywistym świecie mają skończone czasy odpowiedzi.

- Nieprawidłowe odczytywanie skal czasowych: Nie zauważanie jednostki czasu (nanosekundy vs. mikrosekundy). Sygnał wydający się stabilny przy powolnym przybliżeniu może pokazywać zakłócenia przy szybkim przybliżeniu.

- Ignorowanie stanów zasilania: Diagramy czasowe często się zmieniają, gdy urządzenie wchodzi w tryb snu. Upewnij się, że analizujesz aktywny sekwencję czasową.

Strategie dokładnej analizy 🛠️

Aby upewnić się, że analiza czasowa jest odporna, przyjmij te strategie. Te metody pomagają utrzymać spójność i zmniejszają szansę na błąd.

- Używaj linii siatki: Wyrównaj wskaźniki lub znaczniki z liniami siatki na diagramie, aby dokładnie zmierzyć przedziały czasowe.

- Dokumentuj założenia: Zapisz założoną częstotliwość zegara i poziomy logiczne przed rozpoczęciem analizy. Zapobiega to zamieszaniu później.

- Weryfikacja krzyżowa: Porównaj diagram czasowy z logiką maszyny stanów. Każda zmiana stanu powinna mieć odpowiadający jej zdarzenie czasowe.

- Symuluj zmiany: Rozważ najgorsze przypadki. Co się stanie, jeśli temperatura wzrośnie, a opóźnienia się zwiększą? Co jeśli napięcie spadnie, a siła napędu zmniejszy się?

- Skup się na krytycznych ścieżkach: Zidentyfikuj najdłuższą ścieżkę w twojej logice. Ta ścieżka decyduje o maksymalnej częstotliwości zegara systemu. Zadbaj o analizę czasową tych konkretnych tras.

Skutki naruszeń czasowych ⚠️

Zrozumienie, dlaczego czas jest ważny, jest kluczowe. Gdy występuje naruszenie czasowe, zachowanie fizyczne obwodu się zmienia. Najczęstszym skutkiem jest uszkodzenie danych. Rejestr może przechwycić wartość „1”, gdy powinien przechwycić „0”. W protokołach komunikacyjnych powoduje to błędy ramkowania lub utratę pakietów. W systemach sterowania może prowadzić do niepoprawnych poleceń dla aktuatorów, co może spowodować uszkodzenia fizyczne lub zagrożenia bezpieczeństwa.

Dodatkowo, naruszenia czasowe mogą powodować nieregularne awarie. System może działać idealnie w temperaturze pokojowej, ale zawieść, gdy się nagrzeje. Dzieje się tak, ponieważ opóźnienia propagacji rosną wraz z temperaturą. Projektowanie z wystarczającymi marginesami czasowymi uwzględnia te zmiany środowiskowe.

Najlepsze praktyki dotyczące diagramów czasowych 📝

Tworzenie jasnych i dokładnych diagramów czasowych to umiejętność, która poprawia się z praktyką. Postępuj zgodnie z tymi wskazówkami, aby stworzyć diagramy łatwe do zrozumienia dla innych.

- Oznacz wszystko: Każda linia sygnału powinna mieć jasne oznaczenie. Unikaj ogólnych etykiet takich jak „Sygnał 1”.

- Używaj spójnej skali: Utrzymuj jednolitą skalę czasową na całym diagramie, chyba że musisz powiększyć konkretny wydarzenie.

- Wyróżnij krytyczne zdarzenia: Używaj różnych kolorów lub grubszych linii, aby oznaczyć okna ustawienia i utrzymania.

- Dołącz adnotacje: Dodaj notatki tekstowe, aby wyjaśnić złożone interakcje lub konkretne ograniczenia.

- Weryfikuj na podstawie danych technicznych: Zawsze sprawdzaj parametry diagramu pod kątem oficjalnych specyfikacji komponentów.

Zaawansowane rozważania: wiele domen zegarowych 🌐

Nowoczesne systemy często wykorzystują wiele domen zegarowych. Na przykład procesor może działać z częstotliwością 2 GHz, podczas gdy kontroler pamięci działa z częstotliwością 400 MHz. Diagramy czasowe dla takich systemów stają się znacznie bardziej złożone. Musisz uwzględnić:

- Próbowanie między domenami zegarowymi: Jak dane przechodzą z jednej częstotliwości na drugą.

- Bufory FIFO: Jak zsynchronizować przepływ danych między asynchronicznymi zegarami.

- Synchronizacja resetu:Zapewnienie, że wszystkie domeny są resetowane w koordynowany sposób, aby uniknąć niezgodności stanów.

Podczas analizy tych schematów szukaj logiki synchronizacji, takiej jak sygnały wymiany zdań lub łańcuchy synchronizatorów. Te komponenty zostały specjalnie zaprojektowane, aby bezpiecznie pokonywać różnicę między różnymi domenami czasowymi.

Wnioski: Precyzja to klucz 🔑

Diagramy czasowe to więcej niż tylko obrazy; są to dowody matematyczne poprawnie działającego systemu. Określają one granice wiarygodności i wydajności. Zrozumienie podstawowych komponentów, parametrów i potencjalnych pułapek pozwala projektować systemy działające poprawnie w warunkach rzeczywistych. Uwaga na czasy ustawienia, czasy utrzymania i opóźnienia propagacji oddziela funkcjonalny prototyp od produktu gotowego do produkcji. Nieprzerwana praktyka czytania i tworzenia tych diagramów wyostrzy Twoją intuicję techniczną i poprawi wyniki inżynierskie.

Pamiętaj, że każdy zboczenie opowiada historię przepływu informacji. Szanuj czas potrzebny na przemieszczenie tej informacji, a Twoje projekty wytrzymają próbę czasu.