W złożonym świecie inżynierii wbudowanej precyzja nie jest jedynie preferencją; jest wymaganiem. Diagramy czasowe pełnią rolę wizualnego projektu, pozwalającego zrozumieć, jak sygnały oddziałują na siebie w czasie. Te przedstawienia graficzne odwzorowują poziomy napięcia, cykle zegarowe oraz przejścia danych względem osi czasu. Dla inżynierów projektujących mikrokontrolery, czujniki lub interfejsy komunikacyjne opanowanie czytania i tworzenia tych diagramów jest kluczowe dla zapewnienia niezawodności systemu.

Bez jasnego widoku relacji czasowych komponenty sprzętowe mogą nie być w stanie się komunikować, co prowadzi do uszkodzenia danych lub awarii systemu. Ten przewodnik omawia praktyczne zastosowania diagramów czasowych w różnych dziedzinach rozwoju systemów wbudowanych, oferując szczegółowe omówienie ich użyteczności bez wykorzystania konkretnych narzędzi programowych.

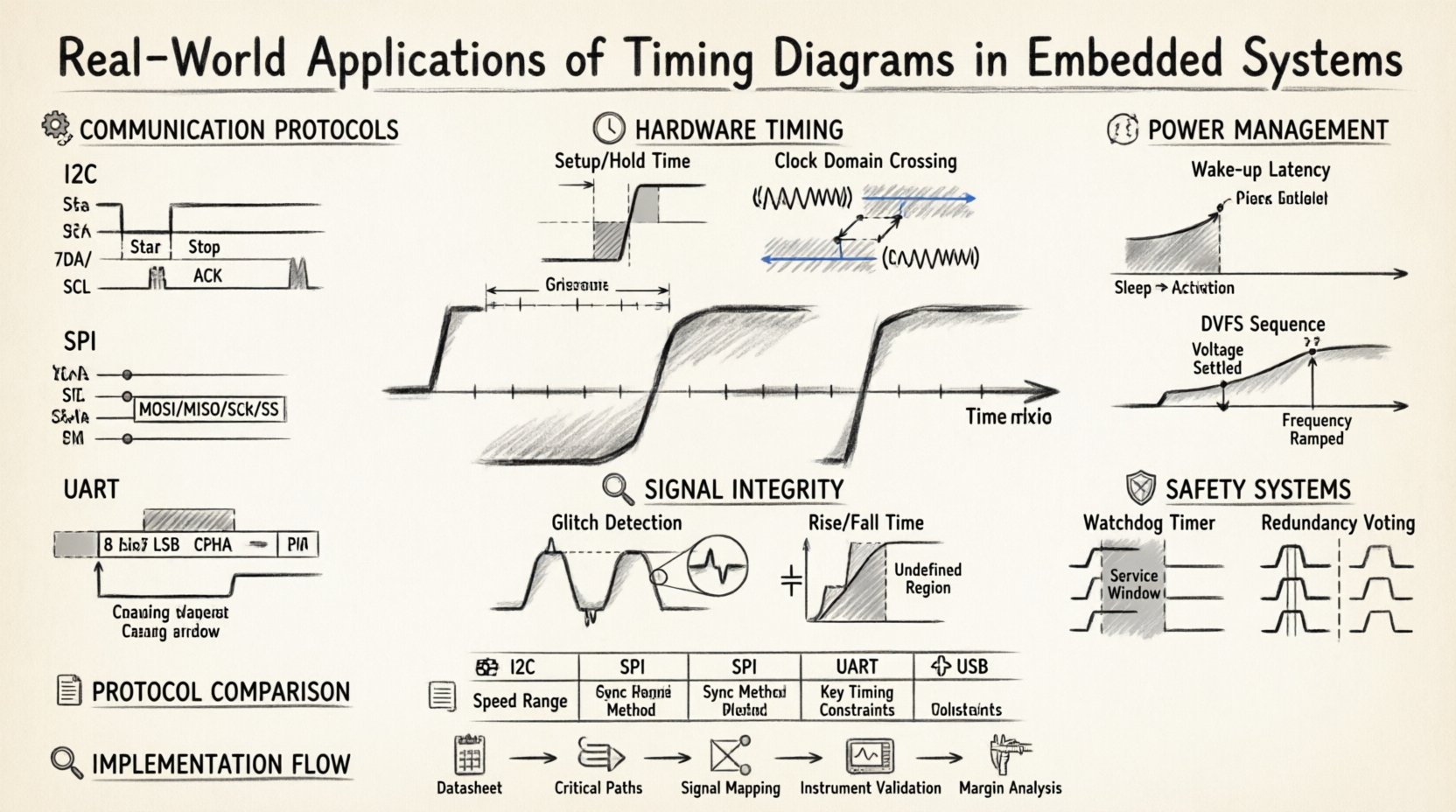

🔌 Analiza protokołów komunikacyjnych

Komunikacja szeregową jest fundamentem nowoczesnych systemów wbudowanych. Dane rzadko pozostają w jednym układzie; poruszają się między procesorami, pamięcią i urządzeniami peripheralnymi. Diagramy czasowe są kluczowe do definiowania i weryfikowania tych interakcji.

Inter-Integracyjny Obwód (I2C)

Protokół I2C wykorzystuje dwukierunkowy interfejs: Dane Szeregowe (SDA) i Zegar Szeregowy (SCL). Diagram czasowy dla I2C ujawnia konkretną sekwencję wymaganą do transmisji danych.

- Warunek rozpoczęcia: Linia SDA przechodzi z wysokiego na niski poziom, podczas gdy linia SCL pozostaje na poziomie wysokim. Sygnalizuje to magistralę, by rozpoczęła transakcję.

- Ramka adresu:Pierwszy wysłany bajt zawiera 7-bitowy adres urządzenia docelowego oraz bit odczytu/zapisu.

- Potwierdzenie:Odbiorca obniża poziom linii SDA podczas dziewiątego impulsu zegarowego, aby potwierdzić odbiór.

- Warunek zakończenia:Linia SDA przechodzi z poziomu niskiego na wysoki, gdy SCL jest na poziomie wysokim, zwalniając magistralę.

Inżynierowie wykorzystują te diagramy do wykrywania problemów takich jak rozciąganie zegara. Jeśli urządzenie niewłaściwe nie może przetworzyć danych wystarczająco szybko, utrzymuje linię SCL na poziomie niskim. Diagram czasowy pokazuje tę ekstensję, umożliwiając projektantowi dostosowanie pętli przetwarzania lub rozmiaru bufora.

Interfejs szeregowy periferyjny (SPI)

SPI to protokół synchroniczny często wykorzystywany do szybszej komunikacji. Używa czterech linii: Wyjście Mistrza do Słowiańskiego (MOSI), Wejście Mistrza od Słowiańskiego (MISO), Zegar Szeregowy (SCK) oraz Wybór Słowiańskiego (SS).

- Polarity zegara (CPOL):Określa stan bezczynności linii zegarowej. Czy jest wysoki czy niski przed rozpoczęciem przesyłania danych?

- Faza zegara (CPHA):Określa, kiedy dane są próbkowane. Czy na pierwszym czy drugim zboczu zegara?

- Czas wyboru układu (Chip Select):Linia SS musi pozostawać na poziomie niskim przez cały czas transakcji. Jeśli przejdzie na poziom wysoki, transakcja zostaje przerwana.

Zrozumienie tych faz jest kluczowe. Niezgodność w CPOL lub CPHA między mistrzem a sługą prowadzi do danych zanieczyszczonych. Diagram czasowy wizualizuje te krawędzie, ułatwiając wykrycie niezgodności podczas włączania sprzętu.

Uniwersalny Asynchroniczny Odbiornik/Wysyłacz (UART)

W przeciwieństwie do SPI i I2C, UART nie wykorzystuje linii zegarowej. Synchronizacja opiera się na ustalonych szybkościach transmisji (baud rate). Diagramy czasowe tutaj skupiają się na czasie trwania bitu i ramkowaniu.

- Bit startowy:Puls niski wskazuje początek bajtu.

- Bity danych: Zazwyczaj 8 bitów, przesyłanych od najmniej znaczącego bitu (LSB) pierwszego.

- Bit stopu: Wysoki impuls sygnalizuje koniec bajtu.

Diagramy czasowe pomagają inżynierom obliczać okno tolerancji. Jeśli zegary dwóch urządzeń odchylają się zbyt dużo, punkt próbkowania przesuwa się, powodując błędy. Diagram ilustruje okno próbkowania, zazwyczaj ustawione w środku czasu bitu.

⏱️ Synchronizacja sprzętowa i czasy przygotowania

Poza komunikacją, diagramy czasowe są niezastąpione do zrozumienia, jak bramki logiczne i przerzutniki wzajemnie się oddziałują. Logika cyfrowa opiera się na dokładnych ograniczeniach czasowych, aby działać poprawnie.

Czasy przygotowania i utrzymania

Gdy dane wchodzą do rejestru lub przerzutnika, muszą spełniać określone wymagania czasowe względem krawędzi zegara.

- Czas przygotowania: Minimalny czas, przez który dane muszą być stabilneprzedprzyjściem krawędzi zegara.

- Czas utrzymania: Minimalny czas, przez który dane muszą pozostać stabilnepoprzyjściem krawędzi zegara.

Jeśli sygnał narusza czas przygotowania, rejestr może przechwycić nieprawidłową wartość. Jeśli narusza czas utrzymania, może wystąpić metastabilność. Diagram czasowy wizualizuje sygnał danych względem krawędzi zegara, wyróżniając zakazane strefy, w których zmiany danych są niedozwolone.

Przejście między domenami zegarowymi (CDC)

Złożone układy często działają w różnych częściach logiki z różnymi częstotliwościami zegara. Przenoszenie danych z szybszej domeny zegarowej do wolniejszej, lub odwrotnie, niesie ryzyko.

- Synchronizacja: Używanie łańcucha przerzutników, aby zapewnić stabilność sygnału przed jego użyciem.

- Uwierzytelnianie: Używanie sygnałów żądania i potwierdzenia, aby koordynować przekaz danych bez wspólnego zegara.

Diagram czasowy dla CDC pokazuje sekwencję uwierzytelniania. Zapewnia, że dane są poprawne przed potwierdzeniem ich odbioru przez odbiorcą. Zapobiega to utracie danych podczas przekazów asynchronicznych.

🔍 Debugowanie i integralność sygnału

Gdy system wbudowany zachowuje się nieoczekiwanie, diagramy czasowe są często pierwszym miejscem, w którym szukają inżynierowie. Dają one historyczny zapis zachowania sygnałów, którego nie można uchwycić testami statycznymi.

Identyfikacja zakłóceń

Zakłócenie to krótki, niechciany impuls na linii sygnału. Może trwać tylko kilka nanosekund, ale może wywołać zmianę stanu w przerzutniku.

- Warunki wyścigu: Występują, gdy kolejność zdarzeń ma znaczenie, a czas jest zbyt krótki.

- Opóźnienie propagacji:Sygnały potrzebują czasu, aby przejść przez bramki logiczne. Diagramy czasowe wyraźnie pokazują te opóźnienia.

Przy nakładaniu oczekiwanego diagramu czasowego na zarejestrowane rzeczywiste sygnały inżynierowie mogą dokładnie wskazać, gdzie występuje odchylenie. Pozwala to na skierowane naprawy w oprogramowaniu lub projekcie sprzętu.

Zapasy szumowe i czasy narastania/spadania

Sygnały z rzeczywistego świata nie są idealnymi falami prostokątnymi. Mają czasy narastania i spadania spowodowane pojemnością i indukcyjnością w śladach.

- Czas narastania: Czas potrzebny na przejście sygnału od niskiego do wysokiego poziomu.

- Czas spadania: Czas potrzebny na przejście sygnału od wysokiego do niskiego poziomu.

Jeśli te przejścia są zbyt powolne, sygnał może zbyt długo przebywać w nieokreślonej strefie napięcia pomiędzy poziomem logicznym 0 a 1. Może to spowodować wywołanie wielu krawędzi zegara lub błędów logicznych. Diagram czasowy pomaga zmierzyć te nachylenia, aby upewnić się, że spełniają one specyfikacje odbiorczego układu.

💤 Zarządzanie energią i stany niskiego zużycia mocy

Efektywność energetyczna jest ważnym zagadnieniem w urządzeniach wbudowanych zasilanych baterią. Diagramy czasowe odgrywają rolę w optymalizacji zużycia energii.

Opóźnienie wzbudzenia

Gdy urządzenie wchodzi w tryb snu, zatrzymuje zegar, aby oszczędzić energię. Wzbudzenie wymaga przywrócenia zegara i ustabilizowania napięcia.

- Czas przejścia: Czas potrzebny na przejście z trybu snu do stanu aktywnego.

- Opóźnienie: Opóźnienie między zdarzeniem wzbudzenia a wykonaniem kodu przez procesor.

Diagram czasowy sekwencji włączania pokazuje opóźnienie między sygnałem wyzwalającym a ustabilizowaniem zegara systemowego. Ta informacja jest kluczowa dla aplikacji czasu rzeczywistego, gdzie opóźnienie kilku milisekund ma znaczenie.

Dynamiczne skalowanie napięcia i częstotliwości (DVFS)

Systemy mogą dostosowywać napięcie i częstotliwość w zależności od obciążenia. Diagramy czasowe pomagają zweryfikować przejścia między różnymi stanami wydajności.

- Nachylenie częstotliwości: Czy zegar zmienia się płynnie czy nagle?

- Ustalanie napięcia: Czy napięcie jest stabilne przed zastosowaniem nowej częstotliwości?

Niepoprawna kolejność podczas DVFS może spowodować spadki napięcia lub błędy logiczne. Diagram czasowy zapewnia weryfikację kolejności potrzebną do zapewnienia bezpiecznych przejść.

🛡️ Systemy krytyczne dla bezpieczeństwa

W zastosowaniach motoryzacyjnych, medycznych i przemysłowych bezpieczeństwo jest najważniejsze. Diagramy czasowe wykorzystywane są do weryfikacji, czy mechanizmy bezpieczeństwa działają w wymaganych granicach czasowych.

Zegary nadzoru (watchdog)

Zegar nadzoru resetuje system, jeśli oprogramowanie zawiesi się. Diagramy czasowe definiują okres wygaśnięcia.

- Okres przekroczenia czasu: Maksymalny czas dozwolony między resetami.

- Okno serwisowe: Czas, w którym oprogramowanie musi zresetować licznik.

Jeśli okno serwisowe jest zbyt długie, zegar nadzorujący może zostać wyzwalany niepotrzebnie. Jeśli jest zbyt krótkie, wolny przerwanie może spowodować fałszywy reset. Diagram zapewnia, że czasowanie jest zgodne z wymaganiami standardów bezpieczeństwa.

Zapasy i głosowanie

Niektóre systemy wykorzystują wiele procesorów do głosowania na poprawny wynik. Diagramy czasowe zapewniają, że wszystkie procesory osiągają etap głosowania jednocześnie.

- Synchronizacja: Wszystkie kanały muszą wyrównać swoje dane.

- Przekroczenie czasu: Jeśli jeden kanał jest spóźniony, system musi wykryć rozbieżność.

To jest krytyczne w układach hamulcowych lub sterowania kierunku, gdzie opóźnienie może być niebezpieczne. Diagram czasowy mapuje opóźnienie każdego kanału, aby zapewnić poprawne działanie logiki głosowania.

📋 Przegląd porównania protokołów

Poniższa tabela podsumowuje kluczowe cechy czasowe powszechnych interfejsów wbudowanych w celu wspomagania wyboru i projektowania.

| Protokół | Zakres prędkości | Metoda synchronizacji | Typowy przypadek użycia | Kluczowy ograniczenie czasowe |

|---|---|---|---|---|

| I2C | 100 kHz do 3,4 MHz | Współdzielony zegar | Czujniki, EEPROM | Rozciąganie zegara |

| SPI | 1 MHz do 50 MHz+ | Zegar główny | Pamięć flash, wyświetlacze | Ustawienie wyboru chipa |

| UART | 9600 do 921600 bps | Asynchroniczny | Debug, GPS, Bluetooth | Dopuszczalna odchyłka szybkości transmisji |

| USB | 1,5 Mbps do 20 Gbps | Oparte na pakietach | Urządzenia peripheralne, pamięć masowa | Czasowanie tokena/rozruchu |

🛠️ Krok po kroku – praktyczne kroki wdrożenia

Tworzenie diagramu czasowego wymaga systematycznego podejścia. Zaczyna się od zrozumienia specyfikacji i kończy weryfikacją.

- Przejrzyj karty katalogowe: Każdy komponent ma sekcję dotyczącą czasowania. Szukaj tabel charakterystyk AC.

- Zidentyfikuj krytyczne ścieżki: Określ, które sygnały decydują o maksymalnej prędkości systemu.

- Zmapuj zależności: Narysuj relacje między sygnałami. Który z nich wywołuje drugi?

- Weryfikuj przy użyciu przyrządów: Użyj analizatorów logicznych lub oscyloskopów do zapisania rzeczywistych przebiegów.

- Analizuj zapasy czasowe: Upewnij się, że pomiędzy sygnałami jest wystarczająco dużo czasu, aby uwzględnić zmiany temperatury i napięcia.

Dokumentacja jest kluczowa. Dobrze oznaczony diagram czasowy służy jako odniesienie do późniejszej konserwacji. Wyjaśnia, dlaczego dodano określone opóźnienia lub dlaczego wybrano konkretne rezystory podciągające.

🚀 Zaawansowane aspekty

Wraz z rosnącą złożonością systemów analiza czasowa wymaga głębszej uwagi.

Jitter i szum fazy

Zegary nie są idealnie stabilne. Jitter to odchylenie krawędzi zegara od jej idealnego położenia. Diagramy czasowe pokazują zmienność położenia krawędzi w ciągu wielu cykli.

- Jitter okresu:Zmienność okresu zegara.

- Jitter cykl do cyklu:Zmienność od jednego cyklu do następnego.

Wysokie drgania zmniejszają marginesy ustawienia i utrzymania. W szybkich interfejsach, takich jak pamięć DDR, może to prowadzić do błędów odczytu/zapisu. Diagramy czasowe pomagają zilustrować te drgania, aby zapewnić, że pozostają w akceptowalnych granicach.

Skutki cieplne

Temperatura wpływa na prędkość tranzystorów. Gdy układ nagrzewa się, sygnały spowalniają.

- Analiza przypadku najgorszego: Projektuj dla maksymalnej temperatury pracy.

- Zmniejszanie mocy cieplnej: Upewnij się, że system nie przekracza bezpiecznych granic cieplnych podczas pracy na wysokich prędkościach.

Diagram czasowy stworzony w temperaturze pokojowej może nie być prawdziwy przy 85°C. Inżynierowie muszą uwzględnić te zmiany cieplne, aby zapewnić trwałość systemu.

📝 Ostateczne rozważania

Diagramy czasowe to więcej niż tylko rysunki; to język synchronizacji. Łączą teorię logiczną z rzeczywistością fizyczną. W systemach wbudowanych, gdzie sprzęt i oprogramowanie się łączą, jasne zrozumienie czasu sygnałów zapobiega kosztownym ponownym projektom i zapewnia niezawodność.

Niezależnie od tego, czy debugujesz protokół komunikacyjny, optymalizujesz zużycie energii, czy zapewniając bezpieczeństwo w krytycznym systemie, te diagramy zapewniają jasność potrzebną do podejmowania świadomych decyzji. Skupiając się na czasach ustawienia, opóźnieniach propagacji i integralności sygnału, inżynierowie mogą tworzyć systemy działające spójnie w warunkach rzeczywistych.

Inwestycja w zrozumienie relacji czasowych przynosi korzyści w postaci stabilności i wydajności. Choć technologia się rozwija, zasady pozostają te same. Czas to stała wielkość, a opanowanie jego pomiaru to klucz do sukcesu w projektowaniu systemów wbudowanych.