數位系統依賴精確的同步才能正確運作。當訊號在錯誤時刻到達時,會產生邏輯錯誤,導致行為不可預測。了解如何分析並修正這些問題,對任何學習數位邏輯、電腦工程或電子學的人來說都至關重要。本指南涵蓋核心概念與實際步驟,用以識別並解決在時序電路與資料傳輸中常見的時序問題。

理解時鐘訊號與邊緣 ⏱️

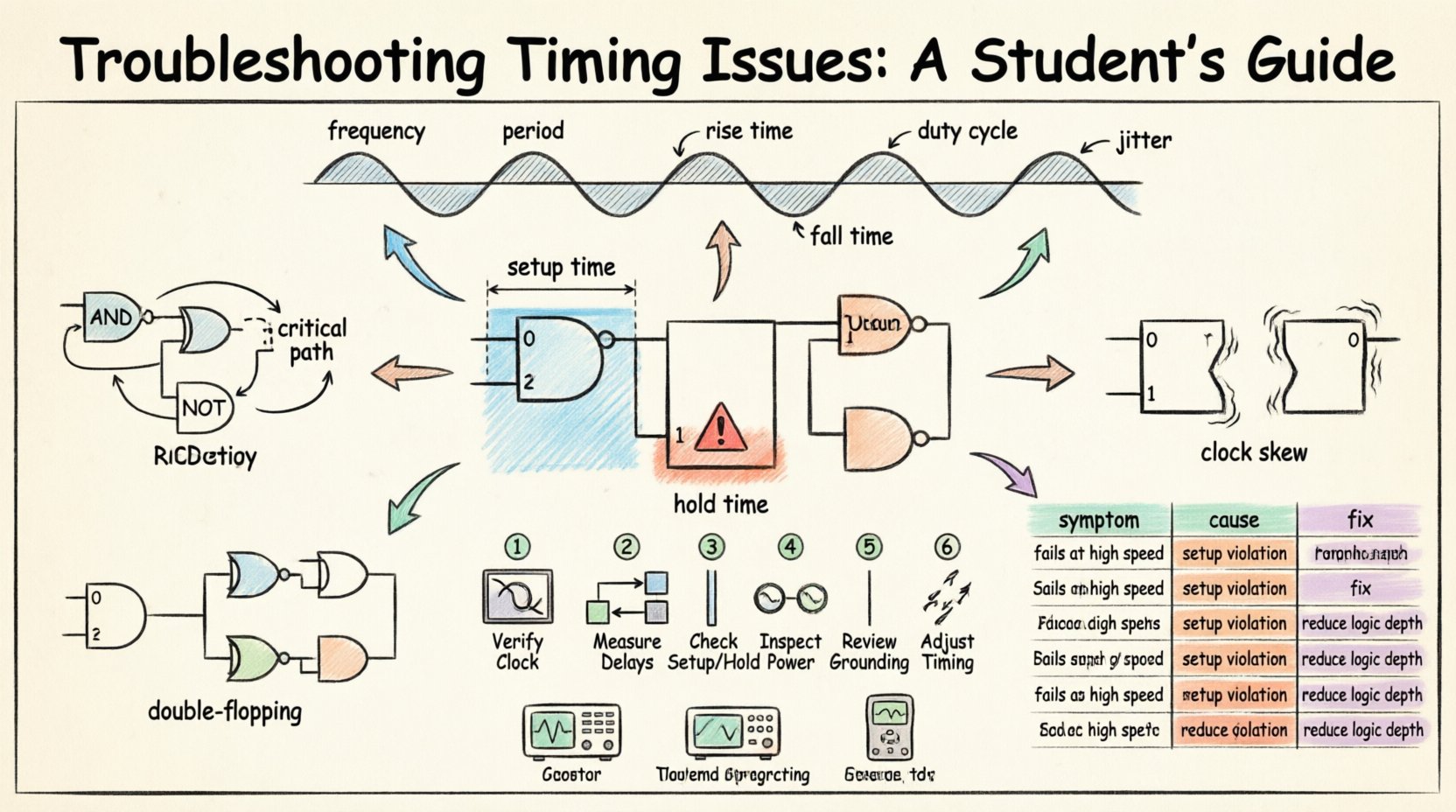

大多數數位設計的核心在於時鐘訊號。此週期性波形決定資料何時被取樣,以及狀態何時變更。故障排除通常從驗證此基本訊號的完整性開始。

- 頻率與週期: 時鐘頻率決定運作速度。週期是完整一個週期的時間長度。若電路需要 100 MHz 的時鐘,週期為 10 納秒。此處的任何偏差都會影響所有下游邏輯。

- 上升與下降時間: 理想的方波是理論上的。實際訊號具有有限的上升與下降時間。若轉換過於緩慢,訊號可能在未定義電壓區域停留過久,導致多次切換或邏輯錯誤。

- 佔空比: 這是訊號處於高電平的時間與總週期的比率。50% 佔空比為標準,但某些設計需要非對稱週期。偏差可能導致設定或保持時間要求的時序餘量偏移。

檢查電路時,請使用示波器或邏輯分析儀來觀察時鐘波形。注意是否有雜訊尖峰、振鈴或過度的抖動。抖動是指時鐘邊緣與其理想時間位置的偏移。高抖動會減少資料穩定所需的實際時序餘量。

設定與保持時間違規 ⚠️

這是在時序邏輯設計中最常見的時序違規。觸發器與鎖存器對資料相對於時鐘邊緣必須穩定的時間有特定要求。

設定時間

設定時間是時鐘邊緣前資料必須穩定的最短時間。若資料在時鐘邊緣附近過於接近地改變,觸發器可能無法捕捉正確的值。

- 限制條件: 提供給觸發器的組合邏輯的傳播延遲,必須小於時鐘週期減去設定時間。

- 症狀: 系統在較低頻率下可能運作正常,但隨著速度提升而失敗。輸出常出現隨機的位元錯誤。

- 解決方法: 減少寄存器之間的邏輯深度,增加時鐘週期,或使用更快的元件。

保持時間

保持時間是時鐘邊緣後資料必須保持穩定的最短時間。若資料在時鐘邊緣後過快改變,觸發器可能遺失所捕捉的值。

- 限制條件: 組合邏輯的傳播延遲必須大於目標觸發器的保持時間。

- 症狀: 保持違規常在任何頻率下發生。這是因為延遲是絕對的,而非相對於週期。

- 解決方法: 在資料路徑中加入延遲緩衝器以減慢訊號,或重新設計邏輯以減少延遲。

釐清這兩者之間的差異至關重要。設定違規與頻率相關,而保持違規則與路徑相關。常見的錯誤是試圖透過減慢時鐘來修復保持違規;這不但無效,反而可能使情況更糟。

傳播延遲與路徑分析 📉

信號不會瞬間傳輸。每條導線、邏輯閘和元件都會引入延遲。分析這些延遲對於確保資料能及時到達至關重要。

- 組合邏輯延遲: 這是指信號通過 AND、OR 和 NOT 等閘門所需的時間。長串的閘門會造成顯著的延遲。

- 互連延遲: 在實體電路板上,導線具有電容和電阻。較長的走線會引入更多延遲。這通常被建模為 RC 網路。

- 腳位到腳位延遲: 從元件的時鐘輸入到資料輸出之間的時間。這通常在資料手冊中指定。

在排錯時,應繪製出關鍵路徑。這是指兩個順序元件之間延遲最長的路徑。如果關鍵路徑超過時鐘週期,設計將失敗。要找出它,需計算所有可能路徑的延遲總和,並識別出最大值。

時鐘偏移與抖動 📶

即使時鐘來源完美,信號也可能在不同時間抵達不同的元件。這種現象稱為偏移。

- 時鐘偏移: 當時鐘信號傳播到不同觸發器的距離不同時就會發生。正偏移會延遲捕獲時鐘,放寬建立時間但縮緊保持時間;負偏移則縮緊建立時間但放寬保持時間。

- 時鐘抖動: 時鐘邊緣定時的短期變化。抖動會減少資料建立可用的時間預算。

- 漂移: 因溫度或電源供應波動,導致時鐘頻率隨時間緩慢變化。

在複雜設計中,偏移通常透過時鐘樹合成來管理。在學生專案中,通常透過均勻佈線時鐘走線並保持其短距離來最小化偏移。若懷疑存在偏移,應同時在電路的多個點測量時鐘。

metastability 與非同步輸入 🌀

當資料變更與時鐘邊緣同時發生時,觸發器會進入 metastability 狀態。它不會立即穩定到 0 或 1,而是在中間電壓水平上懸浮。

- 風險: metastability 可能在系統中傳播,導致難以重現的邏輯錯誤。

- 非同步信號: 來自外部開關或通訊埠的輸入通常與內部時鐘不同步。這些信號必須進行同步。

- 雙觸發器法: 一種常見的解決 metastability 的方法是將信號串聯通過兩個觸發器。第一個觸發器捕獲 metastability 狀態,第二個觸發器在下一個週期中解決該狀態。

應始終將非同步輸入視為潛在的 metastability 來源。不要將它們直接連接到需要嚴格時序的邏輯電路。應使用同步電路,以確保不同時鐘域之間的安全資料傳輸。

逐步排錯工作流程 🛠️

當出現時序問題時,應遵循結構化的方法來定位原因。隨意更改幾乎不會產生效果。

- 驗證時鐘: 檢查頻率、佔空比和振幅。確保信號穩定且乾淨。

- 測量延遲: 使用邏輯分析儀捕獲輸入和輸出波形。測量路徑的實際傳播延遲。

- 檢查建立和保持時間: 根據測量的延遲計算路徑是否滿足建立和保持時間約束。

- 檢查電源: 電壓下降會減慢邏輯門的運作。確保電源穩定並能提供足夠的電流。

- 檢視接地: 接地不良會引入類似時序錯誤的雜訊。檢查是否存在接地迴路和共用回路。

- 調整時序: 如果設計具有彈性,可調整時鐘頻率或增加緩衝器以平衡路徑。

文件記錄在此過程中至關重要。記錄波形和測量數據。這些資料有助於將預期行為與實際性能進行比較。

常見錯誤參考表 📊

可使用此表格作為診斷特定症狀的快速參考。

| 觀察到的症狀 | 可能原因 | 建議操作 |

|---|---|---|

| 系統在高速下失效 | 建立時間違反 | 減少邏輯深度或增加時鐘週期 |

| 系統在低速下失效 | 保持時間違反 | 在資料路徑中增加延遲緩衝器 |

| 隨機位翻轉 | 信號雜訊或抖動 | 檢查屏蔽和電源穩定性 |

| 輸出掛起或重置 | 亞穩態 | 實施同步鏈 |

| 行為不一致 | 時鐘偏移 | 平衡時鐘走線長度 |

| 完全沒有輸出 | 時鐘未啟用 | 確認時鐘分配與使能信號 |

工具與儀器 📏

雖然模擬工具很有用,但實際驗證通常需要特定的硬體。正確使用這些儀器的知識,是故障排除技能的一部分。

- 示波器:用於觀察電壓水平與信號形狀的必要工具。使用高阻抗探頭以避免負載電路。

- 邏輯分析儀:更適合數位信號。它能捕捉隨時間變化的邏輯狀態(0 或 1)。可針對特定模式觸發,以定位錯誤。

- 頻率計:當無法使用示波器時,用於確認時鐘源的精確頻率。

確保探頭正確補償。未補償的探頭會扭曲信號形狀,導致對上升時間與延遲的錯誤判斷。

信號完整性最後考量 🔒

時序問題通常是更廣泛信號完整性問題的症狀。隨著電路速度提升,電路板的物理特性變得更加重要。

- 串擾:相鄰導線上的信號可能互相干擾。應將高速線與敏感線分開佈線。

- 阻抗匹配:若走線阻抗與驅動器或接收器不匹配,就會產生反射。這些反射可能看起來像時序延遲。

- 熱效應:隨著元件加熱,其電氣特性會改變。這可能改變傳播延遲,並導致負載下的時序失效。

時序設計需要全面的觀點。這不僅僅是邏輯閘的問題,更涉及信號傳輸的物理媒介。遵循這些原則,學生才能建立在各種條件下都能可靠運作的穩健系統。

定期使用實際硬體進行練習,有助於內化這些概念。理論提供架構,但實際調試則培養解決複雜時序問題所需的直覺。