在嵌入式工程的複雜世界中,時序至關重要。微控制器可能在模擬中運作完美,卻因幾納秒的延遲而在硬體上災難性地失敗。這正是時序圖成為不可或缺工具的原因。這些視覺化表示法可呈現信號隨時間的行為,清楚地展現數位系統中各組件之間的互動情形。無論您是在除錯通訊失敗,還是設計新的周邊介面,掌握如何閱讀與製作時序圖都是根本要務。

本指南涵蓋信號時序的基本機制,從基本定義到複雜協定互動。我們將探討如何解讀波形、從測量資料建構精確的圖表,並辨識導致系統不穩定的常見陷阱。透過掌握這些視覺化工具,您將具備預測系統行為並在設計離開工作台前進行驗證的能力。

🔍 理解信號時序的基礎

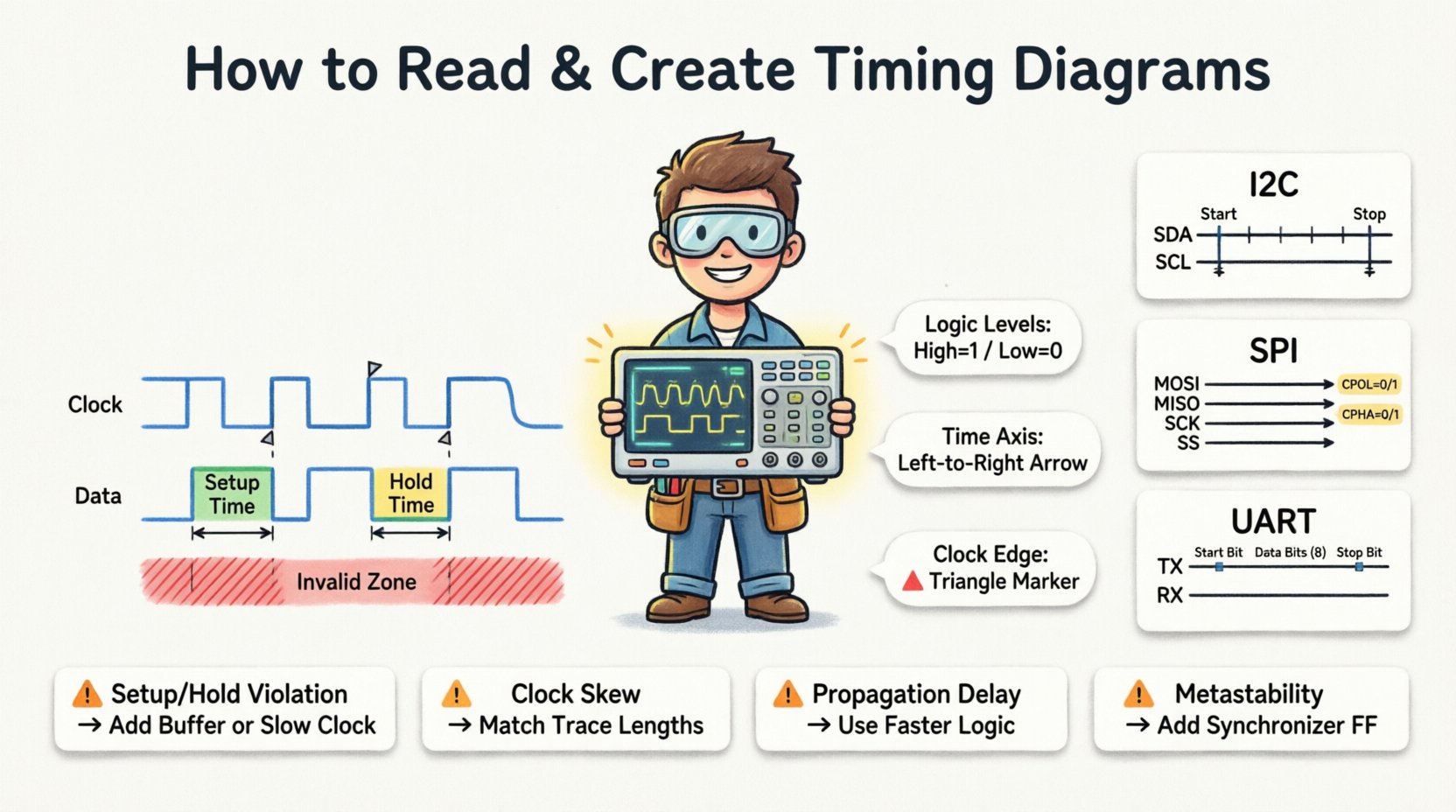

時序圖不僅僅是一張圖畫;它是邏輯狀態相對於時間軸的數學表示。在嵌入式系統中,我們主要處理數位邏輯電平,這些電平是二進位的:高電平(1)與低電平(0)。然而,這些電平之間的轉換才是複雜性的所在。

- 邏輯電平:大多數嵌入式系統運作於特定的電壓閾值。例如,3.3V系統將高電平定義為任何超過2.0V的電壓,低電平則為任何低於0.8V的電壓。

- 時間軸:時間由左向右流動。水平間距代表特定狀態的持續時間,或事件之間的延遲。

- 信號軌跡:每一條水平線代表一條特定的導線或網路。多條線垂直堆疊,可讓您比較信號之間的關係。

分析系統時,您尋找的是因果關係。時鐘信號是否觸發資料變更?使能信號是否必須在資料有效前就處於激活狀態?時序圖能以視覺方式回答這些問題。

🛠️ 時序圖的關鍵元件

要正確解讀圖表,您必須辨識用來表示信號行為的標準元件。這些元件定義了硬體互動的規則。

| 元件 | 描述 | 視覺指示 |

|---|---|---|

| 信號名稱 | 識別特定的導線或網路 | 位於左側的文字標籤 |

| 邏輯電平 | 高電平(1)或低電平(0)狀態 | 位於頂部或底部的水平直線 |

| 轉換邊緣 | 由高電平轉為低電平,或反之 | 連接電平的垂直線 |

| 時鐘邊緣 | 同步邏輯的觸發點 | 虛線或三角形標記 |

| 無效區域 | 資料無法讀取的區域 | 陰影或斜線區域 |

理解這些元件可讓你拆解複雜的互動。例如,陰影區域通常表示設定時間或保持時間的要求,此時接收裝置無法可靠地捕捉資料。

👁️ 如何逐步閱讀時序圖

閱讀時序圖需要系統性的方法。你本質上是在將視覺模式轉譯為一系列事件。遵循此流程可確保準確性。

1. 確定時鐘來源

大多數嵌入式系統都是同步的,表示時鐘信號決定了操作的節奏。找出時鐘訊號路徑,它通常呈現規律且週期性的方波。

- 檢查頻率。是 1 MHz 還是 100 MHz?這決定了整個系統的速度。

- 辨識邊緣類型。裝置是於上升沿(低至高)還是下降沿(高至低)觸發?

2. 繪製資料有效窗口

資料僅在相對於時鐘的特定時間窗內有效。請觀察時鐘邊緣與資料線之間的關係。

- 設定時間: 資料必須在一段特定時間內保持穩定 在時鐘邊緣之後。

- 保持時間: 資料必須在一段特定時間內保持穩定 在時鐘邊緣之後。

如果資料在這些時間窗內變動,就會發生時序違規,導致 metastability 或錯誤的資料捕捉。

3. 分析控制訊號

控制訊號如晶片選擇(CS)、使能(EN)或重置(RST)決定了通訊何時可以發生。

- 晶片選擇是低電平有效還是高電平有效?

- 使能訊號是否需要在時鐘開始切換前被置位?

- 是否有任何非同步事件會覆蓋時鐘邏輯?

4. 驗證握手機制

許多協定使用握手來管理流量控制。請尋找確認(ACK)或就緒(RDY)訊號。

- 發送端是否在傳輸下一個位元前等待訊號?

- 圖中是否表示了逾時條件?

📐 如何建立精確的時序圖

建立時序圖與閱讀時序圖一樣重要。它為硬體工程師提供規格說明,為軟體開發人員提供驗證指南。您可以從需求、量測工具或模擬資料中產生這些時序圖。

步驟 1:定義通訊協定需求

繪製之前,請先收集規格。這些規格通常來自您所介接元件的資料手冊。

- 提取最低與最高的時鐘頻率。

- 注意邏輯高電平與低電平的電壓水準。

- 記錄建立時間與保持時間的限制。

步驟 2:擷取信號資料

使用硬體工具來擷取實際世界中的行為。這可確保您的時序圖反映現實,而非理論上的理想狀態。

- 示波器:最適合用於類比信號完整性與電壓水準。

- 邏輯分析儀:最適合用於數位狀態轉換與多通道時序。

- 模擬模型:在硬體尚未可用時,非常適合用來驗證邏輯。

步驟 3:繪製波形

依時間順序繪製信號。確保所有通道的時間比例一致。

- 邏輯電平使用直線。

- 使用斜線表示轉換,以顯示上升與下降時間。

- 標示關鍵點,例如時鐘邊緣與資料變更。

步驟 4:標註關鍵限制

註解提供了視覺圖像本身無法傳達的背景資訊。

- 明確標示建立時間與保持時間的時間窗。

- 標示特定通訊協定狀態的持續時間(例如:起始位元、停止位元)。

- 強調信號路徑中任何已知的延遲或延遲時間。

🌐 常見嵌入式協定中的時序圖

不同的通訊協定具有獨特的時序特性。理解這些細節對於整合至關重要。

1. 互連式電路(I2C)

I2C 是一種雙線同步串列匯流排。它使用 SDA(資料)與 SCL(時鐘)。

- 起始條件: 當 SCL 為高電平時,SDA 從高電平轉為低電平。

- 停止條件: 當 SCL 為高電平時,SDA 從低電平轉為高電平。

- 資料傳輸: 當 SCL 為高電平时,資料有效;變更發生在 SCL 為低電平时。

- 確認/非確認: 接收器在第九個時鐘脈衝期間將 SDA 拉低,以確認接收。

2. 串行外設介面(SPI)

SPI 是一種四線同步匯流排,速度高於 I2C。

- 線路: MOSI(主機輸出)、MISO(主機輸入)、SCK(時鐘)、SS(從機選擇)。

- CPOL: 時鐘極性決定空閒狀態(高或低)。

- CPHA: 時鐘相位決定資料採樣的時機(第一個或第二個邊緣)。

- 晶片選擇: 必須在時鐘開始切換之前被置位(激活)。

3. 通用非同步收發器(UART)

UART 為非同步,表示沒有共用的時鐘信號。時序依賴於波特率。

- 起始位: 將線路拉低,以標示資料幀的開始。

- 資料位: 以最低有效位(LSB)優先傳輸,通常為 8 位。

- 停止位: 將線路拉高,以標示資料幀的結束。

- 奇偶校驗: 用於錯誤檢查的可選位。

| 特性 | I2C | SPI | UART |

|---|---|---|---|

| 時鐘 | 同步(共用) | 同步(共用) | 非同步(無時鐘) |

| 導線 | 2(SDA、SCL) | 4+(MOSI、MISO、SCK、SS) | 2(TX、RX) |

| 定址 | 是(位元組定址) | 否(依布線) | 否 |

| 最大速度 | ~400 kHz | ~50 MHz | ~3 Mbps |

⚠️ 常見的時序違規與除錯

即使設計謹慎,仍可能發生時序違規。這通常是難以重現的間歇性錯誤的根本原因。

1. 建立與保持時間違規

當資料相對於時鐘邊緣到達過早或過晚時,就會發生此類問題。

- 症狀: 資料損壞或邏輯分析儀捕獲中的隨機錯誤。

- 解決方法: 降低時鐘速度或優化PCB走線長度。

2. 時鐘偏移

當時鐘信號以不同時間到達不同元件時,就會發生時鐘偏移。

- 症狀: 競爭條件,其中一個正反器在另一個尚未準備好時就捕獲資料。

- 解決方法: 使走線長度一致,或使用專用的時鐘分配網路。

3. 傳播延遲

信號需要時間通過導線和邏輯門。長的走線會帶來顯著的延遲。

- 症狀: 高速線路上的信號完整性問題或反射。

- 解決方法: 使用終端電阻,並盡可能縮短走線長度。

4. 靜態不穩定性

當異步信號跨越時鐘域時,接收端的觸發器可能會進入靜態不穩定狀態。

- 症狀: 系統卡死或隨機重啟。

- 解決方法: 使用同步鏈(兩個或更多觸發器串聯)來解決信號問題。

📝 文件編寫的最佳實踐

為文件編寫時序圖,可確保未來的開發人員能理解系統,而無需逆向工程硬體。

- 一致性: 在專案的所有圖表中使用標準符號和線條樣式。

- 比例: 確保時間軸為線性且明確標註單位(ns、µs、ms)。

- 參考: 始終將圖表與特定的資料手冊章節或協定標準連結。

- 清晰度: 避免雜亂。若信號為靜態,應以水平線顯示,而非顯示切換的雜訊。

- 版本控制: 硬體或固件發生重大變更時,應更新圖表。

🔗 關於信號完整性的最後思考

時序圖彙集了抽象邏輯與物理現實之間的差距。它讓工程師能夠視覺化數位電子中那些看不見的限制。學會閱讀時序圖,你就能排除複雜的硬體問題;學會繪製時序圖,你就能設計出在各種條件下都能可靠運作的穩健系統。

這個過程需要耐心與細心。每一個邊緣、每一個延遲、每一個電壓級別都至關重要。隨著嵌入式系統變得更快、更複雜,對精確時序圖的依賴將只會增加。應將其視為關鍵規格,而非可有可無的文件。

從分析你所使用的元件資料手冊開始。尋找時序規格。然後根據這些數值嘗試繪製圖表。將你的繪圖與工具實際測量結果進行比較。這種預測與驗證的循環,能培養高階嵌入式設計所需的直覺。

請記住,圖表是一種溝通工具。它應以最少的歧義向其他工程師傳達必要資訊。清晰且準確的時序圖能縮短開發時間,並避免昂貴的硬體修改。投入時間掌握這項技能,將在你的工程生涯中帶來長期回報。