理解信號隨時間的流動是數位電子學的基礎。對於本科生工程師而言,掌握時序圖的解讀不僅是學術練習;更是設計可靠系統的關鍵技能。這些視覺化表示法在時間軸上描繪出信號的行為,揭示時鐘週期、資料有效性與控制信號之間的關係。若未能牢固掌握這些技術,即使簡單的電路在現實條件下也可能失效。

本指南涵蓋了有效閱讀、創建和分析時序圖所需的關鍵原則。我們將探討同步與非同步設計的機制、建立時間與保持時間的重要性,以及如何避免導致電路失效的常見陷阱。在本文結束時,您將具備應對複雜數位邏輯問題的穩固基礎。

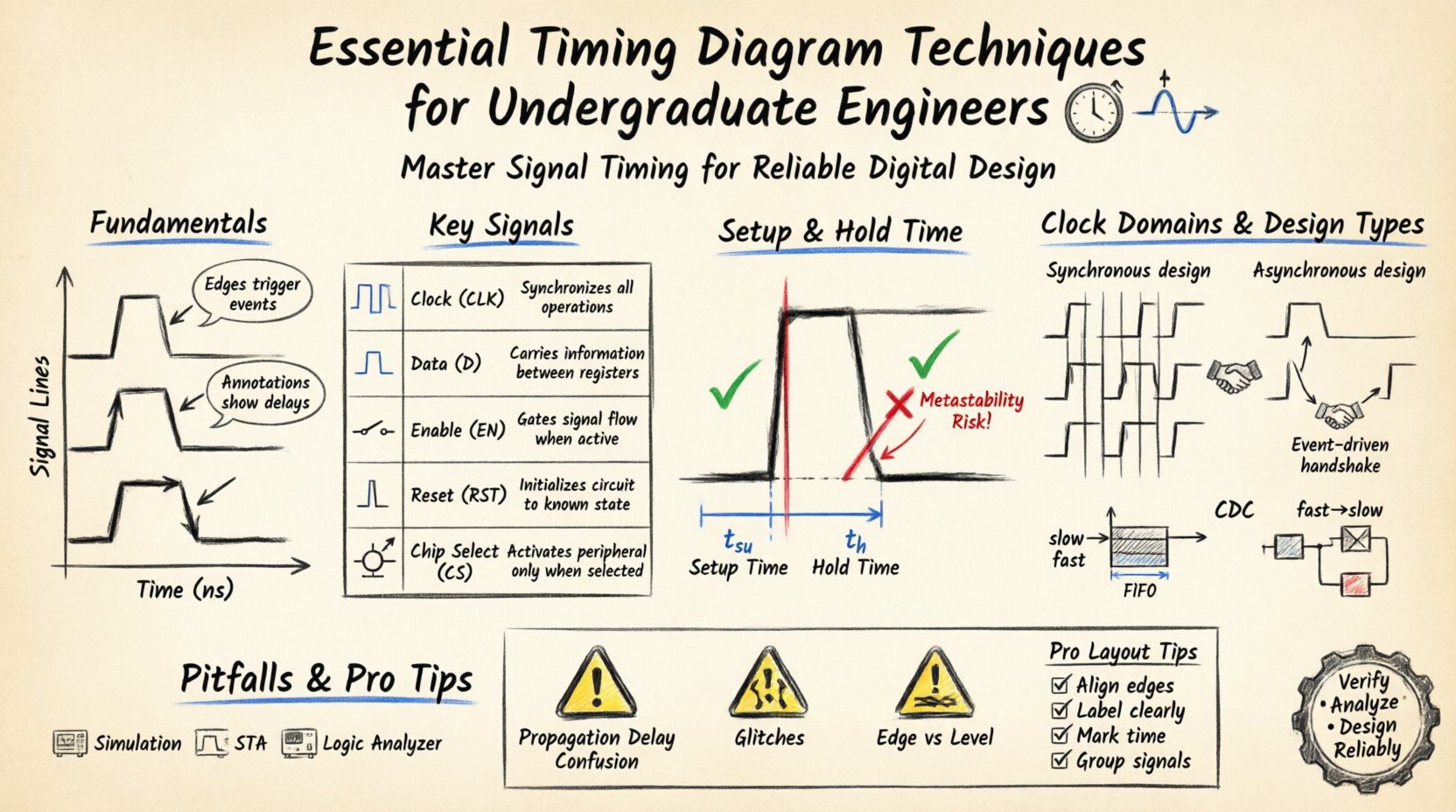

1. 時序圖的基本原理 📐

時序圖是信號隨時間變化的圖形化表示。它讓工程師能夠直觀地觀察數位電路中各條線路的狀態。與顯示連接關係的邏輯圖不同,時序圖展現的是行為。它們對於除錯、驗證設計以及在硬體模組之間傳達信號互動至關重要。

時序圖的關鍵組成部分

- 時間軸(X軸):代表時間的推進。通常以奈秒(ns)或時鐘週期為單位標示。

- 信號線(Y軸):代表單獨電線或匯流排的水平線。每條線對應一個特定的信號名稱。

- 邏輯電平:信號通常是二進位的,以高電平(1)或低電平(0)表示。有時在匯流排設計中會出現『高阻態』(High-Z)狀態。

- 邊緣:垂直轉換表示狀態的變化。上升沿(低至高)與下降沿(高至低)對於觸發事件至關重要。

- 註解:文字標籤通常用來標示延遲、特定時間或影響信號的條件。

為何時序在數位邏輯中至關重要

數位系統依賴精確的同步。如果信號相對於時鐘邊緣到達得太早或太晚,系統可能會誤解資料。時序圖使這些限制變得可見。它們有助於回答以下問題:

- 資料在時鐘邊緣前是否穩定?

- 信號通過邏輯閘需要多長時間?

- 來自不同時鐘域的兩個時鐘是否會互相干擾?

2. 關鍵信號與元件 ⚡

在分析複雜波形之前,您必須識別數位工程中使用的標準信號。這些信號決定了資料如何傳輸以及何時被視為有效。

常見信號類型

| 信號名稱 | 功能 | 典型行為 |

|---|---|---|

| 時鐘(CLK) | 同步來源 | 在 0 與 1 之間規律脈衝 |

| 資料 (D) | 資訊載體 | 根據輸入或邏輯改變狀態 |

| 啟用 (EN) | 啟用模組 | 高電平以允許操作,低電平以禁用 |

| 重置 (RST) | 初始化狀態 | 啟動時為低電平有效或高電平有效脈衝 |

| 晶片選擇 (CS) | 選擇裝置 | 低電平有效以指定特定元件 |

理解控制訊號的激活狀態至關重要。某些訊號為高電平有效,表示電壓高時才會運作。其他訊號為低電平有效,以名稱上方的橫線表示(例如,/重置 或 RST_N),表示電壓低時才會運作。

3. 建立時間與保持時間分析 🕒

時序分析中最關鍵的方面之一是建立時間與保持時間。這些參數定義了資料必須相對於時鐘邊緣保持穩定的時間窗。違反這些限制將導致資料損壞或亞穩態。

建立時間 (tsu)

建立時間是指資料必須保持穩定的最短時間在主動時鐘邊緣到達之前。如果資料在時鐘邊緣附近變動過快,觸發器可能無法捕捉正確的值。

- 要求:資料必須在 tsu上升沿之前保持穩定。

- 違反後果: 記憶體可能捕捉到錯誤的資料,或進入未定義的狀態。

保持時間 (th)

保持時間是指資料必須保持穩定的最短時間在有效時鐘邊緣之後。觸發器需要一段時間來鎖定數值,以避免新資料可能到達。

- 要求:資料必須在 th上升沿之後保持穩定。

- 違反後果:與建立時間違反類似,這會導致資料錯誤或亞穩態。

視覺化建立時間與保持時間

閱讀時序圖時,請觀察資料信號相對於時鐘邊緣的位置。在建立視窗(之前)和保持視窗(之後)期間,資料線應保持平坦且不變動。如果資料線在這些視窗內切換,則設計很可能有問題。

4. 時鐘域交叉 ⏱️

在複雜系統中,電路的不同部分可能以不同的時鐘速度或頻率運作。在這些不同的時鐘域之間傳輸資料稱為時鐘域交叉(CDC)。此過程會帶來顯著的時序挑戰。

時鐘域的類型

- 相同頻率,相同相位:同步設計。適用簡單的時序分析。

- 相同頻率,不同相位:需要相位對齊檢查。

- 不同頻率:需要同步技術,例如握手或 FIFO 缓衝區。

在時序圖中處理 CDC

在分析具有多個時鐘域的圖表時,請確保清楚區分時鐘線。若未妥善管理,資料從慢速域傳輸到快速域可能具有風險。相反地,快速到慢速的傳輸若接收端採樣過快,則可能導致資料遺失。

- 握手協定: 使用 valid/ready 訊號來確認資料傳輸完成。

- FIFO 缓衝區: 解耦生產與消耗速率。

- 同步器: 使用多級觸發器以降低亞穩態風險。

5. 同步設計與非同步設計 🔄

設計架構決定了時序圖的呈現方式。理解兩者的差異有助於預測信號行為。

同步設計

大多數數位邏輯都是同步的。所有狀態變更都發生在中央時鐘信號的邊緣。

- 可預測性: 因為時序受到控制,所以更容易分析。

- 時序圖: 有規律的格狀模式。資料變更與時鐘邊緣對齊。

- 限制: 時鐘偏移在大型設計中可能成為問題。

非同步設計

狀態變更取決於信號的到達,而非全域時鐘。這在握手協定和中斷處理中很常見。

- 彈性: 因為僅需等待資料,所以對特定任務可能更快。

- 時序圖: 不規則。信號取決於先前事件,而非固定時間區段。

- 風險: 若設計不當,容易產生競態條件與 hazards。

6. 常見陷阱與錯誤 ❌

即使經驗豐富的工程師在解讀或製作時序圖時也會犯錯。了解這些常見錯誤可大幅節省調試時間。

1. 忽略傳播延遲

信號不會瞬間改變。邏輯閘具有傳播延遲。若你繪製時假設變更是立即發生的,模擬結果將與現實不符。

- 修正: 在圖中邏輯轉換之間始終包含延遲值。

2. 錯誤解讀低電平有效信號

一個標記為/CS在有效時為低電平。若你假設它為高電平,你的邏輯將被反相。

- 修復:檢查資料手冊或電路圖以確認有效狀態。注意邏輯閘上的圓圈。

3. 忽略雜訊脈衝

雜訊脈衝是短暫且非預期的脈衝。當信號通過不同延遲的路徑時可能產生。

- 修復:使用無危害邏輯,或在設計中加入濾波階段。

4. 混淆邊緣觸發與電平觸發

某些電路在上升沿觸發,其他在下降沿觸發,還有些則根據電平本身觸發。

- 修復:確認元件規格中的觸發條件。

7. 閱讀與創建專業圖表 📝

清晰的溝通在工程中至關重要。一張繪製良好的時序圖能一眼傳達複雜資訊。以下是創建時序圖的最佳實務。

佈局最佳實務

- 對齊邊緣:確保相關信號在一致的時間間隔內變換。

- 清楚標示:使用信號名稱,而非僅僅通用的線條。

- 標示時間:標示週期或特定延遲的持續時間。

- 分組信號:將相關信號(如資料匯流排線路)集中整理。

逐步創建流程

- 識別時鐘:首先繪製時鐘線路。它們是時序的骨幹。

- 加入控制信號:放置使能、重置與晶片選擇線路。

- 繪製資料:根據邏輯流程加入資料線路。

- 註解:加入關於建立/保持時間或特定延遲的註解。

- 審查: 檢查是否有違規情況以及邏輯一致性。

8. 分析現實世界中的情境 🔍

讓我們考慮一個涉及記憶體讀取操作的情境。這對於從事微控制器工作的工程師來說是一項常見任務。

記憶體讀取週期

在記憶體讀取過程中,處理器會送出位址,設定讀取命令,並等待資料。

- 位址匯流排: 在時鐘邊緣前有效。

- 晶片選擇: 變為低電平以啟動記憶體。

- 讀取命令: 變為低電平以啟動傳輸。

- 資料匯流排: 在記憶體驅動之前保持高阻抗狀態。

- 時序: 資料必須在處理器採樣前保持穩定。

信號完整性考量

隨著頻率增加,信號完整性成為主要因素。反射、串擾和雜訊可能扭曲波形。高速設計中的時序圖必須考慮這些物理層面的問題。

- 上升速率: 訊號轉換的速度。太快會產生雜訊;太慢則會導致時序錯誤。

- 電壓電平: 確保在溫度和電壓變化下,邏輯閾值都能滿足。

9. 高階時序概念 🧠

對於希望深化專業知識的人而言,幾項高階概念可延伸基本的時序分析。

metastability( metastability)

當觸發器無法在規定時間內轉換至穩定的 0 或 1 狀態時,就會發生 metastability。這通常發生在資料變更過於接近時鐘邊緣時。

- 機率: 這是一種機率事件,而非決定性事件。

- 緩解措施: 使用同步鏈(串接多個觸發器)將機率降低至接近零。

時鐘偏移

時鐘偏移是指時鐘信號在電路不同部分到達時間的差異。正偏移(較晚到達)有助於建立時間,但會影響保持時間;負偏移則產生相反的效果。

- 設計影響: 時鐘偏移必須納入時序預算中考慮。

- 測量: 使用示波器或模擬工具來測量偏移。

抖動

抖動是指時鐘邊沿與其理想位置的偏離。它會減少有效的建立與保持時間裕量。

- 類型:週期抖動、週期間抖動與隨機抖動。

- 影響: 高抖動會限制系統的最大工作頻率。

10. 工具與方法論 🛠️

雖然手動分析具有教育意義,但現代工程依賴於工具。然而,理解背後的理論才是有效使用這些工具的關鍵。

模擬軟體

硬體描述語言(HDL)允許進行模擬。這些工具可從程式碼自動產生時序圖。你必須理解輸出結果,才能驗證程式碼的正確性。

靜態時序分析(STA)

STA工具透過數學方式驗證所有路徑是否符合時序要求,無需模擬。它們會在所有角落(溫度、電壓)下檢查建立與保持時間的違規情況。

使用邏輯分析儀進行除錯

硬體除錯工具可從電路板上擷取真實信號。它們顯示與實際情況相符的時序圖,有助於識別模擬可能忽略的物理層問題。

結論 🏁

時序圖是數位信號行為的語言。它們架起了抽象邏輯與物理現實之間的橋樑。對於大學工程師而言,投入時間掌握這些技術,將在整個職業生涯中帶來回報。無論你是在設計簡單的計數器還是複雜的處理器,能夠閱讀與分析時序約束都是不可或缺的。

透過專注於建立與保持時間、理解時鐘域,並避免常見陷阱,你將建立穩固的基礎。請記住,務必始終驗證活動狀態,並考慮傳播延遲。隨著你進步,你將遇到更複雜的場景,但核心原則始終不變。持續練習圖形分析,你的設計將變得更可靠且高效。

繼續透過研究資料手冊與檢視真實電路波形來精進你的技能。數位工程領域快速演進,但時序分析的基礎始終不變。