數位系統依賴精確的同步才能正確運作。若缺乏準確的時序,資料損毀、系統當機與安全失效將不可避免。時序圖提供信號隨時間變化的視覺化表示,清楚呈現時鐘週期、資料有效性與控制信號之間的關係。本指南探討時序圖在各個領域中的關鍵角色,詳述實際範例與常見挑戰的技術解決方案。

🔍 理解基本原理

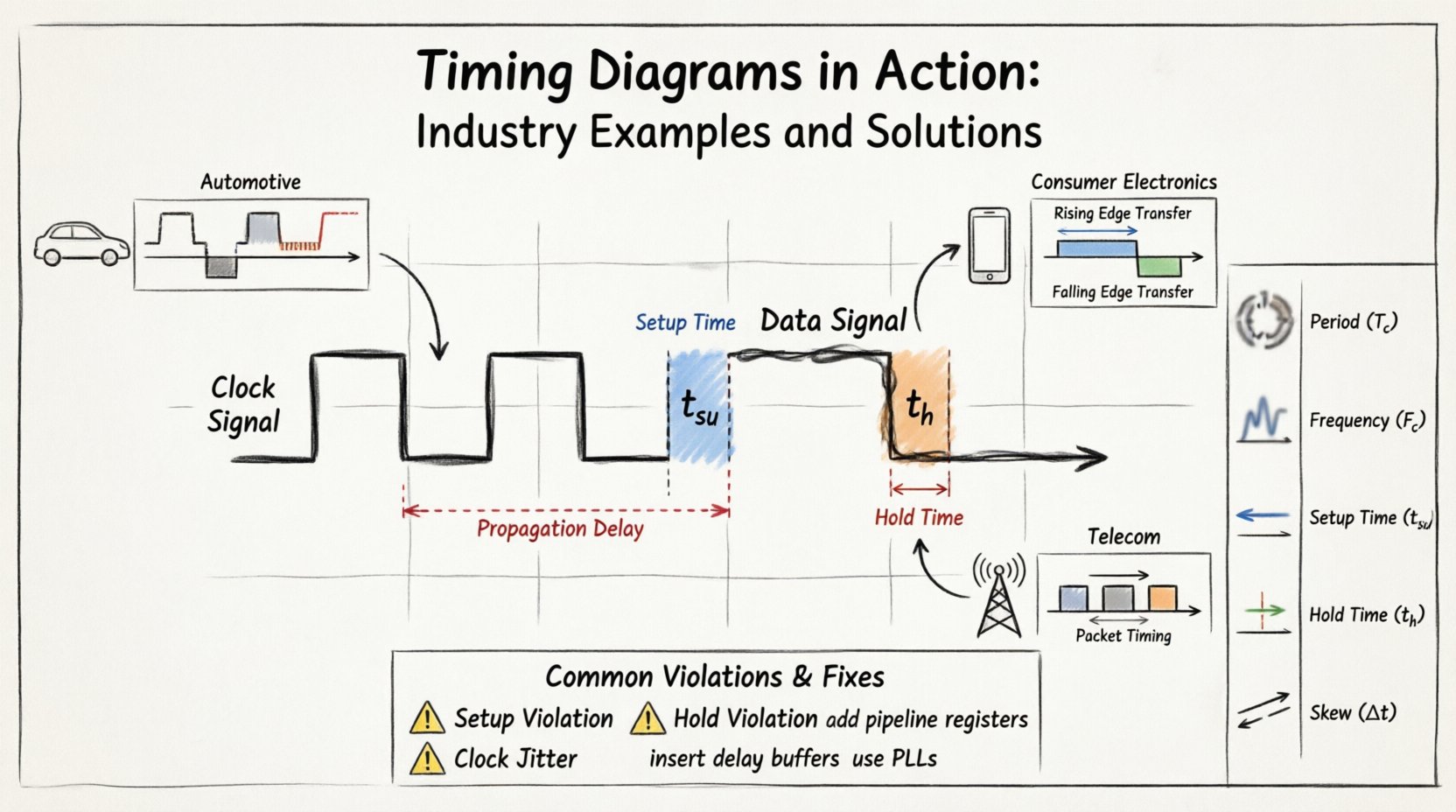

在深入探討特定應用之前,掌握時序圖的核心元件至關重要。這些圖表以參考時鐘為基準,描繪信號的行為。它們不僅僅是繪圖;更是決定硬體行為的數學限制。

- 信號邊緣: 從低電平轉為高電平(上升邊緣)或從高電平轉為低電平(下降邊緣)會觸發順序邏輯中的狀態變更。

- 時鐘週期: 兩個同極性邊緣之間的持續時間,定義了邏輯穩定所需的可用時間。

- 傳播延遲: 訊號透過邏輯閘從輸入接腳傳送到輸出接腳所需的时间。

- 建立時間與保持時間: 關鍵限制條件,確保資料在時鐘邊緣前後都保持穩定。

當這些參數遭到違反時,電路可能進入亞穩態,導致行為不可預測。工程師利用時序圖來驗證設計的實際實現是否符合這些邏輯要求。

🚗 汽車電子:安全關鍵時序

汽車產業要求最高的可靠性。車輛內包含數十個電子控制單元(ECUs),透過如CAN(控制器區域網路)、LIN(局部互連網路)和FlexRay等匯流排進行通訊。在此領域,時序分析不僅關乎速度,更關乎確定性與安全性。

1. CAN匯流排仲裁

CAN匯流排允許多個節點在單一導線上通訊。CAN仲裁的時序圖揭示了在匯流排競爭期間優先權是如何決定的。

- 主導位元與隱性位元: 邏輯電平以電壓狀態表示。主導位元(0)會覆蓋隱性位元(1)。

- 同步: 節點利用同步段與訊框起始位元同步。

- 取樣點: 資料在位元時間的特定百分比處進行取樣,以避免雜訊干擾。

若取樣點過於接近邊緣,雜訊可能導致位元錯誤;若過晚,資料可能尚未穩定。時序圖協助工程師正確設定取樣點,通常位於位元時間的80%左右。

2. 傳感器融合中的ADC取樣

現代車輛使用多個傳感器(雷達、光達、相機)來建立對環境的感知。類比數位轉換器(ADC)必須在精確的間隔內取樣訊號,以避免混疊現象。

- 時鐘抖動: 時鐘邊緣定時的變化會將雜訊引入數位化訊號中。

- 延遲: 從傳感器輸入到處理後資料輸出的時間必須最小化,以實現即時控制。

- 交錯:多個ADC通常並行工作。時序圖確保它們的相位對齊,以防止資料出現間隙。

📱 消費電子:高速介面

消費性裝置優先考慮效能與省電效率。像DDR記憶體與顯示連結之類的介面,需要嚴格的時序窗口,才能在不增加功耗的情況下達到高頻寬。

1. DDR記憶體介面

雙資料速率(DDR)記憶體在時鐘的上升沿與下降沿都傳輸資料。這使有效資料速率加倍,但資料穩定的時間窗口卻減半。

| 參數 | 定義 | 違反的影響 |

|---|---|---|

| 建立時間 | 資料必須在時鐘邊緣前保持穩定的時間 | 資料傳輸遺漏,系統卡頓 |

| 保持時間 | 資料必須在時鐘邊緣後仍保持穩定的時間 | 資料損壞,位元翻轉 |

| 時鐘偏移 | 時鐘到達不同晶片的時間差異 | 時序餘量減少,不穩定 |

| 佔空比 | 高電平時間與總週期的比率 | 效能不平衡,抖動增加 |

在DDR4與DDR5中,指令與位址匯流排通常以低於資料匯流排的頻率運作。時序圖必須考慮隨資料一同傳輸的源同步選通訊號(DQS),以標示有效的時間窗口。

2. 顯示介面(MIPI DSI)

行動裝置使用MIPI顯示序列介面(DSI)將處理器與螢幕連接。此介面使用高速差分通道。

- LP指令模式: 用於傳送指令的低功耗模式,依賴嚴格的時序來進行喚醒序列。

- HS資料模式: 高速傳輸模式,時鐘恢復在資料流上進行。

- 轉換時間: 在同一通道上從傳輸模式切換至接收模式所需的時間。

這些時序圖中的錯位會導致螢幕出現雜訊、閃爍,或完全失去視訊輸出。

📡 電信:延遲與頻寬

在電信領域,時序等同於延遲。封包傳遞時間以及分散式網路中的同步,對於5G和高頻率交易等服務至關重要。

1. PCIe 信號傳輸

Peripheral Component Interconnect Express (PCIe) 標準廣泛用於連接高速元件。它使用內嵌時鐘或源同步時鐘的串列通道。

- 均衡化:訊號完整性會隨著距離增加而劣化。時序圖顯示均衡濾波器如何補償訊號損耗。

- 鏈路訓練: 一連串時序狀態,用於建立鏈路速度和通道寬度。

- 流量控制: 基於信用的流量控制所需的時序窗口可防止緩衝區溢出。

2. 以太網物理層(PHY)

標準以太網依賴共享時鐘或時鐘恢復機制。千兆以太網及更高版本使用8b/10b編碼,以確保足夠的訊號跳變用於時鐘恢復。

- 空閒期間: 定義的時序窗口,在此期間不傳送資料,以維持同步。

- 幀起始定界符: 一種特定的位元模式,標示封包的起始位置,需要精確的檢測時序。

- 封包間隔: 封包之間的強制延遲,以讓硬體有時間重置。

⚠️ 常見的時序違規與解決方案

即使設計謹慎,時序違規仍會發生。識別根本原因需要分析時序圖,以查看信號在何處偏離預期。

1. 建立時間違規

當資料到達過晚,無法被時鐘邊沿捕獲時發生。

- 原因: 邏輯層級過深、導線延遲過長,或時鐘偏移。

- 解決方案:

- 插入流水線寄存器以切斷長路徑。

- 優化邏輯綜合以減少邏輯閘數量。

- 調整時鐘頻率以提供更長的時間。

2. 保持時間違規

當資料在時鐘邊緣後變動過快時發生,會覆蓋已捕獲的值。

- 原因: 短路徑延遲,時鐘偏移導致捕獲時鐘到達過晚。

- 解決方案:

- 在資料路徑中插入延遲緩衝器。

- 使用重定時技術來平衡路徑。

- 確保時鐘分配網路的偏移最小。

3. 時鐘偏移與抖動

偏移是指時鐘信號到達不同暫存器的到達時間差異。抖動是指時鐘邊緣的短時間變化。

- 影響: 降低資料可用的有效時序餘量。

- 解決方案:

- 使用低抖動時鐘產生器。

- 設計具有相等長度走線的平衡時鐘樹。

- 實作鎖相環(PLL)以淨化時鐘信號。

✅ 實作的最佳實務

實現穩健的時序需要在整個設計生命週期中採取系統化的方法。文件記錄與驗證與電路本身同樣重要。

1. 尽早定義時序約束

不要等到實作階段才定義時序需求。在設計規格中記錄時鐘頻率、輸入延遲與輸出延遲。這能確保所有相關人員理解系統的界限。

2. 使用靜態時序分析

靜態時序分析(STA)工具在不模擬每種輸入組合的情況下計算最壞情況的延遲路徑。此方法效率高,涵蓋所有可能狀態,確保不會遺漏任何時序違規。

3. 透過模擬進行驗證

雖然STA功能強大,但動態模擬能提供特定條件下信號行為的視圖。使用模擬來驗證關鍵路徑,特別是涉及非同步邏輯或複雜狀態機的路徑。

4. 物理設計考量

晶片或電路板的物理佈局會直接影響時序。

- 走線長度: 更長的走線會增加電容與電阻,進而增加延遲。

- 串擾: 相鄰信號可能產生雜訊,導致錯誤的轉換。

- 電源雜訊: 電壓下降會降低邏輯閘切換速度。

🛠️ 排除現實世界中的問題情境

當系統無法滿足時序要求時,需要採用結構化的除錯流程。以下步驟概述了解決時序問題的邏輯方法。

- 步驟 1:識別路徑。找出導致失敗的特定寄存器到寄存器路徑。查看時序報告中負值最大的slack。

- 步驟 2:分析波形。使用時序圖形檢視器檢查實際的信號轉換情況,並將其與預期值進行比較。

- 步驟 3:檢查時鐘。確認時鐘信號品質,檢查是否存在抖動、占空比失真或雜訊。

- 步驟 4:檢視約束條件。確保設計檔中的約束條件與硬體的實際物理狀況相符。

- 步驟 5:迭代。對邏輯或佈局進行修改,然後重新執行時序分析。

📊 時序參數摘要

為便於快速參考,以下是各產業常用關鍵時序參數的摘要。

| 參數 | 符號 | 典型單位 | 描述 |

|---|---|---|---|

| 週期 | Tc | ns | 連續時鐘邊緣之間的時間 |

| 頻率 | Fc | Hz | 週期的倒數 |

| 建立時間 | tsu | ns | 時鐘邊緣前所需的資料穩定性 |

| 保持時間 | th | ns | 時鐘邊緣後所需的資料穩定性 |

| 傳播延遲 | tpd | ns | 信號通過邏輯所需時間 |

| 偏移 | Δt | ps | 時鐘到達時間差異 |

🔄 管理異步設計

並非所有系統都運行在單一時鐘下。異步設計涉及資料跨越不同時鐘域。這會帶來亞穩態的風險,即觸發器進入未定義狀態。

- 同步鏈路: 使用多級同步器(通常為兩個觸發器)以確保信號在使用前穩定下來。

- 握手機制: 實施請求-確認機制,以確保資料發送前接收端已準備就緒。

- FIFO緩衝區: 使用先進先出的記憶體結構,以解耦生產者與消費者的速度。

異步設計的時序圖顯示兩個獨立時鐘之間的關係。關鍵在於確保資料路徑有足夠時間穩定,才會被接收時鐘採樣。

🌟 最後的想法

時序圖是數位系統驗證的骨幹。它們彌補了抽象邏輯與物理現實之間的差距。透過理解建立時間、保持時間、時鐘偏移與抖動的細節,工程師能夠設計出穩健、高效且可靠的系統。

無論是在汽車安全系統、消費性電子產品,還是通訊基礎設施中,這些原則都保持不變。時序的精確性帶來性能的精確性。持續監控並遵循最佳實務,可確保設計在其整個生命周期內都能正常運作。隨著技術進步與速度提升,詳細時序分析的重要性將不斷增加。

對於希望提升設計品質的團隊而言,投入時間製作精確的時序圖和驗證流程至關重要。這能降低風險、減少除錯成本,並確保最終產品符合其規格要求。透過適當的工具與方法,時序挑戰將轉化為可管理的限制條件,而非障礙。