Trong thiết kế số hiện đại, việc hiểu rõ luồng tín hiệu theo thời gian là yếu tố then chốt để đảm bảo độ tin cậy của hệ thống. Các hệ thống bất đồng bộ, nơi các thao tác không được điều khiển bởi một đồng hồ toàn cục duy nhất, mang lại những thách thức đặc biệt so với các hệ thống đồng bộ tương ứng. Công cụ chính được sử dụng để trực quan hóa và gỡ lỗi những tương tác phức tạp này là sơ đồ thời gian. Hướng dẫn này cung cấp cái nhìn sâu sắc về cách xây dựng, đọc và phân tích sơ đồ thời gian trong môi trường bất đồng bộ.

Bản chất của thiết kế bất đồng bộ 🌐

Các hệ thống bất đồng bộ hoạt động mà không cần tín hiệu đồng hồ tập trung điều khiển mọi thay đổi trạng thái. Thay vào đó, các sự kiện được kích hoạt bởi việc hoàn thành các thao tác trước đó hoặc khi dữ liệu đến. Cách tiếp cận này mang lại những lợi ích như giảm tiêu thụ điện năng và hiệu suất tiềm năng cao hơn trong một số ngữ cảnh cụ thể. Tuy nhiên, nó cũng tạo ra độ phức tạp liên quan đến đồng bộ hóa tín hiệu và xác minh thời gian.

Khi các kỹ sư phân tích các hệ thống này, họ phải tính đến các độ trễ biến đổi, thời gian lan truyền và sự thiếu vắng điểm tham chiếu phổ quát. Sơ đồ thời gian đóng vai trò như ngôn ngữ trực quan để biểu diễn các sự kiện này. Chúng cho phép các nhóm nhìn thấy mối quan hệ chính xác giữa các chuyển đổi tín hiệu theo thời gian.

Cấu tạo của sơ đồ thời gian 📐

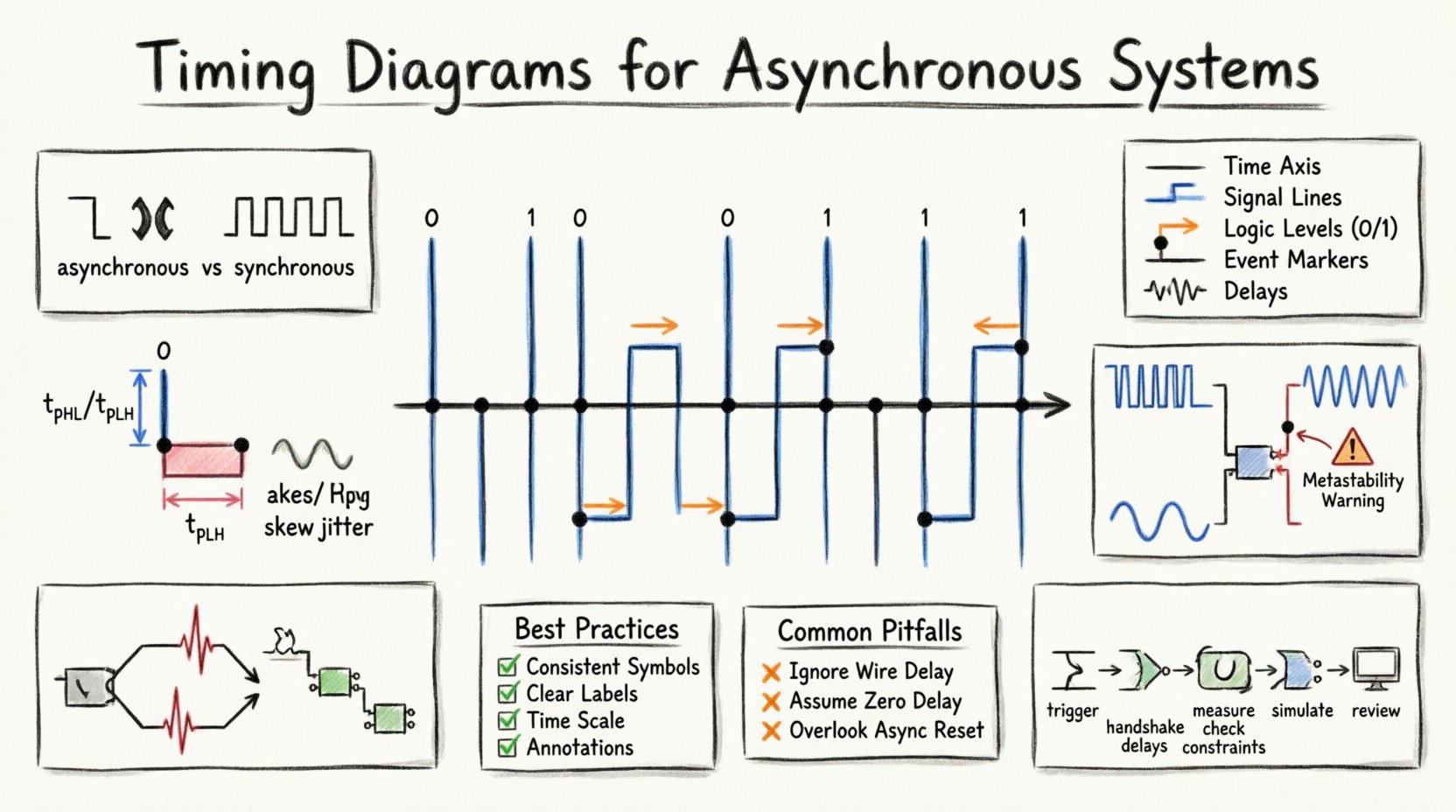

Sơ đồ thời gian là một biểu diễn đồ họa về hành vi tín hiệu. Nó vẽ thời gian theo trục hoành và trạng thái tín hiệu theo trục tung. Để phân tích hiệu quả một hệ thống bất đồng bộ, người ta phải hiểu rõ các thành phần cơ bản tạo nên những sơ đồ này.

- Trục thời gian:Biểu diễn sự tiến triển của thời gian. Trong phân tích bất đồng bộ, trục này thường mang tính tương đối so với một sự kiện kích hoạt cụ thể thay vì một chu kỳ đồng hồ.

- Các đường tín hiệu:Các đường nằm ngang biểu diễn từng dây dẫn hoặc mạng riêng lẻ. Mỗi đường theo dõi mức logic (Cao, Thấp hoặc Không xác định) của một tín hiệu cụ thể.

- Mức logic:Thường được ký hiệu là

0(Thấp/Đất) và1(Cao/VCC). Các chuyển đổi giữa các trạng thái này là trọng tâm của phân tích. - Các dấu hiệu sự kiện:Các đường thẳng đứng hoặc chú thích chỉ ra các sự kiện cụ thể, chẳng hạn như tín hiệu trao đổi trạng thái thay đổi.

- Độ trễ:Khoảng trống trực quan giữa sự thay đổi đầu vào và sự thay đổi đầu ra tương ứng, biểu diễn độ trễ lan truyền.

Khác với các sơ đồ đồng bộ dựa vào các đường lưới biểu diễn các cạnh đồng hồ, sơ đồ bất đồng bộ dựa vào các ranh giới sự kiện. Điều này đòi hỏi sự diễn giải cẩn trọng hơn về khoảng cách giữa các chuyển đổi.

Các tham số thời gian quan trọng ⚙️

Để phân tích độ toàn vẹn của một hệ thống bất đồng bộ, các tham số thời gian cụ thể phải được đo lường và so sánh với các thông số thiết kế. Những tham số này xác định khoảng thời gian mà một tín hiệu phải ổn định để được bộ nhận xử lý chính xác.

Độ trễ lan truyền

Độ trễ lan truyền là thời gian cần thiết để một tín hiệu đi từ đầu vào của một thành phần đến đầu ra của nó. Trong logic bất đồng bộ, độ trễ này là nguồn chính gây ra sự không chắc chắn. Các biến thể trong quá trình sản xuất, nhiệt độ và điện áp có thể làm thay đổi độ trễ này.

- tpHL:Thời gian để một tín hiệu chuyển từ Cao sang Thấp.

- tpLH:Thời gian để một tín hiệu chuyển từ Thấp sang Cao.

- tpd: Thời gian trễ lan truyền chung, thường được tính như trung bình cộng của tpHL và tpLH.

Khi phân tích sơ đồ thời gian, hãy tìm khoảng cách ngang giữa cạnh đầu vào và cạnh đầu ra tương ứng. Khoảng cách này chính là thời gian trễ lan truyền.

Thời gian thiết lập và thời gian giữ

Ngay cả trong các hệ thống bất đồng bộ, các flip-flop và bộ nhớ giữ thường yêu cầu các khoảng thời gian ổn định cụ thể. Thời gian thiết lập là khoảng thời gian trước sự kiện kích hoạt mà dữ liệu phải ổn định. Thời gian giữ là khoảng thời gian sau sự kiện kích hoạt mà dữ liệu phải duy trì ổn định.

Nếu các khoảng thời gian này bị vi phạm, hệ thống có thể rơi vào trạng thái bất ổn, nơi đầu ra không phải là cao cũng không phải là thấp, mà là mức điện áp không xác định. Sơ đồ thời gian giúp trực quan hóa các vi phạm này bằng cách cho thấy dữ liệu thay đổi quá gần với cạnh điều khiển.

Chênh lệch và dao động

- S chênh lệch: Sự khác biệt về thời gian đến của cùng một tín hiệu tại hai điểm khác nhau trong mạch.

- Dao động: Những biến động ngắn hạn trong thời gian tín hiệu. Trong các hệ thống bất đồng bộ, dao động có thể do nhiễu nguồn điện hoặc nhiễu xuyên kênh.

Xử lý việc chuyển giữa các miền đồng hồ 🔄

Một trong những nguồn lỗi phổ biến nhất trong các hệ thống hỗn hợp liên quan đến việc chuyển giữa các miền đồng hồ khác nhau. Ngay cả khi một hệ thống chủ yếu là bất đồng bộ, nó thường chứa các khối con đồng bộ hoạt động ở các tần số khác nhau. Sơ đồ thời gian là công cụ thiết yếu để xác minh các chuyển đổi này.

Khi một tín hiệu di chuyển từ miền đồng hồ này sang miền đồng hồ khác, bộ nhận có thể lấy mẫu tín hiệu vào thời điểm tín hiệu đang thay đổi. Điều này dẫn đến trạng thái bất ổn. Cách tiếp cận tiêu chuẩn để giảm thiểu điều này là sử dụng bộ đồng bộ hóa, thường là một chuỗi các flip-flop.

| Tham số | Mô tả | Ảnh hưởng đến sơ đồ thời gian |

|---|---|---|

| Thời gian giải quyết trạng thái bất ổn | Thời gian cần thiết để bộ đồng bộ hóa đạt đến mức logic hợp lệ | Hiển thị một khoảng thời gian kéo dài ở trạng thái không xác định trước khi tín hiệu ổn định |

| Độ trễ chuyển miền | Độ trễ bổ sung do bộ đồng bộ hóa tạo ra | Làm tăng khoảng thời gian giữa sự kiện nguồn và sự kiện đích |

| Độ trễ tín hiệu xác nhận | Thời gian cần thiết cho các tín hiệu xác nhận trong các giao thức bất đồng bộ | Tạo ra mẫu đi lại-lại trong dòng thời gian tín hiệu |

Các nhà phân tích phải đảm bảo sơ đồ thời gian tính đến thời gian giải quyết. Nếu một khối phía sau cố gắng đọc tín hiệu trước khi bộ đồng bộ hóa hoàn tất giải quyết, dữ liệu sẽ bị lỗi.

Phát hiện và giải quyết các điều kiện cạnh tranh ⚠️

Một điều kiện cạnh tranh xảy ra khi hành vi của hệ thống phụ thuộc vào thứ tự thời gian tương đối của các sự kiện mà lẽ ra không nên ảnh hưởng lẫn nhau. Trong logic bất đồng bộ, đây là một vấn đề thường gặp. Sơ đồ thời gian là phương pháp chính để phát hiện các điều kiện này.

Suy yếu tĩnh

Một nguy cơ tĩnh xảy ra khi một tín hiệu nên duy trì ở mức không đổi nhưng tạm thời đảo ngược do độ trễ đường đi. Ví dụ, nếu một tín hiệu về mặt logic được dự kiến duy trì ở mức cao, nhưng một thay đổi đầu vào gây ra một dao động ngắn đến mức thấp, thì đây là một nguy cơ tĩnh-1.

- Chỉ báo hình ảnh:Một đỉnh nhọn hoặc xung hẹp trên đường tín hiệu mà lẽ ra phải phẳng.

- Nguyên nhân gốc rễ:Độ trễ lan truyền không bằng nhau qua các cổng logic khác nhau.

Nguy cơ động

Nguy cơ động liên quan đến nhiều chuyển trạng thái khi chỉ mong đợi một chuyển trạng thái. Điều này thường xảy ra trong các đường logic phức tạp, nơi các tín hiệu đi qua số lượng cổng khác nhau.

Các bước phân tích điều kiện cạnh tranh

- Theo dõi các đường đi:Xác định tất cả các đường đi mà tín hiệu đi từ nguồn đến đích.

- Đo độ trễ:Tính toán độ trễ cho từng đường đi bằng cách sử dụng sơ đồ thời gian.

- So sánh các cạnh:Kiểm tra xem các thời điểm đến của các tín hiệu cạnh tranh có chồng lấn nhau theo cách tạo ra sự mơ hồ hay không.

- Xác minh độ ổn định:Đảm bảo các tín hiệu điều khiển duy trì ổn định trong khoảng thời gian quan trọng khi dữ liệu đến.

Nếu phát hiện điều kiện cạnh tranh, thiết kế có thể cần được tái cấu trúc. Các giải pháp phổ biến bao gồm thêm bộ đệm để cân bằng độ trễ, chèn giao thức bắt tay, hoặc sử dụng cấu trúc FIFO bất đồng bộ.

Xét đến độ toàn vẹn tín hiệu và nhiễu 🔌

Sơ đồ thời gian không tồn tại trong chân không. Tầng vật lý tạo ra nhiễu ảnh hưởng đến chất lượng tín hiệu. Khi phân tích các hệ thống bất đồng bộ, các kỹ sư phải phân biệt giữa lỗi thời gian logic và suy giảm tín hiệu vật lý.

Sự cố tín hiệu

Các sự cố tín hiệu là những xung ngắn hạn có thể lan truyền qua mạch. Trong các hệ thống bất đồng bộ, một sự cố tín hiệu có thể kích hoạt nhầm một bộ nhớ giữ hoặc flip-flop. Sơ đồ thời gian thường thể hiện chúng dưới dạng các đỉnh mảnh.

- Lọc:Đảm bảo logic đầu ra có đủ độ trễ để lọc bỏ các xung này.

- Tốc độ cạnh:Cạnh dốc hơn (thời gian tăng/giảm nhanh hơn) dễ bị ảnh hưởng bởi sự耦 hợp nhiễu hơn.

Tương tác chéo

Tương tác chéo xảy ra khi một tín hiệu trên dây này cảm ứng điện áp lên dây kề bên. Điều này có thể làm thay đổi thời gian của tín hiệu, khiến nó đến sớm hoặc muộn hơn dự kiến.

Trong sơ đồ thời gian, tương tác chéo có thể thể hiện dưới dạng dịch chuyển vị trí cạnh hoặc một đỉnh nhiễu bổ sung. Để giảm thiểu điều này, khoảng cách giữa các tín hiệu phải được xem xét trong giai đoạn thiết kế vật lý.

Các thực hành tốt nhất cho tài liệu 📝

Tài liệu rõ ràng đảm bảo rằng phân tích thời gian có thể được tái tạo và hiểu được bởi các kỹ sư khác. Một sơ đồ thời gian được cấu trúc tốt bao gồm các thông tin mô tả cụ thể và chú thích.

Tiêu chuẩn hóa

- Sử dụng các ký hiệu nhất quán cho các mức logic.

- Ghi nhãn tất cả các tín hiệu một cách rõ ràng với chức năng của chúng.

- Chỉ rõ thang thời gian một cách rõ ràng (ví dụ: nanosecond mỗi vạch chia).

Ghi chú

Các ghi chú văn bản rất quan trọng để giải thích các hành vi cụ thể. Sử dụng mũi tên để chỉ ra các chuyển tiếp quan trọng hoặc các khu vực tiềm ẩn vấn đề. Ghi nhãn các giá trị trễ lan truyền trực tiếp trên sơ đồ.

Kiểm soát phiên bản

Sơ đồ thời gian thay đổi theo sự thay đổi thiết kế. Duy trì số phiên bản cho tất cả các sơ đồ để đảm bảo phân tích phù hợp với trạng thái phần cứng hiện tại. Không nên dựa vào trí nhớ để ghi nhớ chi tiết thời gian.

Quy trình phân tích từng bước 🛠️

Để phân tích hiệu quả một hệ thống bất đồng bộ, hãy tuân theo một phương pháp có cấu trúc. Điều này đảm bảo rằng không có tham số thời gian quan trọng nào bị bỏ sót.

- Xác định sự kiện kích hoạt:Xác định sự kiện khởi đầu chuỗi. Đây thường là điểm bắt đầu của trục thời gian.

- Bản đồ giao tiếp:Theo dõi các tín hiệu yêu cầu và xác nhận. Đảm bảo chúng tuân theo đúng giao thức (ví dụ: giao tiếp bốn pha hoặc hai pha).

- Đo các độ trễ:Tính toán độ trễ tổng cộng từ sự kiện kích hoạt đến đầu ra cuối cùng. Chia nhỏ thành các độ trễ thành phần.

- Kiểm tra các ràng buộc:Xác minh rằng các thời gian thiết lập và giữ được đáp ứng cho tất cả các phần tử lưu trữ tham gia.

- Mô phỏng các biến thể:Phân tích sơ đồ trong điều kiện xấu nhất, chẳng hạn như nhiệt độ cao nhất hoặc điện áp thấp nhất.

- Xem xét hiện tượng bất ổn:Đảm bảo xác suất xảy ra hiện tượng bất ổn được giảm xuống mức chấp nhận được thông qua các bộ đồng bộ hóa.

Những sai lầm phổ biến trong phân tích thời gian ⚡

Ngay cả các kỹ sư có kinh nghiệm cũng có thể bỏ sót những vấn đề tinh tế. Nhận thức được những sai lầm phổ biến sẽ giúp tránh được việc thiết kế lại tốn kém.

- Bỏ qua độ trễ dây dẫn:Chỉ dựa vào độ trễ cổng trong khi bỏ qua điện trở và điện dung của các đường nối.

- Giả định độ trễ bằng không:Xem các vòng hồi tiếp như tức thời, điều này là không thể về mặt vật lý.

- Bỏ qua tín hiệu reset bất đồng bộ:Không tính đến thời gian của tín hiệu reset so với tín hiệu dữ liệu.

- Nhầm lẫn giữa cạnh và mức:Nhầm lẫn giữa hành vi kích cạnh và hành vi kích mức trong việc diễn giải sơ đồ.

Kết luận về kiểm chứng ✅

Sơ đồ thời gian là công cụ không thể thiếu trong việc kiểm chứng các hệ thống bất đồng bộ. Chúng cung cấp một biểu diễn trực quan cụ thể cho các mối quan hệ thời gian trừu tượng. Bằng cách phân tích nghiêm ngặt các sơ đồ này, các kỹ sư có thể phát hiện các điều kiện cạnh tranh, xác minh các giao thức bắt tay và đảm bảo độ toàn vẹn tín hiệu.

Độ phức tạp của thiết kế bất đồng bộ đòi hỏi sự chính xác. Mỗi nanosecond đều có ý nghĩa. Việc hiểu rõ sâu sắc về độ trễ lan truyền, thời gian thiết lập và thời gian giữ cho phép tạo ra các hệ thống vững chắc. Dù việc thiếu đồng hồ toàn cục làm tăng độ khó, nhưng những hiểu biết thu được từ phân tích thời gian chi tiết dẫn đến các thiết kế hiệu quả và đáng tin cậy hơn.

Việc tiếp tục hoàn thiện các kỹ năng phân tích này đảm bảo rằng hệ thống hoạt động đúng đắn trong các điều kiện môi trường khác nhau. Mục tiêu là sự ổn định và khả năng dự đoán, đạt được thông qua việc ghi chép và đo lường cẩn thận.

Các cân nhắc nâng cao 🔬

Đối với các ứng dụng hiệu suất cao, các yếu tố bổ sung sẽ xuất hiện. Bao gồm các gradient nhiệt độ trên chip và sự sụt áp trong các sự kiện chuyển đổi.

- Gradient nhiệt độ:Các tín hiệu di chuyển từ tâm chip nóng sang mép lạnh sẽ trải qua các tốc độ khác nhau. Sự biến thiên này phải được phản ánh trong phân tích thời gian.

- Tiếng ồn lưới nguồn:Tiếng ồn chuyển đổi đồng thời có thể làm dịch chuyển ngưỡng logic. Sơ đồ thời gian nên lý tưởng là bao gồm biểu diễn về độ ổn định của đường nguồn.

- Độ trễ biến đổi:Một số giao thức bất đồng bộ cho phép độ trễ thay đổi. Sơ đồ thời gian phải thể hiện khoảng độ trễ được chấp nhận, chứ không chỉ một giá trị duy nhất.

Bằng cách tích hợp các cân nhắc nâng cao này, phân tích thời gian trở thành công cụ toàn diện cho việc xác thực hệ thống. Nó vượt ra ngoài kiểm chứng đơn thuần để đạt đến tối ưu hóa hiệu suất thực sự.

Hãy nhớ rằng thời gian không chỉ liên quan đến tốc độ; nó liên quan đến tính chính xác. Một hệ thống nhanh nhưng thất bại do lỗi thời gian sẽ ít hữu ích hơn một hệ thống chậm nhưng hoạt động đáng tin cậy. Sơ đồ thời gian là bản đồ dẫn bạn đến sự đáng tin cậy đó.