Sơ đồ thời gian là nền tảng của thiết kế hệ thống số. Chúng cung cấp một ngôn ngữ trực quan mà các kỹ sư sử dụng để mô tả cách tín hiệu thay đổi theo thời gian. Dù bạn đang thiết kế giao diện vi điều khiển hay gỡ lỗi giao thức truyền thông, việc hiểu rõ các sơ đồ này là điều cần thiết. Hướng dẫn này sẽ dẫn dắt bạn qua quy trình tạo ra và diễn giải chúng mà không cần sự phức tạp không cần thiết.

Bắt đầu có thể khiến bạn cảm thấy lo lắng, nhưng với khung nền phù hợp, bạn có thể vẽ các sơ đồ hiệu quả chỉ trong vài phút. Chúng ta sẽ tìm hiểu các thành phần cốt lõi, logic đằng sau các chuyển đổi tín hiệu, và các tham số then chốt định nghĩa độ tin cậy của hệ thống. Hãy cùng khám phá cơ chế của thời gian tín hiệu.

Hiểu rõ mục đích cốt lõi 🧠

Sơ đồ thời gian là một biểu diễn đồ họa cho trình tự các sự kiện trong hệ thống. Nó biểu diễn trạng thái của các tín hiệu theo một trục thời gian chung. Khác với sơ đồ mạch điện thể hiện các kết nối vật lý, sơ đồ thời gian tập trung vào mối quan hệ theo thời gian. Sự phân biệt này rất quan trọng khi gỡ lỗi các lỗi logic không xuất hiện trong phân tích mạch tĩnh.

Khi bạn vẽ các sơ đồ này, bạn đang ghi lại hành vi của các tín hiệu dữ liệu và điều khiển. Mục tiêu là đảm bảo rằng một tín hiệu đã sẵn sàng trước khi tín hiệu khác tác động lên nó. Sự đồng bộ này ngăn ngừa lỗi dữ liệu và đảm bảo hoạt động ổn định.

-

Rõ ràng về mặt trực quan: Chúng biến các mối quan hệ thời gian trừu tượng thành cụ thể.

-

Công cụ hỗ trợ gỡ lỗi: Chúng làm nổi bật các điều kiện cạnh tranh và vi phạm điều kiện thiết lập.

-

Tài liệu tham khảo: Chúng đóng vai trò là tài liệu tham khảo cho các đội ngũ phần cứng và phần mềm.

-

Kiểm chứng: Chúng giúp xác minh rằng logic hoạt động đúng với yêu cầu kỹ thuật.

Không có sơ đồ rõ ràng, rất dễ bỏ sót những vấn đề về thời gian tinh tế chỉ xảy ra trong điều kiện cụ thể. Bằng cách chuẩn hóa cách bạn vẽ, bạn sẽ giảm thiểu sự mơ hồ cho tất cả những người tham gia dự án.

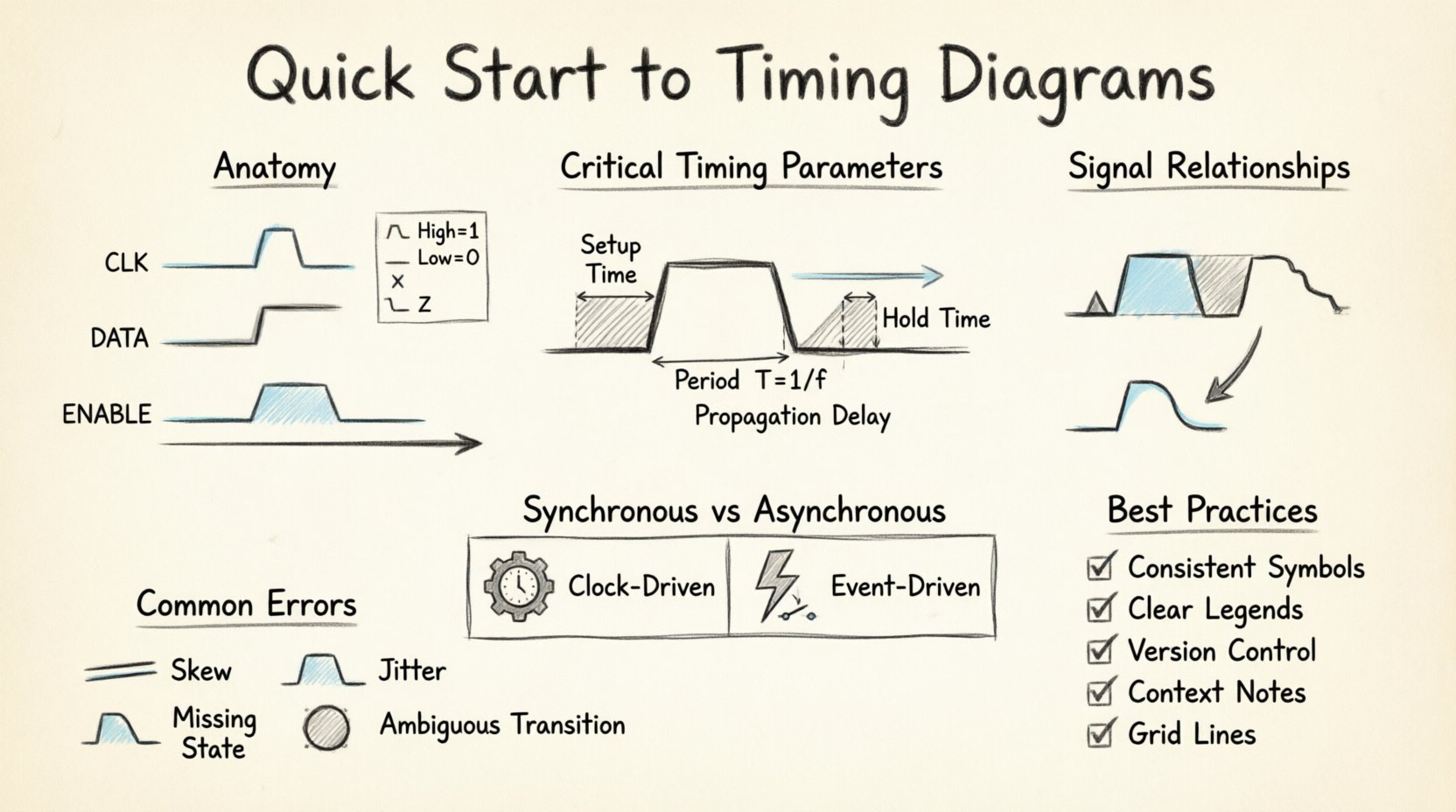

Cấu tạo của sơ đồ thời gian 📐

Mọi sơ đồ thời gian đều có cấu trúc chung. Nắm vững cấu trúc này giúp bạn đọc các sóng phức tạp một cách dễ dàng. Bố cục này được duy trì nhất quán qua nhiều lĩnh vực kỹ thuật, từ hệ thống nhúng đến mạng tốc độ cao.

1. Trục thời gian ⏰

Trục ngang đại diện cho thời gian. Nó chảy từ trái sang phải. Thời gian không phải lúc nào cũng tuyến tính trong mọi ngữ cảnh, nhưng trong phần lớn các sơ đồ tiêu chuẩn, các khoảng cách bằng nhau đại diện cho các khoảng thời gian bằng nhau. Bạn không cần ghi nhãn từng mili giây, nhưng việc đánh dấu các khoảng thời gian quan trọng sẽ giúp định tỷ lệ thông tin.

-

Hướng:Luôn từ trái sang phải.

-

Tỷ lệ:Có thể tuyến tính hoặc logarit tùy theo tần số tín hiệu.

-

Điểm đánh dấu:Sử dụng các đường thẳng đứng để đánh dấu các sự kiện cụ thể như cạnh xung đồng hồ.

2. Các đường tín hiệu 📊

Các tín hiệu được biểu diễn bằng các đường ngang được chồng lên nhau theo chiều dọc. Mỗi đường tương ứng với một dây dẫn hoặc mạng cụ thể trong mạch. Tên tín hiệu thường xuất hiện ở bên trái hoặc bên phải của đường.

-

Nhóm tín hiệu:Các tín hiệu liên quan, chẳng hạn như đường địa chỉ và đường dữ liệu, thường được nhóm lại với nhau.

-

Ghi nhãn:Luôn đánh dấu các tín hiệu một cách rõ ràng để tránh nhầm lẫn giữa các tên tương tự.

-

Thứ tự:Đặt tín hiệu quan trọng nhất ở trên cùng hoặc dưới cùng, tùy theo quy ước.

3. Mức logic 🔋

Các tín hiệu chuyển đổi giữa các trạng thái đã xác định. Trong logic số, các trạng thái này thường là Cao và Thấp, hoặc 1 và 0. Vị trí theo chiều dọc của đường biểu diễn cho biết trạng thái.

|

Trạng thái |

Ký hiệu thông dụng |

Ý nghĩa vật lý |

|---|---|---|

|

Cao |

1, H, VCC |

Ngõ nguồn điện dương |

|

Thấp |

0, L, GND |

Đất hoặc điện áp bằng không |

|

Không xác định |

X |

Trạng thái không xác định |

|

Trở kháng cao |

Z |

Ngắt kết nối hoặc trôi nổi |

Hiểu được các mức này là bước đầu tiên khi đọc sơ đồ. Các chuyển tiếp giữa các mức này chính là nơi diễn ra hành động.

Các tham số thời gian quan trọng ⚙️

Thời gian không chỉ đơn thuần là vẽ các đường thẳng; đó là việc xác định các giới hạn. Một số tham số quy định tín hiệu có thể thay đổi nhanh đến mức nào và khi nào phải ổn định. Những giới hạn này rất quan trọng để đảm bảo hệ thống hoạt động đúng.

1. Thời gian thiết lập ⏳

Thời gian thiết lập là khoảng thời gian tối thiểu mà tín hiệu dữ liệu phải ổn định trước khi cạnh đồng hồ đến. Nếu dữ liệu thay đổi quá gần cạnh đồng hồ, hệ thống có thể ghi nhận giá trị sai. Đây là một giới hạn quan trọng trong các hệ thống đồng bộ.

-

Định nghĩa:Thời gian trước cạnh đồng hồ hoạt động.

-

Vi phạm:Gây ra trạng thái bất ổn hoặc ghi nhận dữ liệu sai.

-

Quy tắc thiết kế: Đảm bảo dữ liệu ổn định trước khi đồng hồ kích hoạt.

2. Thời gian giữ ⏳

Thời gian giữ là khoảng thời gian tối thiểu mà tín hiệu dữ liệu phải duy trì ổn định sau cạnh kích hoạt của đồng hồ. Nếu tín hiệu thay đổi quá sớm sau khi kích hoạt, thành phần nhận có thể không ghi giữ giá trị đúng.

-

Định nghĩa:Thời gian sau cạnh kích hoạt của đồng hồ.

-

Vi phạm:Giống như thời gian thiết lập, dẫn đến lỗi dữ liệu.

-

Quy tắc thiết kế:Đảm bảo tín hiệu không chuyển đổi ngay sau khi đồng hồ.

3. Thời gian lan truyền ⏱️

Thời gian lan truyền là khoảng thời gian để tín hiệu đi từ đầu vào của một thành phần đến đầu ra. Không có thành phần điện tử nào là tức thì. Khoảng trễ này tích lũy qua nhiều giai đoạn và phải được tính đến trong các thiết kế tốc độ cao.

-

Nguyên nhân:Thời gian trễ bên trong cổng và độ dài dây dẫn.

-

Tác động:Hạn chế tần số hoạt động tối đa.

-

Đo lường:Đo từ điểm 50% đầu vào đến điểm 50% đầu ra.

4. Chu kỳ và tần số 🔁

Đối với tín hiệu đồng hồ, chu kỳ là khoảng thời gian giữa hai điểm giống nhau liên tiếp trên dạng sóng (ví dụ: cạnh lên đến cạnh lên). Tần số là nghịch đảo của chu kỳ.

-

Chu kỳ: T = 1 / f

-

Chu kỳ làm việc:Phần trăm thời gian tín hiệu ở mức cao trong một chu kỳ.

-

Độ ổn định:Sự dao động đồng hồ ảnh hưởng đến độ chính xác của thời gian.

Đọc và phân tích mối quan hệ giữa các tín hiệu 🔄

Một khi bạn hiểu được các thành phần, bước tiếp theo là phân tích cách các tín hiệu tương tác với nhau. Đây là lúc sơ đồ trở thành công cụ chẩn đoán. Bạn tìm kiếm các mối phụ thuộc và xung đột tiềm ẩn.

1. Kích hoạt theo cạnh 📉

Hầu hết các mạch số kích hoạt theo các cạnh cụ thể của đồng hồ. Một số kích hoạt theo cạnh lên, trong khi những cái khác sử dụng cạnh xuống. Bạn phải xác định cạnh nào là hoạt động cho từng thành phần trong hệ thống của mình.

-

Cạnh lên:Chuyển đổi từ thấp sang cao.

-

Cạnh xuống:Chuyển đổi từ cao sang thấp.

-

Cả hai cạnh:Một số hệ thống lấy mẫu dữ liệu ở cả hai chuyển tiếp.

Khi vẽ, hãy dùng các tam giác nhỏ hoặc các vết khía để chỉ ra cạnh nào đang hoạt động. Điều này giúp tránh nhầm lẫn trong quá trình triển khai.

2. Khoảng thời gian dữ liệu hợp lệ 🕒

Dữ liệu chỉ hợp lệ trong một khoảng thời gian cụ thể. Trước thời gian thiết lập, và sau thời gian giữ, đường dữ liệu phải không thay đổi. Ngoài khoảng thời gian này, dữ liệu được coi là hợp lệ. Ghi chú khoảng thời gian này trên sơ đồ của bạn sẽ làm rõ các kỳ vọng.

-

Khoảng thời gian:Được xác định bởi Thời gian thiết lập + Thời gian giữ + Thời gian lan truyền.

-

Vi phạm:Nếu dữ liệu thay đổi ngoài khoảng thời gian này, sẽ xảy ra lỗi.

-

Dấu hiệu trực quan:Sử dụng các vùng được tô màu để làm nổi bật các khoảng thời gian dữ liệu hợp lệ.

3. Tín hiệu bất đồng bộ 📡

Không phải tất cả các tín hiệu đều tuân theo đồng hồ. Các tín hiệu bất đồng bộ như ngắt hoặc khởi động lại hoạt động độc lập. Chúng đòi hỏi cách xử lý cẩn thận trong sơ đồ thời gian để thể hiện ưu tiên và độ trễ của chúng.

-

Ưu tiên:Các tín hiệu ngắt thường được ưu tiên hơn các chu kỳ đồng hồ.

-

Độ trễ:Lưu ý khoảng thời gian trễ giữa việc phát tín hiệu và phản hồi.

-

Tính ổn định:Đảm bảo các tín hiệu bất đồng bộ ổn định để đáp ứng yêu cầu thiết lập/giữ.

Hệ thống đồng bộ so với hệ thống bất đồng bộ 📡

Sự khác biệt giữa thiết kế đồng bộ và bất đồng bộ ảnh hưởng đến cách bạn xây dựng sơ đồ của mình. Mỗi phương pháp đều có những quy tắc và quy ước riêng.

|

Tính năng |

Đồng bộ |

Bất đồng bộ |

|---|---|---|

|

Điều khiển |

Được điều khiển bởi đồng hồ |

Được điều khiển bởi sự kiện |

|

Dự đoán |

Dễ dự đoán thời gian |

Khó dự đoán thời gian hơn |

|

Độ phức tạp |

Logic chuẩn hóa |

Các giao thức trao đổi |

|

Công suất |

Cao hơn do đồng hồ |

Thường thấp hơn |

Trong sơ đồ đồng bộ, bạn sẽ thấy một đường đồng hồ chính điều chỉnh tất cả các tín hiệu khác. Trong sơ đồ bất đồng bộ, bạn sẽ thấy các thao tác trao đổi và các trạng thái chờ. Cả hai đều yêu cầu tài liệu thời gian chính xác.

Những lỗi phổ biến và cách tránh chúng ⚠️

Những sai sót trong sơ đồ thời gian có thể dẫn đến việc sửa đổi phần cứng tốn kém. Nhận thức được những điểm nguy hiểm phổ biến sẽ giúp bạn vẽ ra các biểu diễn sạch sẽ và chính xác hơn.

1. Bỏ qua độ lệch 📏

Độ lệch là sự khác biệt về thời gian đến của một tín hiệu tại các điểm khác nhau. Nếu bạn giả định tất cả các tín hiệu đến đồng thời, bạn có thể bỏ lỡ các vi phạm thời gian. Luôn tính đến sự khác biệt về chiều dài dây dẫn và tải.

-

Kiểm tra:So sánh thời gian đến tại các bộ nhận khác nhau.

-

Sửa chữa:Thêm bộ đệm trễ hoặc điều chỉnh chiều dài đường dẫn.

-

Trực quan:Hiện các độ lệch nhỏ trên các đường song song nếu độ lệch đáng kể.

2. Bỏ qua độ nhảy ⚡

Độ nhảy là sự biến thiên về thời gian của một tín hiệu. Đồng hồ có thể không hoàn toàn tuần hoàn. Trong các thiết kế tốc độ cao, độ nhảy có thể làm giảm khoảng trống thời gian của bạn. Biểu diễn độ nhảy bằng một vùng được tô màu xung quanh cạnh đồng hồ.

-

Nguyên nhân:Tiếng ồn nguồn cấp điện hoặc nhiễu bên ngoài.

-

Tác động:Làm giảm thời gian thiết lập và giữ hiệu quả.

-

Trực quan:Sử dụng các đường mờ hoặc dải để chỉ sự không chắc chắn.

3. Chuyển tiếp mơ hồ 🔄

Một chuyển tiếp trông như một đường thẳng thực ra có thể là một độ dốc. Các tín hiệu thực tế không thay đổi tức thì. Vẽ các đường thẳng đứng hoàn hảo ngụ ý tốc độ vô hạn, điều này là không thể về mặt vật lý.

-

Thực hành tốt nhất:Vẽ các chuyển tiếp với một độ dốc nhẹ nếu cần độ chính xác.

-

Thỏa thuận:Các đường thẳng đứng là chấp nhận được để biểu diễn logic.

-

Rõ ràng:Đảm bảo mục đích rõ ràng bất kể độ dốc.

4. Thiếu các chuyển tiếp trạng thái 🚦

Các máy trạng thái phức tạp thường có các trạng thái trung gian không rõ ràng. Nếu bạn chỉ vẽ các trạng thái bắt đầu và kết thúc, bạn sẽ mất thông tin quan trọng về thứ tự.

-

Chi tiết:Hiển thị tất cả các thay đổi trạng thái liên quan.

-

Nhãn:Ghi chú các trạng thái bằng tên hoặc giá trị của chúng.

-

Lôgic:Đảm bảo sơ đồ phản ánh đúng luồng lôgic thực tế.

Các thực hành tốt nhất cho tài liệu 📝

Để đảm bảo sơ đồ của bạn hữu ích trong nhiều năm, hãy tuân theo một phong cách nhất quán. Điều này giúp chúng dễ bảo trì và chia sẻ với các kỹ sư khác.

-

Ký hiệu nhất quán:Sử dụng cùng loại đầu mũi tên và kiểu đường nét trên toàn bộ sơ đồ.

-

Chú thích rõ ràng:Xác định bất kỳ ký hiệu hoặc chữ viết tắt tùy chỉnh nào được sử dụng.

-

Kiểm soát phiên bản:Gán nhãn sơ đồ bằng số phiên bản và ngày tháng.

-

Bối cảnh:Bao gồm mô tả ngắn gọn về hệ thống đang được minh họa.

-

Đường lưới:Sử dụng lưới để hỗ trợ căn chỉnh tín hiệu và đánh dấu các khoảng thời gian.

Tính nhất quán giảm tải nhận thức cho bất kỳ ai đọc công việc của bạn. Nó cũng giúp dễ dàng phát hiện các bất thường khi bạn xem lại sơ đồ sau này.

Chẩn đoán sự cố bằng phân tích thời gian 🛠️

Khi một hệ thống thất bại, sơ đồ thời gian thường là nơi đầu tiên cần kiểm tra. Chúng giúp xác định xem vấn đề là logic hay về thời gian.

1. Xác định các điều kiện cạnh tranh 🏁

Một điều kiện cạnh tranh xảy ra khi đầu ra phụ thuộc vào thứ tự các sự kiện. Nếu hai tín hiệu đến cùng lúc tại một cổng, kết quả có thể không thể dự đoán được. Các sơ đồ thời gian tiết lộ những sự chồng lấn này.

-

Nhìn vào:Các tín hiệu giao nhau đồng thời.

-

Giải pháp:Thêm bộ đệm hoặc sắp xếp lại logic.

-

Phòng ngừa:Thiết kế với khoảng trống để tránh các chuyển đổi đồng thời.

2. Phát hiện các xung nhảy ⚡

Các xung nhảy là những xung ngắn xảy ra do độ trễ lan truyền. Chúng có thể kích hoạt một flip-flop một cách vô ý. Trên sơ đồ, chúng xuất hiện như những đỉnh nhọn hẹp giữa các mức ổn định.

-

Trực quan:Những xung hẹp không khớp với chu kỳ đồng hồ.

-

Sửa chữa:Sử dụng bộ lọc hoặc khóa tín hiệu ở cạnh ổn định.

-

Phân tích:Kiểm tra xem độ rộng xung có vượt quá thời gian giữ hay không.

3. Xác minh các giao thức Bus 📡

Các bus như I2C hoặc SPI có yêu cầu về thời gian nghiêm ngặt. Các điều kiện bắt đầu và kết thúc, kéo dài đồng hồ, và dịch chuyển dữ liệu phải được đồng bộ hoàn hảo. Các sơ đồ thời gian là cách chuẩn để xác minh các giao thức này.

-

Bắt đầu/Kết thúc:Xác minh sự chuyển đổi đúng trên đường dữ liệu so với đồng hồ.

-

Kéo dài:Đảm bảo thiết bị phụ có thể giữ đồng hồ ở mức thấp trong khoảng thời gian yêu cầu.

-

Dữ liệu:Xác nhận dữ liệu ổn định trong giai đoạn đồng hồ ở mức cao.

Suy nghĩ cuối cùng về độ toàn vẹn tín hiệu 🎯

Việc tạo ra các sơ đồ thời gian chính xác là một kỹ năng được cải thiện qua thực hành. Nó đòi hỏi sự hiểu biết sâu sắc về cách các linh kiện điện tử hoạt động theo thời gian. Bằng cách tuân theo các hướng dẫn trên, bạn có thể tạo ra các sơ đồ vừa cung cấp thông tin vừa đáng tin cậy.

Hãy nhớ rằng các sơ đồ này là công cụ giao tiếp. Chúng tạo nên cầu nối giữa lý thuyết và thực thi. Khi bạn vẽ một sơ đồ thời gian, bạn đang kể một câu chuyện về cách hệ thống hoạt động. Hãy làm cho câu chuyện đó rõ ràng, chính xác và nhất quán.

Tập trung vào các tham số thiết yếu: thời gian thiết lập, thời gian giữ, độ trễ và độ lệch. Giữ bố cục sạch sẽ và nhãn rõ ràng. Với những thói quen này, bạn sẽ thấy việc vẽ sơ đồ thời gian trở thành một phần tự nhiên trong quy trình thiết kế của mình, giúp bạn hoàn thành trong vài phút thay vì vài giờ.