Các hệ thống số phụ thuộc vào sự đồng bộ chính xác để hoạt động đúng. Khi các tín hiệu đến vào thời điểm sai, các lỗi logic xảy ra, dẫn đến hành vi không thể dự đoán được. Hiểu cách phân tích và khắc phục những vấn đề này là điều cần thiết đối với bất kỳ ai học về logic số, kỹ thuật máy tính hay điện tử. Hướng dẫn này bao gồm các khái niệm cốt lõi và các bước thực tế để xác định và giải quyết các vấn đề về thời gian gặp phải trong mạch tuần tự và truyền dữ liệu.

Hiểu về tín hiệu đồng hồ và các cạnh ⏱️

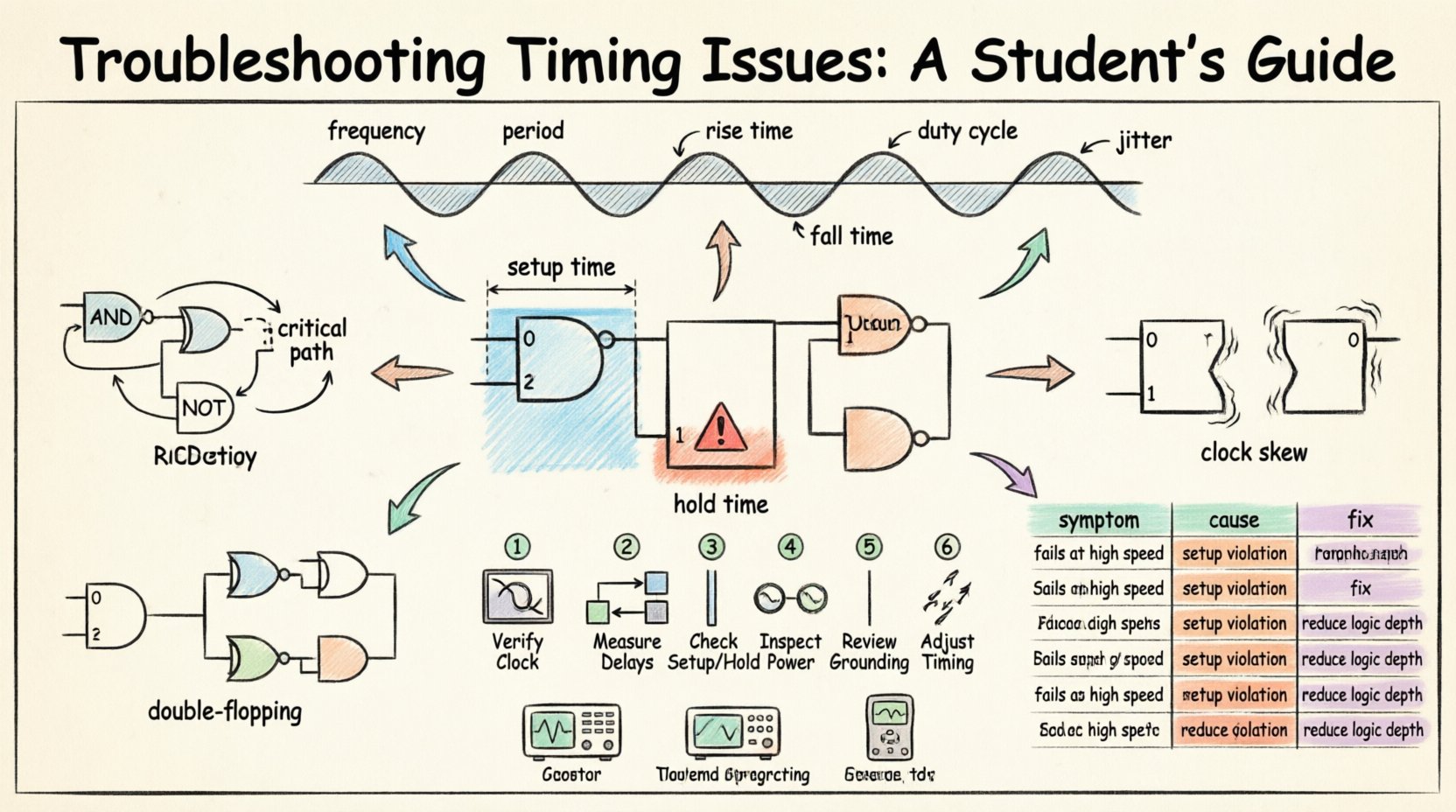

Ở trung tâm của hầu hết các thiết kế số là tín hiệu đồng hồ. Sóng hình sin chu kỳ này xác định thời điểm dữ liệu được lấy mẫu và thời điểm trạng thái thay đổi. Việc khắc phục sự cố thường bắt đầu bằng việc xác minh độ toàn vẹn của tín hiệu cơ bản này.

- Tần số và Chu kỳ: Tần số đồng hồ xác định tốc độ hoạt động. Chu kỳ là khoảng thời gian của một chu kỳ hoàn chỉnh. Nếu mạch yêu cầu đồng hồ 100 MHz, chu kỳ là 10 nanosecond. Bất kỳ sự lệch nào ở đây đều ảnh hưởng đến toàn bộ logic phía sau.

- Thời gian tăng và giảm: Sóng vuông hoàn hảo là lý thuyết. Các tín hiệu thực tế có thời gian tăng và giảm hữu hạn. Nếu quá trình chuyển đổi quá chậm, tín hiệu có thể dành quá nhiều thời gian trong vùng điện áp không xác định, gây ra nhiều lần chuyển đổi hoặc lỗi logic.

- Chu kỳ làm việc: Đây là tỷ lệ thời gian tín hiệu ở mức cao so với tổng chu kỳ. Chu kỳ làm việc 50% là tiêu chuẩn, nhưng một số thiết kế yêu cầu chu kỳ không đối xứng. Những lệch này có thể làm lệch khoảng thời gian cho phép về điều kiện thiết lập hoặc giữ.

Khi kiểm tra một mạch, hãy dùng máy hiện sóng hoặc bộ phân tích logic để quan sát dạng sóng đồng hồ. Hãy tìm các đỉnh nhiễu, hiện tượng cộng hưởng hoặc độ jitter quá lớn. Jitter là sự lệch của cạnh đồng hồ so với vị trí lý tưởng theo thời gian. Jitter cao làm giảm khoảng thời gian hiệu dụng cho dữ liệu ổn định.

Vi phạm thời gian thiết lập và thời gian giữ ⚠️

Đây là những vi phạm về thời gian phổ biến nhất gặp phải trong thiết kế logic tuần tự. Các flip-flop và latch có yêu cầu cụ thể về thời điểm dữ liệu phải ổn định so với cạnh đồng hồ.

Thời gian thiết lập

Thời gian thiết lập là khoảng thời gian tối thiểu trước cạnh đồng hồ mà dữ liệu phải ổn định. Nếu dữ liệu thay đổi quá gần cạnh đồng hồ, flip-flop có thể không ghi nhận được giá trị đúng.

- Điều kiện: Thời gian trễ lan truyền của logic tổ hợp cấp nguồn cho flip-flop phải nhỏ hơn chu kỳ đồng hồ trừ đi thời gian thiết lập.

- Triệu chứng: Hệ thống có thể hoạt động ở tần số thấp nhưng sẽ thất bại khi tốc độ tăng. Các lỗi bit ngẫu nhiên thường xảy ra ở đầu ra.

- Giải pháp: Giảm độ sâu logic giữa các thanh ghi, tăng chu kỳ đồng hồ hoặc sử dụng các thành phần nhanh hơn.

Thời gian giữ

Thời gian giữ là khoảng thời gian tối thiểu sau cạnh đồng hồ mà dữ liệu phải duy trì ổn định. Nếu dữ liệu thay đổi quá sớm sau cạnh đồng hồ, flip-flop có thể mất giá trị đã ghi nhận.

- Điều kiện: Thời gian trễ lan truyền của logic tổ hợp phải lớn hơn thời gian giữ của flip-flop đích.

- Triệu chứng: Các vi phạm về giữ thường xảy ra bất kể tần số. Điều này là do độ trễ là tuyệt đối, không phụ thuộc vào chu kỳ.

- Giải pháp: Thêm các bộ đệm trễ vào đường truyền dữ liệu để làm chậm tín hiệu, hoặc thiết kế lại logic để giảm độ trễ.

Rất quan trọng phải phân biệt hai điều này. Các vi phạm về thiết lập phụ thuộc vào tần số, trong khi các vi phạm về giữ phụ thuộc vào đường đi. Một sai lầm phổ biến là cố gắng khắc phục vi phạm giữ bằng cách làm chậm đồng hồ; điều này sẽ không hiệu quả và có thể làm tình trạng tồi tệ hơn.

Thời gian trễ lan truyền và phân tích đường đi 📉

Tín hiệu không di chuyển tức thì. Mỗi dây dẫn, cổng và thành phần đều tạo ra một độ trễ. Phân tích những độ trễ này là điều cần thiết để đảm bảo dữ liệu đến đúng thời điểm.

- Độ trễ logic tổ hợp: Đây là khoảng thời gian để tín hiệu đi qua các cổng như AND, OR và NOT. Những chuỗi cổng dài tạo ra độ trễ đáng kể.

- Độ trễ kết nối: Trên bảng mạch vật lý, dây dẫn có điện dung và điện trở. Những đường dẫn dài hơn sẽ tạo ra độ trễ lớn hơn. Điều này thường được mô hình hóa dưới dạng mạng RC.

- Độ trễ chân đến chân: Khoảng thời gian từ đầu vào đồng hồ đến đầu ra dữ liệu trong một thành phần. Điều này thường được nêu rõ trong sổ tay dữ liệu.

Khi khắc phục sự cố, hãy xác định đường đi quan trọng. Đây là đường đi có độ trễ lớn nhất giữa hai phần tử tuần tự. Nếu đường đi quan trọng vượt quá chu kỳ đồng hồ, thiết kế sẽ thất bại. Để tìm ra nó, hãy tính tổng độ trễ cho tất cả các đường đi khả dĩ và xác định giá trị lớn nhất.

Sự lệch đồng hồ và độ nhảy đồng hồ 📶

Ngay cả khi nguồn đồng hồ hoàn hảo, tín hiệu có thể đến các thành phần khác nhau vào những thời điểm khác nhau. Hiện tượng này được gọi là sự lệch đồng hồ.

- Sự lệch đồng hồ: Hiện tượng này xảy ra khi tín hiệu đồng hồ đi những quãng đường khác nhau để đến các flip-flop khác nhau. Lệch dương làm trễ đồng hồ thu nhận, làm giảm thời gian thiết lập nhưng làm chặt thời gian giữ. Lệch âm làm chặt thời gian thiết lập nhưng làm lỏng thời gian giữ.

- Độ nhảy đồng hồ: Những biến động ngắn hạn trong thời điểm cạnh đồng hồ. Độ nhảy làm giảm ngân sách thời gian sẵn có cho việc thiết lập dữ liệu.

- Sự trôi: Những thay đổi chậm trong tần số đồng hồ theo thời gian do biến động nhiệt độ hoặc nguồn cung cấp điện.

Sự lệch thường được quản lý bằng kỹ thuật tổng hợp cây đồng hồ trong các thiết kế phức tạp. Trong các dự án sinh viên, nó thường được giảm thiểu bằng cách bố trí các đường dẫn đồng hồ đều đặn và giữ chúng ngắn. Nếu nghi ngờ có sự lệch, hãy đo đồng hồ tại nhiều điểm trong mạch đồng thời.

Tình trạng bất ổn và đầu vào bất đồng bộ 🌀

Khi dữ liệu thay đổi cùng lúc với cạnh đồng hồ, một flip-flop sẽ rơi vào trạng thái bất ổn. Nó không ngay lập tức ổn định về 0 hay 1 mà lơ lửng ở mức điện áp trung gian.

- Rủi ro:Tình trạng bất ổn có thể lan truyền qua hệ thống, gây ra lỗi logic rất khó tái hiện.

- Tín hiệu bất đồng bộ:Các đầu vào từ công tắc bên ngoài hoặc cổng giao tiếp thường không đồng bộ với đồng hồ nội bộ. Những tín hiệu này phải được đồng bộ hóa.

- Đồng bộ hóa kép: Một kỹ thuật phổ biến để giải quyết tình trạng bất ổn là đưa tín hiệu qua hai flip-flop nối tiếp. Flip-flop đầu tiên ghi nhận trạng thái bất ổn, và flip-flop thứ hai xử lý nó trong chu kỳ tiếp theo.

Luôn coi các đầu vào bất đồng bộ là nguồn tiềm ẩn của tình trạng bất ổn. Không kết nối chúng trực tiếp với logic yêu cầu thời gian nghiêm ngặt. Sử dụng mạch đồng bộ hóa để đảm bảo chuyển dữ liệu an toàn giữa các miền đồng hồ khác nhau.

Một quy trình khắc phục sự cố từng bước 🛠️

Khi xảy ra vấn đề về thời gian, hãy tuân theo một phương pháp có cấu trúc để xác định nguyên nhân. Những thay đổi ngẫu nhiên khó có thể mang lại kết quả.

- Xác minh đồng hồ: Kiểm tra tần số, chu kỳ làm việc và biên độ. Đảm bảo tín hiệu ổn định và sạch.

- Đo độ trễ:Sử dụng bộ phân tích logic để thu tín hiệu đầu vào và đầu ra. Đo độ trễ lan truyền thực tế của đường dẫn.

- Kiểm tra điều kiện thiết lập và giữ:Tính toán xem đường dẫn có đáp ứng các ràng buộc thiết lập và giữ hay không dựa trên độ trễ đã đo.

- Kiểm tra nguồn điện:Sụt áp có thể làm chậm các cổng. Đảm bảo nguồn cung cấp ổn định và cung cấp đủ dòng điện.

- Xem xét nối đất:Nối đất kém có thể gây ra nhiễu giống như lỗi thời gian. Kiểm tra các vòng nối đất và các đường trả về chung.

- Điều chỉnh thời gian:Nếu thiết kế linh hoạt, điều chỉnh tần số đồng hồ hoặc thêm bộ đệm để cân bằng đường dẫn.

Tài liệu là yếu tố then chốt trong quá trình này. Ghi lại các dạng sóng và các phép đo. Dữ liệu này giúp so sánh hành vi mong đợi với hiệu suất thực tế.

Bảng tham khảo các lỗi phổ biến 📊

Sử dụng bảng này như một tham chiếu nhanh để chẩn đoán các triệu chứng cụ thể.

| Triệu chứng quan sát được | Nguyên nhân khả dĩ | Hành động được đề xuất |

|---|---|---|

| Hệ thống thất bại ở tốc độ cao | Vi phạm thời gian thiết lập | Giảm độ sâu logic hoặc tăng chu kỳ đồng hồ |

| Hệ thống thất bại ở tốc độ thấp | Vi phạm thời gian giữ | Thêm bộ đệm trễ vào đường dẫn dữ liệu |

| Các bit bị đảo ngẫu nhiên | Nhiễu tín hiệu hoặc độ lệch thời gian | Kiểm tra khả năng che chắn và độ ổn định nguồn cung cấp |

| Đầu ra bị treo hoặc khởi động lại | Tình trạng bất ổn | Thực hiện chuỗi bộ đồng bộ hóa |

| Hành vi không nhất quán | Chênh lệch đồng hồ | Cân bằng độ dài các đường dẫn tín hiệu đồng hồ |

| Không có đầu ra gì cả | Đồng hồ chưa được kích hoạt | Xác minh tín hiệu phân phối đồng hồ và tín hiệu kích hoạt |

Công cụ và thiết bị đo lường 📏

Mặc dù công cụ mô phỏng hữu ích, nhưng xác minh thực tế thường đòi hỏi phần cứng cụ thể. Hiểu cách sử dụng đúng các thiết bị này là một phần trong kỹ năng chẩn đoán sự cố.

- Dao động ký:Cần thiết để quan sát mức điện áp và hình dạng tín hiệu. Sử dụng đầu dò trở kháng cao để tránh tải mạch.

- Bộ phân tích logic:Phù hợp hơn với tín hiệu số. Nó ghi lại trạng thái logic (0 hoặc 1) theo thời gian. Có thể kích hoạt theo các mẫu cụ thể để cô lập lỗi.

- Bộ đếm tần số:Dùng để xác minh tần số chính xác của nguồn đồng hồ khi không có dao động ký.

Đảm bảo đầu dò được điều chỉnh đúng. Một đầu dò không được điều chỉnh có thể làm méo tín hiệu, dẫn đến kết luận sai về thời gian tăng và độ trễ.

Những cân nhắc cuối cùng về độ toàn vẹn tín hiệu 🔒

Vấn đề về thời gian thường là biểu hiện của các vấn đề về độ toàn vẹn tín hiệu rộng hơn. Khi mạch trở nên nhanh hơn, các đặc tính vật lý của bo mạch trở nên quan trọng hơn.

- Tương tác chéo:Tín hiệu trên các dây dẫn kề nhau có thể can thiệp lẫn nhau. Giữ các đường dẫn tốc độ cao cách xa các đường dẫn nhạy cảm.

- Phù hợp trở kháng:Nếu trở kháng đường dẫn không khớp với bộ phát hoặc bộ nhận, sẽ xảy ra hiện tượng phản xạ. Những phản xạ này có thể trông giống như độ trễ thời gian.

- Tác động nhiệt: Khi các linh kiện nóng lên, đặc tính điện của chúng thay đổi. Điều này có thể làm thay đổi độ trễ lan truyền và dẫn đến lỗi thời gian khi chịu tải.

Thiết kế về thời gian đòi hỏi cái nhìn toàn diện. Đó không chỉ là về cổng logic; mà còn là về môi trường vật lý mà tín hiệu đi qua. Bằng cách tuân thủ các nguyên tắc này, sinh viên có thể xây dựng các hệ thống vững chắc hoạt động ổn định trong nhiều điều kiện khác nhau.

Thực hành thường xuyên với phần cứng thực tế giúp thấm nhuần những khái niệm này. Lý thuyết cung cấp khung nền, nhưng việc chẩn đoán sự cố thực tế xây dựng trực giác cần thiết để giải quyết hiệu quả các vấn đề thời gian phức tạp.