Zeitdiagramme sind die Grundlage der Verifizierung digitaler Systeme. Sie übersetzen abstrakte Logik in visuelle Zeitlinien, auf die Ingenieure, Designer und Tester angewiesen sind, um das Verhalten von Signalen zu validieren. Wenn ein Zeitdiagramm Fehler enthält, haben die Konsequenzen weit über die Zeichenfläche hinaus. Falsche Zeitannahmen können zu Hardware-Fehlern, Datenkorruption oder Systeminstabilität in Produktionsumgebungen führen. Dieser Leitfaden untersucht die häufigsten Fallstricke bei der Zeitanalyse und liefert konkrete Strategien, um Genauigkeit zu gewährleisten.

Die Erstellung eines präzisen Zeitdiagramms erfordert mehr als nur das Zeichnen von Linien. Es erfordert ein tiefes Verständnis von Taktdomänen, Signalverbreitung und physischen Beschränkungen. Ingenieure eilen oft durch die Visualisierungsphase und übersehen subtile Details, die sich bei der Implementierung als entscheidend erweisen. Indem man diese häufigen Fehler früh erkennt, können Teams erhebliche Zeit während der Debugging- und Integrationsphasen sparen. Betrachten wir nun die spezifischen Bereiche, in denen Fehler typischerweise auftreten.

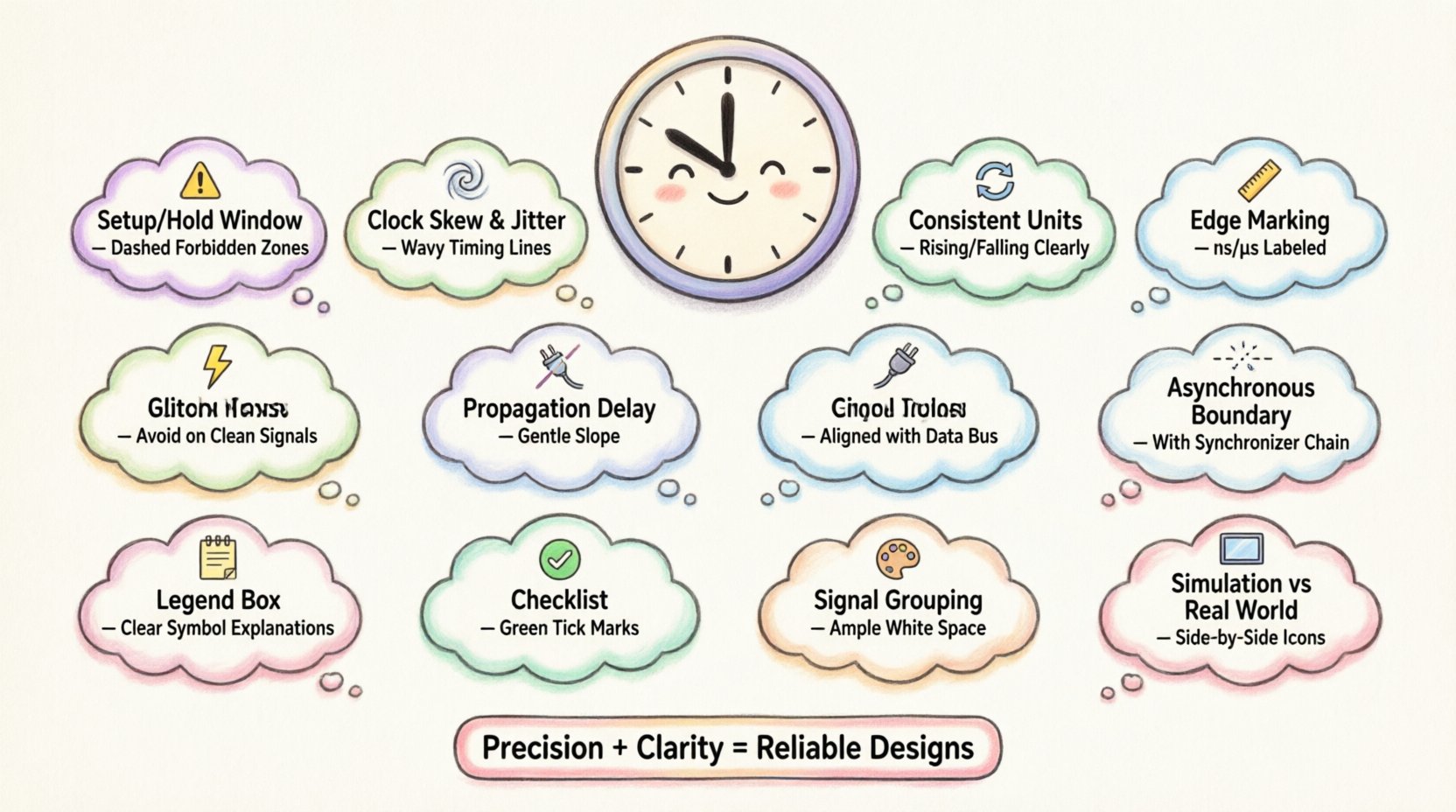

1. Falsche Deutung von Setup- und Hold-Zeit-Verletzungen ⚠️

Setup- und Hold-Zeiten sind grundlegende Beschränkungen in der synchronen digitalen Schaltungstechnik. Eine Setup-Verletzung tritt auf, wenn Daten zu spät vor dem aktiven Taktflankensignal eintreffen. Eine Hold-Verletzung tritt auf, wenn Daten zu früh nach der Taktflanke wechseln. Diese Begriffe sind keine rein theoretischen Konzepte, sondern repräsentieren physikalische Grenzen von Flip-Flops und Logikgattern.

Viele Diagramme geben die Gültigkeitszeitraum für Datensignale nicht eindeutig an. Beim Zeichnen dieser Signale lassen Ingenieure manchmal die kritischen Setup- und Hold-Zeiträume weg, was bei der Überprüfung zu Unklarheiten führt. Ein robustes Diagramm sollte diese Zeiträume explizit im Verhältnis zur Taktflanke markieren.

- Häufiger Fehler:Zeichnen von Datentransitionen, die genau an der Taktflanke ausgerichtet sind, ohne Berücksichtigung von Jitter oder Skew.

- Häufiger Fehler:Ignorieren der Richtung der Flanke (steigend vs. fallend) bei Setup-/Hold-Zeiträumen.

- Häufiger Fehler:Annahme idealer Taktflanken mit null Übergangszeit.

Um diese Probleme zu vermeiden, sollten Setup- und Hold-Margen immer annotiert werden. Verwenden Sie deutliche Schattierungen oder Markierungen, um die verbotenen Bereiche anzuzeigen, in denen Datentransitionen ungültig sind. Diese visuelle Markierung zwingt die Überprüfer dazu, zu prüfen, ob der Signalpfad den Zeitvorgaben der empfangenden Logik entspricht.

2. Vernachlässigung von Takt-Skew und Jitter 🌪️

Takt-Skew bezeichnet die Differenz in den Ankunftszeiten des Taktsignals an verschiedenen Komponenten. Jitter stellt die kurzfristigen Schwankungen in der Zeitlage des Taktsignals dar. Beide Faktoren können die effektiven Zeitfenster für Datensignale erheblich verändern.

Ein häufiger Fehler in Diagrammen ist die Behandlung des Taktsignals als perfekt gerader vertikaler Linie über alle Komponenten hinweg. In Wirklichkeit führen Verteilungsnetzwerke zu Verzögerungen. Wenn ein Diagramm eine einzige Taktleitung zeigt, die sich in drei verschiedene Register verzweigt, ohne die Pfadunterschiede zu berücksichtigen, wird ein unrealistisches Bild des Systemverhaltens vermittelt.

- Auswirkung:Skew kann die verfügbare Zeit für die Signalverbreitung verringern und so falsche Setup-Verletzungen verursachen.

- Auswirkung:Jitter kann die Hold-Zeit-Marge verkleinern und das Risiko von Metastabilität erhöhen.

Bei der Erstellung von Diagrammen sollten Taktpfade bei signifikantem Skew als separate Linien mit relativen Verschiebungen dargestellt werden. Wenn der Skew vernachlässigbar ist, sollte diese Annahme in den Diagrammbemerkungen klar angegeben werden. Verbergen Sie die Komplexität der Taktverteilung nicht, wenn sie den Zeitbudget beeinflusst.

3. Inkonsistente Zeitskalen und Einheiten 📏

Einer der einfachsten, aber schädlichsten Fehler ist das Mischen von Zeitskalen innerhalb eines einzigen Diagramms. Ein Abschnitt könnte Nanosekunden anzeigen, während ein anderer Mikrosekunden zeigt. Diese Inkonsistenz zwingt den Leser dazu, ständig Verhältnisse neu zu berechnen, was die Wahrscheinlichkeit einer falschen Interpretation erhöht.

Ein weiteres Problem ist das Fehlen einer klaren Zeitachse. Ohne Maßstab oder beschriftete Markierungen wird die Dauer von Impulsen subjektiv. Ein kurzer Impuls könnte je nach Interpretation der Abstände 10 Nanosekunden oder 100 Nanosekunden betragen.

Beachten Sie diese Standards, um Konsistenz zu gewährleisten:

- Skala definieren:Platzieren Sie einen Zeitmaßstab am unteren oder oberen Rand des Diagramms.

- Wissenschaftliche Schreibweise verwenden:Beschreiben Sie die Einheiten (ns, μs, ps) eindeutig im Kopfbereich.

- Halten Sie die Verhältnisse proportional: Stellen Sie sicher, dass der horizontale Abstand zwischen Ereignissen der Zeitdifferenz entspricht.

Konsistenz schafft Vertrauen. Wenn jeder Ingenieur das Diagramm betrachtet, sollten sie die gleichen Zeitwerte ableiten können, ohne Annahmen über die Zeichnungsskala treffen zu müssen.

4. Mehrdeutigkeit bei Edge-Triggern 🔄

Digitale Logik beruht oft auf spezifischen Edge-Triggern, wie zum Beispiel dem steigenden oder fallenden Edge. Ein Zeitdiagramm muss explizit zeigen, welcher Edge die Aktion auslöst. Mehrdeutigkeit hier kann zu völlig entgegengesetztem Verhalten in der Hardware führen.

Ein häufiger Fehler ist das Zeichnen eines Taktsignals ohne Angabe des aktiven Edge. Wenn beispielsweise ein Flip-Flop am fallenden Edge auslöst, das Diagramm aber identisch mit einem steigenden Edge-Trigger aussieht, könnte der Logikdesigner das falsche Verhalten implementieren.

- Beste Praxis: Verwenden Sie Pfeile auf der Taktsignal-Linie, um den aktiven Edge anzugeben.

- Beste Praxis: Kennzeichnen Sie den Trigger-Typ in der Legende (z. B. „Posedge“, „Nedge“).

- Beste Praxis: Vermeiden Sie das Verwenden von Doppelpfeilen, es sei denn, beide Edges sind aktiv.

Klarheit ist entscheidend. Wenn ein Signal asynchron ist, stellen Sie sicher, dass es deutlich vom Taktsignalbereich getrennt ist, um Verwirrung darüber zu vermeiden, welcher Edge es steuert.

5. Übersehen von Ausbreitungsverzögerungen ⏳

Die Ausbreitungsverzögerung ist die Zeit, die ein Signal benötigt, um von der Eingabe zur Ausgabe durch ein Logikgatter oder einen Draht zu gelangen. In idealen Diagrammen scheinen Signale sofort zu wechseln. In physischen Systemen gibt es immer eine Verzögerung.

Wenn Designer Ausbreitungsverzögerungen weglassen, suggeriert das Zeitdiagramm, dass die Ausgabe sofort nach dem Eingabewechsel wechselt. Dies kann Zeitverletzungen verbergen, die in der Silizium-Implementierung auftreten werden. Beispielsweise könnte ein kombinatorischer Pfad im Diagramm die Taktrate erfüllen, aber die tatsächliche Verzögerung schiebt die Daten über den nächsten Taktkante hinaus.

| Funktion | Ideales Diagramm | Realitätsnahe Implementierung |

|---|---|---|

| Signalübergang | Senkrechte Linie | Gefällige Linie mit Verzögerung |

| Ausbreitung | Sofortig | Gatterverzögerung + Leiterverzögerung |

| Setup-Marge | Häufig nicht überprüft | Muss den schlechtesten Fall berücksichtigen |

Um dies zu minimieren, markieren Sie die erwartete Verzögerung für kritische Pfade. Wenn die Verzögerung im Verhältnis zur Taktrate signifikant ist, zeichnen Sie den Übergang mit einer Steigung oder markieren Sie den Verzögerungswert explizit. Diese visuelle Darstellung hilft Reviewern, potenzielle Engpässe vor der Fertigung zu erkennen.

6. Ignorieren von Metastabilitätsrisiken 🌌

Metastabilität tritt auf, wenn ein Flip-Flop Daten nahe der Taktkante erhält, wodurch es in einen undefinierten Zustand gerät, der eine unvorhersehbare Dauer hat. Zeitdiagramme erfassen diesen Zustand selten explizit, da es sich um einen Fehlerzustand handelt, nicht um eine normale Operation.

Allerdings ist die Ignorierung der Möglichkeit von Metastabilität in asynchronen Schnittstellen ein kritischer Fehler. Wenn ein Diagramm ein asynchrones Signal zeigt, das sich ohne Synchronisiererkette mit einem Takt synchronisiert, deutet dies auf ein Risiko von Datenverlust oder -korruption hin.

- Identifikation: Suchen Sie nach Signalen, die Taktbereiche ohne ordnungsgemäße Synchronisation überschreiten.

- Dokumentation: Notieren Sie, wo Metastabilität ein bekanntes Risiko darstellt und wie sie gemindert wird.

- Visualisierung: Verwenden Sie gestrichelte Linien, um asynchrone Grenzen zu kennzeichnen.

Selbst wenn das System zur Bewältigung von Metastabilität ausgelegt ist, sollte das Diagramm die Synchronisationsstufen widerspiegeln. Dadurch wird sichergestellt, dass das Verifizierungsteam weiß, dass diese spezifischen Bedingungen getestet werden müssen.

7. Signal-Sprünge und Gefahren ⚡

Sprünge sind transiente Impulse, die durch ungleiche Ausbreitungsverzögerungen in parallelen Pfaden entstehen. Sie können eine falsche Auslösung der Logik verursachen, wenn sie bei der Zeitplanungsanalyse nicht berücksichtigt werden.

Ein häufiger Fehler ist die Darstellung sauberer, stabiler Signale dort, wo Sprünge physisch unvermeidbar sind. Zum Beispiel könnte bei einem Multiplexer, der zwischen Eingängen wechselt, das Ausgangssignal kurz flackern, bevor es sich stabilisiert. Wenn das Diagramm einen reibungslosen Übergang zeigt, ist die nachgeschaltete Logik möglicherweise nicht darauf ausgelegt, diese Sprünge zu filtern.

Markieren Sie potenzielle Gefahrenzonen im Diagramm. Verwenden Sie Anmerkungen, um darauf hinzuweisen, dass ein bestimmtes Signal während Zustandsänderungen transientes Verhalten zeigen könnte. Dies informiert die Teststrategie, dass Szenarien zur Sprungdetektion enthalten sein müssen.

8. Fehlendes Kontext für Steuersignale 🔌

Daten-Signale sind nutzlos ohne den Kontext von Steuersignalen wie Enable, Reset oder Chip Select. Ein Diagramm, das sich ausschließlich auf Datenleitungen konzentriert, übersieht oft die Bedingungen, die erforderlich sind, damit die Daten gültig sind.

Zum Beispiel könnte ein Datenbus gültige Werte anzeigen, aber wenn das Signal „Write Enable“ während dieses Zeitfensters nicht als aktiv dargestellt wird, werden die Daten praktisch ignoriert. Umgekehrt, wenn „Write Enable“ aktiv ist, aber die Daten ungültig sind, schreibt das System Müll.

- Steuersignale einbeziehen: Zeigen Sie Steuersignale stets zusammen mit Datenignalen an.

- Gültigkeit definieren: Verwenden Sie eine „Valid“-Kennzeichnung oder ähnlichen Indikator, um anzugeben, wann Daten zuverlässig sind.

- Zustandsbedingungen: Kennzeichnen Sie deutlich den Zustand der Steuersignale (High-aktiv vs. Low-aktiv).

Vollständigkeit ist entscheidend. Ein Zeitdiagramm, das den Kontext der Steuersignale fehlt, ist oft eine Quelle der Verwirrung während der Fehlersuche. Stellen Sie sicher, dass die Beziehung zwischen Steuer- und Daten signalen visuell eindeutig ist.

9. Schlechte Verwendung von Anmerkungen und Legenden 📝

Selbst ein perfekt genaues Diagramm kann missverstanden werden, wenn es keine geeigneten Anmerkungen enthält. Symbole, Abkürzungen und Legenden müssen konsistent sein und erklärt werden.

Häufige Fehler bei Anmerkungen sind:

- Verwendung generischer Bezeichnungen wie „Signal A“ statt beschreibender Namen.

- Das Fehlen einer Erklärung für die Bedeutung spezifischer Linienstile (durchgezogen vs. gestrichelt).

- Das Weglassen der Definition des aktiven Pegels (aktiv hoch vs. aktiv niedrig).

Ein spezieller Legendenabschnitt sollte Bestandteil jedes Zeitdiagramms sein. Er definiert jedes verwendete Symbol, Linienstil und jede Abkürzung. Dadurch wird die kognitive Belastung für den Leser reduziert und sichergestellt, dass alle das Diagramm gleich interpretieren.

10. Überprüfungs- und Revisions-Checkliste ✅

Bevor ein Zeitablaufdiagramm endgültig festgelegt wird, ist eine systematische Überprüfung erforderlich. Verwenden Sie die folgende Prüfliste, um die Richtigkeit und Klarheit Ihrer Arbeit zu überprüfen.

| Prüfpunkt | Bestehenskriterium |

|---|---|

| Zeitskala | Konsistente Einheiten und eindeutige Maßstabslinie bereitgestellt |

| Taktrand | Aktiver Rand für alle Takte eindeutig gekennzeichnet |

| Setup/Hold | Fenster für synchrone Signale definiert |

| Ausbreitung | Verzögerungen in kritischen Pfaden berücksichtigt |

| Steuerzeichen | Enable-/Reset-Signale zusammen mit Daten dargestellt |

| Legenden | Alle Symbole und Abkürzungen erklärt |

| Domainschnittstelle | CDC-Punkte identifiziert und markiert |

Durch regelmäßiges Aktualisieren dieser Prüfliste wird sichergestellt, dass keine typischen Fehler durch das Raster fallen. Sie dient als Qualitätskontrolle für Dokumentationen, bevor sie beim Ingenieurteam ankommen.

11. Visuelle Klarheit und Layout-Design 🎨

Das Layout eines Zeitablaufdiagramms beeinflusst, wie leicht Fehler erkannt werden können. Überfüllte Diagramme mit überlappenden Signalen sind anfällig für falsche Interpretationen. Eine vertikale Ausrichtung verwandter Signale hilft dem Auge, die Beziehung zwischen Ereignissen nachzuverfolgen.

Beachten Sie diese Layout-Prinzipien:

- Signale gruppieren:Halten Sie verwandte Signale (wie Adresse und Daten) eng beieinander.

- Ränder ausrichten:Stellen Sie sicher, dass Taktränder über alle Kanäle vertikal ausgerichtet sind.

- Platzieren:Lassen Sie ausreichend weißen Raum, um Signalüberlappungen zu vermeiden.

- Farbcodierung:Verwenden Sie unterschiedliche Farben für verschiedene Taktdomänen, falls verfügbar (obwohl Schwarz-Weiß für den Druck Standard ist).

Ein sauberes Layout reduziert den kognitiven Aufwand, der zur Interpretation des Diagramms erforderlich ist. Dadurch wird es einfacher, Anomalien und Zeitverletzungen auf einen Blick zu erkennen.

12. Realitätsbedingungen gegenüber Simulation 🖥️

Zeitdiagramme, die ausschließlich aus Simulationen abgeleitet sind, spiegeln möglicherweise nicht die physikalischen Realitäten wider. Simulationswerkzeuge gehen oft von idealen Bedingungen aus, wie beispielsweise null parasitärer Kapazität und perfekter Verdrahtung.

Beim Übersetzen von Simulationsergebnissen in Dokumentation müssen Ingenieure Fertigungsvariationen berücksichtigen. Prozess-, Spannungs- und Temperatur (PVT)-Ecken können die Zeitintervalle verschieben. Ein Diagramm, das nur Nennwerte zeigt, könnte für eine robuste Auslegung unzureichend sein.

- Schlechtester Fall:Berücksichtigen Sie die langsamste Prozessecke für die Zeitanalyse.

- Schnellster Fall:Berücksichtigen Sie die schnellste Prozessecke für die Haltezeitanalyse.

- Abstand:Fügen Sie Sicherheitsabstände in das Diagramm ein, um PVT-Variationen zu berücksichtigen.

Die Dokumentation sollte die Robustheit des Designs widerspiegeln, nicht nur die besten Simulationsergebnisse. Dies bereitet das Team auf realitätsnahe Einsatzszenarien vor.

Abschließende Gedanken zur Zeitgenauigkeit 🛡️

Zeitdiagramme sind ebenso Kommunikationswerkzeuge wie technische Spezifikationen. Ihr primäres Ziel ist es, Absicht und Einschränkungen klar an alle Beteiligten weiterzugeben. Indem Ingenieure häufige Fehler vermeiden, wie die Vernachlässigung von Verzögerungen, das Ignorieren von Flankenauslösern oder das Weglassen von Steuersignalen, stellen sie sicher, dass die Entwurfsabsicht von der Dokumentation bis zur Hardware erhalten bleibt.

Genauigkeit in diesen Diagrammen verhindert kostspielige Neuaufbauten und Fehlersuchezyklen. Ein gut strukturiertes Diagramm dient als einziges Quellenwissen für die gesamte Projektlaufzeit. Investieren Sie die Zeit, um die Zeitanalyse richtig durchzuführen, dann verläuft die nachfolgende Implementierung reibungslos.

Denken Sie daran, dass ein Zeitdiagramm ein lebendiges Dokument ist. Es sollte bei jeder Änderung des Entwurfs aktualisiert werden. Die Aufrechterhaltung der Integrität der Zeitinformationen stellt sicher, dass das System während seiner gesamten Betriebszeit zuverlässig bleibt. Konzentrieren Sie sich auf Präzision, Klarheit und Vollständigkeit, um robuste digitale Designs zu liefern.