In der Welt der digitalen Elektronik und Hardware-Engineering beruht die Kommunikation zwischen Komponenten auf präziser Abstimmung. Ohne ein klares Verständnis dafür, wann Signale ihren Zustand wechseln, versagen Systeme. Das Zeitdiagramm dient als Bauplan für diese Abstimmung. Es visualisiert die Beziehung zwischen Signalen über die Zeit und zeigt auf, ob Daten gültig, stabil und zur Verarbeitung bereit sind. Dieser Leitfaden beantwortet die grundlegenden Fragen, mit denen Ingenieure und Studierende bei der Analyse dieser entscheidenden visuellen Werkzeuge konfrontiert werden.

Unabhängig davon, ob Sie eine Mikrocontroller-Schnittstelle entwerfen, einen Kommunikationsprotokoll fehlerfrei analysieren oder digitale Logik studieren – das Verständnis der zeitlichen Aspekte Ihres Entwurfs ist unverzichtbar. Dieser Artikel untersucht die Struktur von Zeitdiagrammen, erläutert zentrale Parameter und beantwortet häufig gestellte Fragen zu Signalintegrität und Synchronisation.

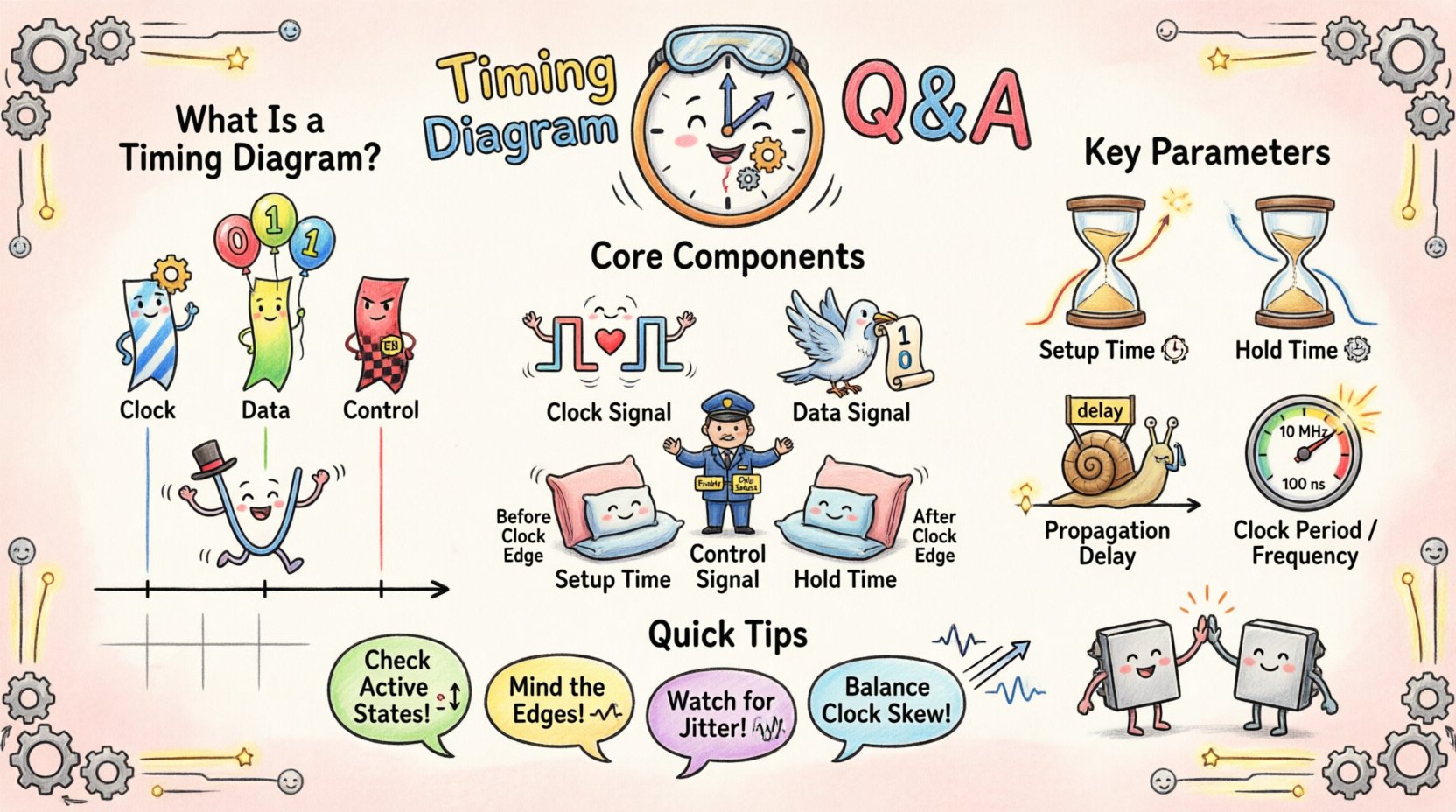

Was ist genau ein Zeitdiagramm? 📊

Ein Zeitdiagramm ist eine grafische Darstellung der Abfolge von Ereignissen in einem System. Es stellt Signalpegel entlang einer horizontalen Zeitachse dar. Im Gegensatz zu einer Logikschaltung, die die Verbindungen zeigt, verdeutlicht ein Zeitdiagramm das Verhalten. Es ermöglicht Ihnen, zu erkennen, ob ein Signal vor oder nach einem anderen Signal auf Hoch oder Niedrig wechselt. Dieser visuelle Kontext ist entscheidend, um sicherzustellen, dass ein Empfänger ausreichend Zeit hat, die Daten zu lesen, bevor der nächste Taktflankeneintritt erfolgt.

Wichtige Merkmale sind:

- Zeitachse: Läuft normalerweise horizontal von links nach rechts.

- Signalleitungen: Horizontale Linien, die einzelne Leitungen oder Datenbusse darstellen.

- Logische Pegel: Hohe (1) und niedrige (0) Zustände werden als deutlich voneinander abgegrenzte Spannungsplateaus dargestellt.

- Flanken: Vertikale Linien, die den Übergang von einem Zustand zum anderen anzeigen.

Wichtige Bestandteile eines Zeitdiagramms 🧩

Um diese Diagramme effektiv zu lesen, müssen Sie die Standardelemente identifizieren, aus denen die Wellenform besteht. Jedes Element spielt eine spezifische Rolle bei der Synchronisation des Systems.

| Komponente | Beschreibung | Visueller Indikator |

|---|---|---|

| Taktsignal | Bietet das „Herzschlag“ des Systems. Andere Signale werden oft relativ zu diesem abgetastet. | Regelmäßiges Rechteckwellenmuster |

| Daten-Signal | Trägt die tatsächlich übertragenen Informationen. | Unregelmäßige Übergänge basierend auf der Eingabe |

| Steuer-Signal | Steuerung des Datenflusses (z. B. Enable, Chip Select, Schreiben). | Aktiv-hoch- oder aktiv-niedrig-Pulse |

| Vorhaltezeit | Die Dauer, in der Daten stabil sein müssen, bevor eine Taktflanke eintritt. | Horizontale Distanz vor der Kante |

| Hold-Zeit | Die Dauer, in der die Daten stabil bleiben müssen, nachdem ein Taktkante aufgetreten ist. | Horizontale Distanz nach der Kante |

Verständnis der wichtigsten Zeitparameter ⚙️

Zeitparameter definieren die Einschränkungen, innerhalb derer eine digitale Schaltung korrekt arbeitet. Die Verletzung dieser Parameter führt oft zu unvorhersehbarem Verhalten. Nachfolgend finden Sie Definitionen und Implikationen der wichtigsten Metriken.

1. Setup-Zeit ⏳

Die Setup-Zeit ist die minimale Zeitspanne, in der das Datensignal stabil gehalten werden sollte, bevor die auslösende Kante des Taktsignals eintritt. Wenn sich das Datenignal zu nahe an der Taktkante ändert, kann der Flip-Flop den Wert möglicherweise nicht korrekt erfassen. Dies ist oft die kritischste Einschränkung bei Hochgeschwindigkeitsdesigns, da sie die maximale Betriebsfrequenz festlegt.

2. Hold-Zeit ⏳

Die Hold-Zeit ist die minimale Zeitspanne, in der das Datensignal stabil gehalten werden sollte, nachdem die auslösende Kante des Taktsignals eingetreten ist. Im Gegensatz zur Setup-Zeit ist die Hold-Zeit im Allgemeinen unabhängig von der Taktfrequenz. Sie hängt von der internen Verzögerung des Flip-Flops und der externen Ausbreitungsverzögerung der Datenumleitung ab.

3. Propagierungsverzögerung ⏳

Dies ist die Zeit, die ein Signal benötigt, um von der Eingabe einer Komponente bis zu ihrer Ausgabe zu gelangen. Sie variiert je nach Temperatur, Spannung und Fertigungstoleranzen. In einem Zeitdiagramm erscheint dies als Verzögerung zwischen einer Änderung eines Signals und der daraus resultierenden Änderung eines anderen Signals.

4. Taktkreiszeit und Frequenz ⏳

Die Taktkreiszeit ist die Dauer eines vollständigen Zyklus des Taktsignals. Die Frequenz ist der Kehrwert der Periode. Eine kürzere Periode bedeutet eine höhere Frequenz, was eine schnellere Verarbeitung ermöglicht, aber die Zeitspanne für Signalstabilität verengt.

Häufig gestellte Fragen ❓

Ingenieure stoßen oft auf spezifische Szenarien, die Verwirrung stiften. Hier finden Sie detaillierte Antworten auf die dringlichsten Fragen zur Zeitanalyse.

F: Was passiert, wenn die Setup-Zeit verletzt wird? 🛑

Wenn die Anforderung an die Setup-Zeit nicht erfüllt ist, gelangt der Flip-Flop in einen Zustand, der alsMetastabilität. In diesem Zustand setzt sich die Ausgabe nicht sofort auf einen gültigen Logikpegel hoch oder niedrig fest. Stattdessen kann sie oszillieren oder für eine unvorhersehbare Zeitspanne auf einem mittleren Spannungsniveau verbleiben. Dies kann dazu führen, dass die nachgeschaltete Logik einen beschädigten Wert liest, was zu Systemfehlern oder Abstürzen führen kann. In schweren Fällen kann die Metastabilität sich durch die gesamte Schaltung ausbreiten und eine funktionsunfähige Störung verursachen, die schwer zu debuggen ist.

F: Wie gehe ich mit Taktschiefe um? 🔄

Taktschiefe tritt auf, wenn das Taktsignal zu verschiedenen Komponenten zu unterschiedlichen Zeiten eintrifft. Dies kann aufgrund unterschiedlicher Pfadlängen oder Lastunterschiede auftreten. Um die Schiefe zu verwalten:

- Ausgleich der Verdrahtung: Stellen Sie sicher, dass die Taktsignalleitungen mit ähnlichen Längen und Breiten verlegt werden.

- Pufferung: Verwenden Sie Taktpuffer, um mehrere Lasten gleichmäßig zu versorgen.

- Zeitpuffer: Gestalten Sie das System mit ausreichendem Spielraum in Setup- und Hold-Zeiten, um geringfügige Schiefevariationen auszugleichen.

F: Was ist der Unterschied zwischen synchroner und asynchroner Zeitsteuerung? ⚖️

In synchronSysteme werden alle Operationen durch ein einzelnes Taktsignal koordiniert. Zeitdiagramme für diese Systeme zeigen regelmäßige, sich wiederholende Taktränder. In asynchronSysteme lösen Signale aus, ohne einen globalen Takt. Zeitdiagramme für diese Systeme zeigen ereignisgesteuerte Übergänge, oft mit größerer Variation in den Abständen zwischen Signalen. Asynchrone Designs sind schwerer zu analysieren, können aber in bestimmten Low-Power-Anwendungen energiesparender sein.

F: Wie wirkt sich Jitter auf ein Zeitdiagramm aus? 📉

Jitter ist die kurzfristige Abweichung eines Signals von seiner idealen Position in der Zeit. In einem Zeitdiagramm zeigt sich dies darin, dass die Ränder des Taktsignals etwas früher oder später erscheinen, als es sein sollte. Zu viel Jitter verringert das effektive Fenster zum Erfassen von Daten. Es verkleinert praktisch die Setup- und Hold-Margen und erhöht das Risiko von Zeitverletzungen. Hochgeschwindigkeitsschnittstellen erfordern strenge Jitter-Kontrolle, um die Datenintegrität zu gewährleisten.

F: Kann ich Zeitdiagramme ohne Takt lesen? 🕵️

Ja, aber es erfordert einen anderen Ansatz. Asynchrone Protokolle wie I2C oder UART verwenden nicht immer eine gemeinsame Taktsignalleitung. Stattdessen beruhen sie auf vordefinierten Baudraten oder Handshake-Signalen. In diesen Diagrammen müssen Sie auf die Pulsbreiten und die Zeit zwischen Übergängen achten, um die Datenrate abzuleiten. Zum Beispiel definiert die Dauer eines Startbits in UART die Zeit für die nachfolgenden Datenbits.

Lesen und Interpretieren von Wellenformen 🔍

Die Interpretation eines Zeitdiagramms erfordert einen systematischen Ansatz. Zufälliges Scannen der Linien führt oft zu übersehenen Details. Folgen Sie diesem Prozess für eine genaue Analyse.

- Identifizieren Sie die Referenz: Finden Sie das Taktsignal oder das primäre Steuersignal. Alle anderen Zeiten beziehen sich darauf.

- Überprüfen Sie die aktiven Zustände: Bestimmen Sie, ob Signale aktiv hoch oder aktiv niedrig sind. Ein niedriger Puls könnte „aktiviert“ bedeuten, während ein hoher Puls „deaktiviert“ bedeutet. Dies wird oft durch ein Kreiszeichen am Pin-Namen in Schaltplänen angezeigt.

- Analysieren Sie die Kantenausrichtung: Achten Sie genau darauf, wo Datenecken mit Taktkanten ausgerichtet sind. Daten sollten idealerweise dann wechseln, wenn der Takt stabil ist (z. B. in der niedrigen Phase) und während der aktiven Kante stabil bleiben.

- Verfolgen Sie Abhängigkeiten: Verfolgen Sie die Ursache-Wirkungs-Beziehung. Wenn Signal A Signal B auslöst, sollte zwischen ihnen eine klare Verzögerung bestehen, die der Propagationsverzögerung entspricht.

- Überprüfen Sie die Pulsbreiten: Stellen Sie sicher, dass aktive Pulse breit genug sind, damit das empfangende Bauteil sie erkennen kann. Ein zu schmaler Puls kann als Rauschen herausgefiltert werden.

Häufige Fehler bei der Diagramminterpretation ❌

Selbst erfahrene Ingenieure können Diagramme falsch interpretieren, wenn sie bestimmte Details übersehen. Vermeiden Sie diese häufigen Fallen.

- Ignorieren der Logikpegel: Annahme, dass alle Signale aktiv hoch sind, ohne Überprüfung. Prüfen Sie immer die Datenblätter oder Schaltpläne.

- Übersehen der Propagationsverzögerungen: Annahme, dass Signale sofort wechseln. Reale Komponenten haben endliche Reaktionszeiten.

- Falsches Lesen der Zeitskalen: Nicht bemerken der Zeiteinheit (Nanosekunden gegenüber Mikrosekunden). Ein Signal, das bei langsamer Vergrößerung stabil erscheint, kann bei schneller Vergrößerung Störungen zeigen.

- Ignorieren der Stromzustände: Zeitdiagramme ändern sich oft, wenn ein Gerät in den Ruhezustand wechselt. Stellen Sie sicher, dass Sie die aktive Zeitfolge betrachten.

Strategien für eine genaue Analyse 🛠️

Stellen Sie sicher, dass Ihre Zeitanalyse robust ist, indem Sie diese Strategien übernehmen. Diese Methoden helfen, Konsistenz zu gewährleisten und die Wahrscheinlichkeit von Fehlern zu verringern.

- Verwenden Sie Gitterlinien:Richten Sie Ihre Cursor oder Markierungen an den Gitterlinien im Diagramm aus, um Zeitintervalle genau zu messen.

- Dokumentieren Sie Annahmen:Notieren Sie die angenommene Taktfrequenz und Logikpegel, bevor Sie die Analyse beginnen. Dadurch wird späterer Verwirrung vorgebeugt.

- Kreuzverweis:Vergleichen Sie das Zeitdiagramm mit der Zustandsmaschinenlogik. Jeder Zustandswechsel sollte einem entsprechenden Zeitereignis entsprechen.

- Simulieren Sie Variationen:Berücksichtigen Sie die ungünstigsten Szenarien. Was passiert, wenn die Temperatur steigt und die Verzögerungen zunehmen? Was geschieht, wenn die Spannung sinkt und die Treibkraft abnimmt?

- Konzentrieren Sie sich auf kritische Pfade:Identifizieren Sie den längsten Pfad in Ihrer Logik. Dieser Pfad bestimmt die maximale Taktfrequenz des Systems. Priorisieren Sie die Zeitanalyse für diese spezifischen Pfade.

Die Auswirkungen von Zeitverletzungen ⚠️

Das Verständnis, warum die Zeitplanung wichtig ist, ist entscheidend. Wenn eine Zeitverletzung auftritt, ändert sich das physikalische Verhalten der Schaltung. Die häufigste Folge ist Datenkorruption. Ein Register könnte eine ‘1’ erfassen, obwohl eine ‘0’ erfasst werden sollte. Bei Kommunikationsprotokollen führt dies zu Rahmenfehlern oder verlorenen Paketen. In Steuerungssystemen kann dies zu falschen Aktorbefehlen führen, was möglicherweise physische Schäden oder Sicherheitsrisiken verursacht.

Darüber hinaus können Zeitverletzungen intermittierende Ausfälle verursachen. Ein System könnte bei Raumtemperatur einwandfrei funktionieren, aber ausfallen, wenn es sich erwärmt. Dies geschieht, weil sich die Propagierungsverzögerungen mit der Temperatur erhöhen. Die Gestaltung mit ausreichenden Zeitpuffern berücksichtigt diese Umweltveränderungen.

Best Practices für Zeitdiagramme 📝

Klare und genaue Zeitdiagramme zu erstellen, ist eine Fähigkeit, die sich durch Übung verbessert. Folgen Sie diesen Richtlinien, um Diagramme zu erstellen, die für andere leicht verständlich sind.

- Beschriften Sie alles:Jede Signalleitung sollte einen klaren Namen haben. Vermeiden Sie generische Bezeichnungen wie „Signal 1“.

- Verwenden Sie eine einheitliche Skala:Halten Sie eine einheitliche Zeitskala über das gesamte Diagramm aufrecht, es sei denn, Sie müssen einen bestimmten Ereignis vergrößern.

- Hervorhebung kritischer Ereignisse:Verwenden Sie verschiedene Farben oder dickere Linien, um Setup- und Hold-Zeiträume zu markieren.

- Fügen Sie Anmerkungen hinzu:Fügen Sie Textnotizen hinzu, um komplexe Wechselwirkungen oder spezifische Einschränkungen zu erklären.

- Überprüfen Sie mit Datenblättern:Überprüfen Sie Ihre Diagrammparameter immer mit den offiziellen Bauteilspezifikationen.

Erweiterte Überlegungen: Mehrere Taktsysteme 🌐

Moderne Systeme verwenden oft mehrere Taktsysteme. Zum Beispiel könnte ein Prozessor mit 2 GHz laufen, während ein Speichercontroller mit 400 MHz arbeitet. Zeitdiagramme für diese Systeme werden deutlich komplexer. Sie müssen berücksichtigen:

- Quer-Takt-Abtastung: Wie Daten von einer Frequenz zur anderen bewegt werden.

- FIFO-Puffer: Wie der Datenfluss zwischen asynchronen Taktquellen synchronisiert wird.

- Reset-Synchronisation: Sicherstellen, dass alle Bereiche koordiniert zurückgesetzt werden, um Zustandsinkonsistenzen zu vermeiden.

Beim Analysieren dieser Diagramme achten Sie auf die Synchronisationslogik, wie zum Beispiel Handshake-Signale oder Synchronisiererketten. Diese Komponenten sind speziell dafür ausgelegt, die Lücke zwischen verschiedenen Zeitdomänen sicher zu überbrücken.

Schlussfolgerung: Präzision ist entscheidend 🔑

Zeitdiagramme sind mehr als nur Bilder; sie sind der mathematische Beweis für ein funktionierendes System. Sie definieren die Grenzen von Zuverlässigkeit und Leistungsfähigkeit. Durch das Verständnis der zentralen Komponenten, Parameter und möglichen Fallstricke können Sie Systeme entwerfen, die unter realen Bedingungen korrekt funktionieren. Die Beachtung von Ansprechzeiten, Haltezeiten und Ausbreitungsverzögerungen unterscheidet einen funktionsfähigen Prototypen von einem produktionsreifen Produkt. Regelmäßiges Üben im Lesen und Erstellen dieser Diagramme schärft Ihr technisches Empfinden und verbessert Ihre ingenieurtechnischen Ergebnisse.

Denken Sie daran, dass jeder Übergang eine Geschichte über den Informationsfluss erzählt. Respektieren Sie die Zeit, die diese Information benötigt, um zu reisen, und Ihre Entwürfe werden der Zeit standhalten.