En el mundo de la electrónica digital y la ingeniería de computadoras, las señales no existen en el vacío. Viajan a través de trazos, a través de puertas y hacia procesadores con restricciones temporales específicas. Para entender cómo funciona un sistema, los ingenieros deben visualizar cómo cambian estas señales con el tiempo. Esta visualización se logra mediante un diagrama de tiempo. Para un principiante, estas gráficas pueden parecer jeroglíficos complejos, pero en realidad son la herramienta más fundamental para depurar y diseñar lógica digital.

Esta guía ofrece un análisis exhaustivo de los diagramas de tiempo. Exploraremos la anatomía de una señal, los parámetros críticos que definen la fiabilidad y los errores comunes que provocan fallas en el sistema. Ya sea que estés estudiando para un examen o diseñando tu primer circuito de microcontrolador, comprender estos diagramas es esencial.

🧠 ¿Qué es un Diagrama de Tiempo?

Un diagrama de tiempo es una representación gráfica del estado de las señales digitales con el tiempo. A diferencia de un esquema de circuito, que muestraquéestá conectado a qué, un diagrama de tiempo muestracuándoocurren las cosas. Representa los niveles de voltaje contra un eje de tiempo, permitiendo a los ingenieros ver la secuencia de eventos.

Estos diagramas son indispensables por varias razones:

- Depuración: Revelan condiciones de carrera en las que las señales llegan fuera de orden.

- Verificación: Confirman que un circuito cumple con las especificaciones de velocidad requeridas.

- Documentación: Sirven como referencia sobre cómo se comunican diferentes chips.

- Diseño: Ayudan a determinar la frecuencia máxima del reloj que un sistema puede soportar.

Cuando miras un diagrama de tiempo, estás viendo una instantánea del comportamiento físico de los electrones que se mueven a través de un sistema. Captura la realidad de la latencia, la propagación y la sincronización.

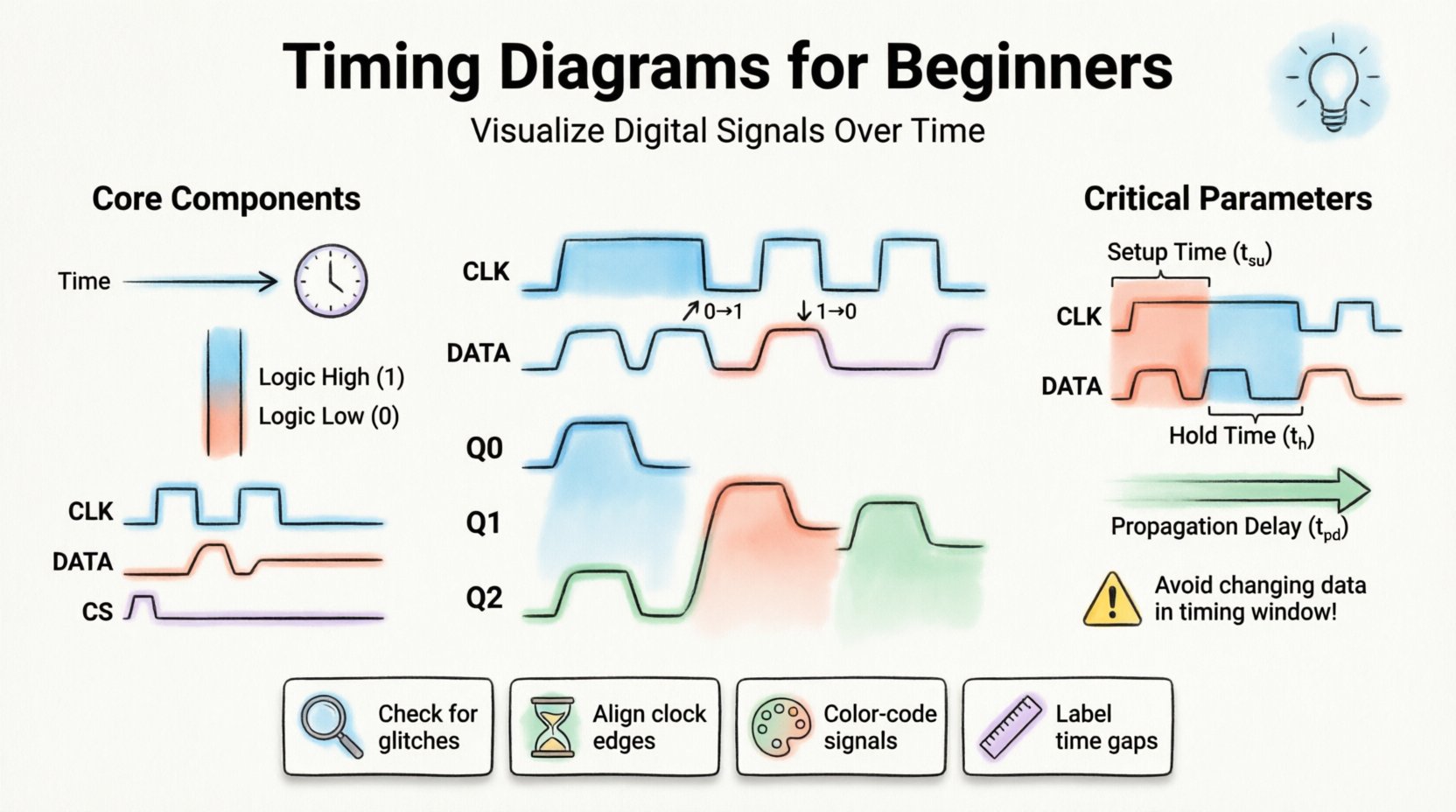

📊 Componentes Fundamentales de un Diagrama de Tiempo

Antes de analizar formas de onda complejas, debes entender los bloques de construcción. Cada diagrama de tiempo consta de unos pocos elementos fundamentales.

1. El Eje del Tiempo

El eje horizontal representa el tiempo. Fluye de izquierda a derecha. En el diseño digital, este eje a menudo se segmenta en ciclos de reloj, marcados por líneas de cuadrícula verticales. La escala puede variar desde nanosegundos (ns) para procesadores de alta velocidad hasta milisegundos (ms) para lógica de control más lenta.

2. El Eje del Nivel de Voltaje

El eje vertical representa el estado lógico de la señal. En familias lógicas estándar, esto suele ser binario:

- Lógica Alta (1):A menudo representado como VCC o 5V.

- Lógica Baja (0):A menudo representado como tierra o 0V.

- High-Z (alta impedancia):Un estado en el que el pin está efectivamente desconectado, común en los sistemas de bus.

3. Líneas de señal

Cada línea horizontal representa un cable específico o un nombre de señal. Estas líneas están etiquetadas claramente (por ejemplo, CLK, DATA_IN, CS) para identificar qué parte del circuito se está monitoreando.

🔄 Leyendo las transiciones de señal

El movimiento de la línea de señal hacia arriba y hacia abajo es donde reside los datos. Comprender la dirección de estos movimientos es fundamental.

⬆️ Borde ascendente

Un borde ascendente ocurre cuando una señal cambia de bajo a alto. En la lógica binaria, este es a menudo el punto de activación para muchas operaciones. Representa un cambio de 0 a 1.

⬇️ Borde descendente

Un borde descendente ocurre cuando una señal cambia de alto a bajo. Esto representa un cambio de 1 a 0.

⚡ Disparo por borde

Muchos componentes digitales, como los flip-flops, solo responden a estos bordes en lugar del estado estable. Un flip-flop podría capturar datos solo en el borde ascendentede una señal de reloj. Si pierdes el borde, los datos se pierden.

| Transición | Dirección | Cambio binario | Tipo común de disparo |

|---|---|---|---|

| Borde ascendente | Bajo ➔ Alto | 0 ➔ 1 | Disparado por borde positivo |

| Borde descendente | Alto ➔ Bajo | 1 ➔ 0 | Disparado por borde negativo |

| Nivel alto | Alto constante | 1 constante | Sensible al nivel |

| Nivel bajo | Bajo estable | Estable 0 | Sensible al nivel |

⏳ Parámetros críticos de temporización

Los diagramas de temporización no son solo imágenes; contienen mediciones. El espacio entre los cambios de señal es donde se determina la fiabilidad. Tres parámetros específicos dominan el análisis de temporización digital.

1. Retardo de propagación (tpd)

Las señales no viajan instantáneamente. Cuando cambia una entrada, transcurre un tiempo finito antes de que la salida refleje ese cambio. Este es el retardo de propagación. Es causado por la resistencia física y la capacitancia de los materiales.

- Definición: La diferencia de tiempo entre el cambio de entrada y el cambio de salida.

- Impacto: En una cadena de puertas lógicas, los retardos se acumulan. Si el retardo es demasiado largo, la señal podría llegar después de que comience el siguiente ciclo de reloj, causando errores.

2. Tiempo de preparación (tsu)

El tiempo de preparación es el requisito para que una señal de datos permanezca estableantes de que llegue una transición de reloj. Si los datos cambian demasiado cerca de la transición del reloj, el circuito receptor no puede capturarlos correctamente.

- Regla: Los datos deben ser válidos durante una duración específica antes de que el reloj se active.

- Visual: En un diagrama, esta es la brecha entre la estabilización de la línea de datos y la transición del reloj.

3. Tiempo de retención (th)

El tiempo de retención es el requisito para que la señal de datos permanezca establedespués de cuando llega el borde del reloj. Si los datos cambian inmediatamente después del borde del reloj, el circuito podría no capturar el valor correcto.

- Regla:Los datos deben permanecer sin cambios durante una duración específica después de que el reloj se active.

- Visual:En un diagrama, esta es la brecha entre el borde del reloj y la siguiente transición de datos.

⚠️ La Ventana de Tiempo

La combinación del tiempo de preparación y el tiempo de retención crea una ventana válida para capturar datos. Si su diagrama de tiempo muestra que los datos cambian dentro de esta ventana, el sistema está en riesgo de fallar.

⚡ Sistemas Síncronos frente a Asíncronos

Los diagramas de tiempo difieren significativamente según la arquitectura del sistema.

Sistemas Síncronos

En el diseño síncrono, todas las operaciones están coordinadas por una señal de reloj global. Cada cambio de estado ocurre en el borde de este reloj. Los diagramas de tiempo para estos sistemas tienen un aspecto muy regular.

- Características:Predecibles, más fáciles de diseñar, limitados por la velocidad del reloj.

- Aspecto del Diagrama:Las líneas verticales de la cuadrícula se alinean perfectamente con todos los cambios de señal.

Sistemas Asíncronos

En el diseño asíncrono, no existe un reloj global. Las señales cambian cada vez que cambian las entradas. Esto ofrece un mayor potencial de velocidad, pero hace que el análisis de tiempo sea mucho más difícil.

- Características:Respuesta más rápida ante entradas, análisis de peligros complejo.

- Aspecto del Diagrama:Las transiciones de señal ocurren a intervalos irregulares. Debe medir las brechas de tiempo exactas entre los eventos.

📝 Cómo dibujar un diagrama de tiempo

Crear un diagrama de tiempo es un proceso sistemático. Siga estos pasos para documentar un circuito o verificar un diseño.

- Identifique las señales: Liste todas las entradas, salidas y líneas de control internas. Etiquételas claramente.

- Establezca la base de tiempo:Decida la escala de tiempo. Para circuitos lógicos, los ciclos de reloj suelen ser la unidad estándar.

- Dibuje el reloj:Dibuje siempre la señal de reloj primero. Es la referencia para todos los demás eventos.

- Mapa de las entradas Dibuje las formas de onda de entrada según la operación lógica o la secuencia de pruebas.

- Calcule los retrasos:Desplace las señales de salida hacia la derecha según el retardo de propagación de las puertas involucradas.

- Verifique las restricciones:Verifique que se cumplan los tiempos de preparación y retención para cada flip-flop.

- Revise las transiciones:Asegúrese de que no haya picos. Un pico es un pulso breve e involuntario que puede activar incorrectamente la lógica.

🔄 Ejemplo del mundo real: Un contador simple

Para visualizar cómo funcionan juntos estos conceptos, considere un contador binario simple de 3 bits. Este circuito incrementa su valor cada vez que la señal de reloj pulsa.

Imagine tres líneas de salida: Q0, Q1 y Q2. Q0 cambia de estado en cada ciclo de reloj. Q1 cambia de estado cada vez que Q0 completa un ciclo completo. Q2 cambia de estado cada vez que Q1 completa un ciclo completo.

Análisis paso a paso

- Reloj (CLK):Una onda cuadrada con un ciclo de trabajo del 50%.

- Q0 (bit menos significativo):Cambia de estado en cada flanco ascendente del reloj. La frecuencia es la mitad del reloj.

- Q1:Cambia de estado en cada flanco ascendente de Q0. La frecuencia es la mitad de Q0.

- Q2 (bit más significativo):Cambia de estado en cada flanco ascendente de Q1. La frecuencia es la mitad de Q1.

Al dibujar esto, notará un efecto de rebote. Q0 cambia primero. Q1 espera a que Q0 se estabilice antes de cambiar. Q2 espera a que Q1 se estabilice. Esta acumulación de retrasos es la esencia de un contador de rebote.

| Ciclo de reloj | Q2 | Q1 | Q0 | Valor decimal |

|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 2 |

| 4 | 0 | 1 | 1 | 3 |

| 5 | 1 | 0 | 0 | 4 |

⚠️ Errores comunes que debes evitar

Incluso los ingenieros con experiencia pueden cometer errores al leer diagramas de tiempo. Ten en cuenta estos errores comunes.

- Ignorar los picos:Un pulso breve podría no ser visible si la escala de tiempo es demasiado grande, pero podría activar una trampa. Revisa siempre la existencia de pulsos estrechos.

- Malinterpretar el ciclo de trabajo:Suponer que un reloj es del 50 % cuando en realidad está sesgado. Esto afecta la ventana de tiempo.

- Descuidar los estados de alta impedancia:En los sistemas de bus, las líneas están flotando. Un diagrama de tiempo debe mostrar cuándo una línea está activa frente a cuándo está flotando.

- Confundir el tiempo de establecimiento y el de retención: El tiempo de establecimiento es antes del borde; el de retención es después. Confundirlos conduce a diseños incorrectos de circuitos.

- Ignorar la referencia de tierra: Todos los niveles de voltaje deben medirse con respecto al mismo punto de tierra. Si las tierras son diferentes, los niveles lógicos son inválidos.

🛠 Mejores prácticas para la documentación

Al crear diagramas de temporización para documentación o depuración, siga estas directrices para asegurar la claridad.

- Utilice una escala consistente: Asegúrese de que el eje del tiempo sea lineal. No comprima una sección y estire otra a menos que esté marcado explícitamente.

- Alinee los bordes críticos: Asegúrese de que el borde del reloj se alinee perfectamente con el punto de muestreo de los datos.

- Etiquete los espacios: Si hay un retardo, etiquételo con el valor de tiempo específico (por ejemplo, tpd = 5ns).

- Codificación por colores: Utilice colores distintos para diferentes tipos de señales (por ejemplo, azul para reloj, rojo para datos, verde para control).

- Marque los estados activos: Indique claramente si una señal está activa en alto o activa en bajo (por ejemplo, usando una barra sobre el nombre como /CS).

🧩 Metastabilidad y riesgos de temporización

Los diagramas de temporización avanzados revelan a menudo un fenómeno llamado metastabilidad. Esto ocurre cuando una señal cambia exactamente en la ventana de establecimiento/sostenimiento de un flip-flop. La salida no se establece inmediatamente en 0 o 1; permanece en un nivel de voltaje intermedio.

Aunque es raro, la metastabilidad puede causar fallos del sistema. Los diagramas de temporización ayudan a predecir esto al mostrar la relación entre las entradas asíncronas y el reloj síncrono. Si una señal externa cambia demasiado cerca del borde del reloj, el diagrama mostrará que los datos cruzan el umbral en el momento incorrecto.

🔍 Análisis de datos reales

Cuando observa un diagrama de temporización generado por un analizador lógico, las líneas rara vez son cuadrados perfectos. Las señales del mundo real tienen:

- Tiempo de subida: El tiempo que tarda en pasar de bajo a alto. Rara vez es instantáneo.

- Tiempo de caída: El tiempo que tarda en pasar de alto a bajo.

- Sobrepico/subpico: Picos de voltaje que superan los niveles de alimentación.

- Jitter: Variaciones en el tiempo de los bordes de la señal.

Comprender estas imperfecciones es vital para el diseño de alta velocidad. Una onda cuadrada perfecta es una idealización teórica; las señales reales son formas de onda analógicas que representan lógica digital.

📚 Resumen de los puntos clave

Los diagramas de tiempo son el lenguaje del tiempo digital. Traducen la lógica abstracta a la realidad física. Al dominarlos, adquirirás la capacidad de:

- Visualizar el flujo de datos a través de un sistema.

- Identificar dónde podrían producirse conflictos entre señales.

- Asegurarse de que los datos se capturen de forma confiable.

- Calcular la velocidad máxima de operación de un circuito.

Comienza practicando con puertas lógicas simples. Dibuja la entrada, calcula el retardo y traza la salida. A medida que avances, pasa a buses y dominios de reloj más complejos. Con paciencia y práctica, leer estos diagramas se convertirá en algo natural.

🚀 Avanzando

Continúa explorando los matices de la integridad de señales y las redes de distribución de reloj. A medida que los sistemas se vuelven más rápidos, los márgenes de tiempo se reducen. La capacidad de leer un diagrama de tiempo con precisión seguirá siendo una competencia fundamental para cualquier ingeniero que trabaje con hardware digital.