En el diseño digital moderno, comprender el flujo de señales a lo largo del tiempo es fundamental para garantizar la fiabilidad del sistema. Los sistemas asíncronos, donde las operaciones no están gobernadas por un único reloj global, presentan desafíos únicos en comparación con sus contrapartes síncronas. La herramienta principal utilizada para visualizar y depurar estas interacciones complejas es el diagrama de tiempo. Esta guía ofrece una exploración profunda sobre cómo construir, leer y analizar diagramas de tiempo en entornos asíncronos.

La naturaleza del diseño asíncrono 🌐

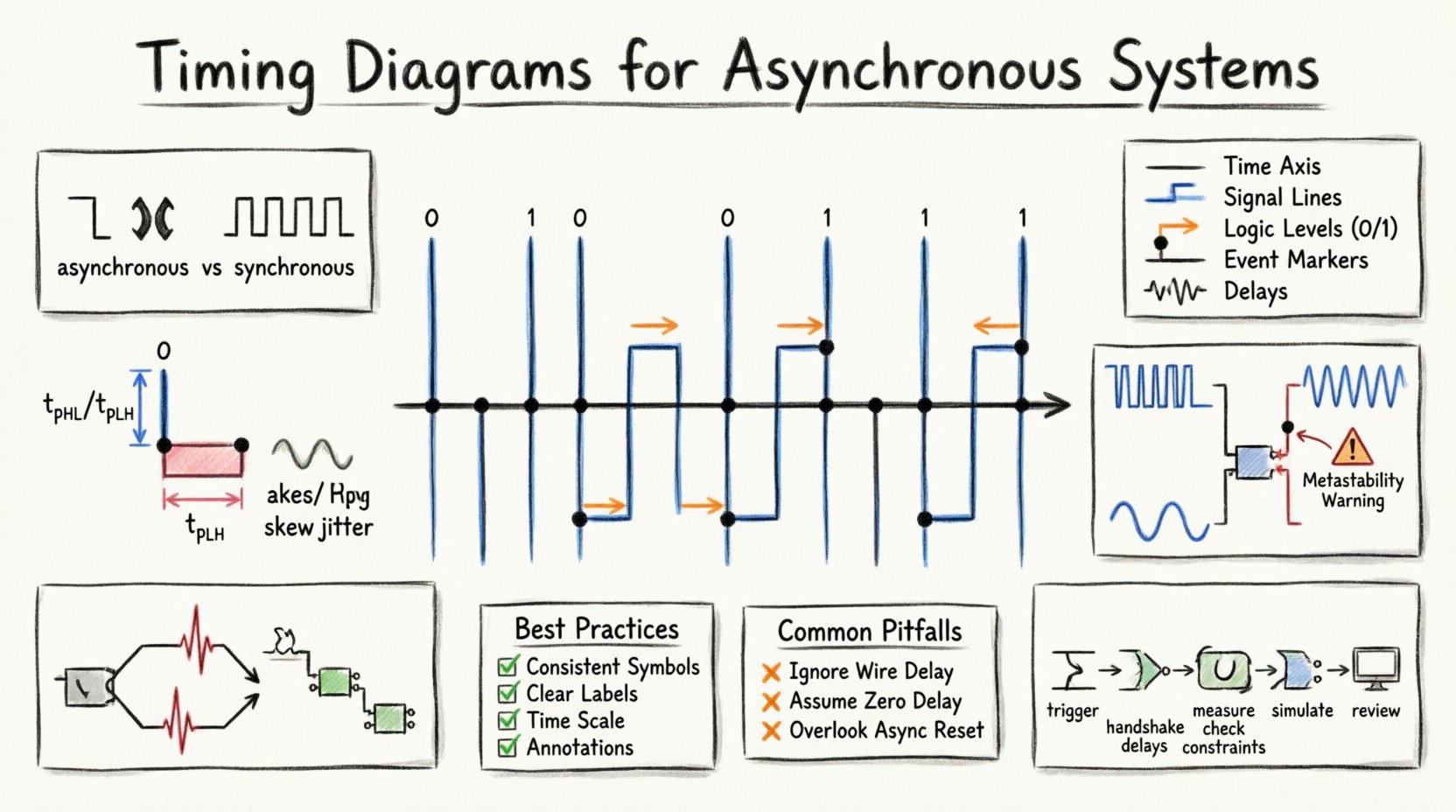

Los sistemas asíncronos operan sin una señal de reloj centralizada que impulse cada cambio de estado. En su lugar, los eventos se activan con la finalización de operaciones anteriores o con la llegada de datos. Este enfoque ofrece beneficios como un consumo reducido de energía y un rendimiento potencial más alto en contextos específicos. Sin embargo, introduce complejidad en cuanto a la sincronización de señales y la verificación del tiempo.

Cuando los ingenieros analizan estos sistemas, deben tener en cuenta los retrasos variables, los tiempos de propagación y la ausencia de un punto de referencia universal. Los diagramas de tiempo sirven como el lenguaje visual para representar estos eventos. Permiten a los equipos ver la relación exacta entre las transiciones de señal a lo largo del tiempo.

Anatomía de un diagrama de tiempo 📐

Un diagrama de tiempo es una representación gráfica del comportamiento de una señal. Representa el tiempo a lo largo del eje horizontal y los estados de la señal a lo largo del eje vertical. Para analizar de forma efectiva un sistema asíncrono, se debe comprender los componentes fundamentales que conforman estos diagramas.

- Eje del tiempo: Representa la progresión del tiempo. En el análisis asíncrono, esto suele ser relativo a un desencadenante de evento específico, más que a un ciclo de reloj.

- Líneas de señal:Líneas horizontales que representan cables o redes individuales. Cada línea rastrea el nivel lógico (Alto, Bajo o Desconocido) de una señal específica.

- Niveles lógicos:Normalmente indicados como

0(Bajo/Tierra) y1(Alto/VCC). Las transiciones entre estos estados son el núcleo del análisis. - Marcadores de evento:Líneas verticales o anotaciones que indican ocurrencias específicas, como un cambio de estado en una señal de acuerdo.

- Retardos:Espacios visuales entre un cambio de entrada y el cambio de salida correspondiente, que representan el retardo de propagación.

A diferencia de los diagramas síncronos, que dependen de líneas de cuadrícula que representan bordes de reloj, los diagramas asíncronos dependen de límites de eventos. Esto requiere una interpretación más cuidadosa de la separación entre transiciones.

Parámetros críticos de tiempo ⚙️

Para analizar la integridad de un sistema asíncrono, deben medirse parámetros específicos de tiempo y compararse con las especificaciones de diseño. Estos parámetros definen la ventana en la que una señal debe permanecer estable para ser correctamente interpretada por un receptor.

Retardo de propagación

El retardo de propagación es el tiempo que tarda una señal en viajar desde la entrada de un componente hasta su salida. En la lógica asíncrona, este retardo es una fuente principal de incertidumbre. Las variaciones en la fabricación, la temperatura y el voltaje pueden alterar este retardo.

- tpHL:Tiempo que tarda una señal en transicionar de Alto a Bajo.

- tpLH:Tiempo que tarda una señal en transicionar de Bajo a Alto.

- tpd:Retardo de propagación general, a menudo calculado como el promedio de tpHL y tpLH.

Al analizar un diagrama de tiempos, busca la distancia horizontal entre el borde de entrada y el borde de salida resultante. Esta distancia es el retardo de propagación.

Tiempo de preparación y tiempo de retención

Incluso en sistemas asíncronos, los flip-flops y los bloqueos a menudo requieren ventanas específicas de estabilidad. El tiempo de preparación es la duración antes de un evento desencadenante en que los datos deben estar estables. El tiempo de retención es la duración después del evento desencadenante en que los datos deben permanecer estables.

Si se violan estas ventanas, el sistema puede entrar en un estado de metastabilidad, en el que la salida no es ni alta ni baja, sino un nivel de voltaje indefinido. Los diagramas de tiempos ayudan a visualizar estas violaciones mostrando si los datos cambian demasiado cerca de un borde de control.

Desfase y jitter

- S desfase: La diferencia en el tiempo de llegada de la misma señal en dos puntos diferentes del circuito.

- Jitter: Variaciones a corto plazo en la sincronización de la señal. En sistemas asíncronos, el jitter puede ser causado por ruido de alimentación o acoplamiento cruzado.

Manejo de cruces de dominios de reloj 🔄

Una de las fuentes más comunes de errores en sistemas mixtos implica el cruce entre diferentes dominios de reloj. Aunque un sistema sea principalmente asíncrono, a menudo contiene sub-bloques síncronos que operan a frecuencias diferentes. Los diagramas de tiempos son esenciales para verificar estos cruces.

Cuando una señal pasa de un dominio de reloj a otro, el receptor puede muestrear la señal en un momento en que esta está cambiando. Esto conduce a la metastabilidad. El enfoque estándar para mitigar esto es usar un sincronizador, típicamente una cadena de flip-flops.

| Parámetro | Descripción | Impacto en el diagrama de tiempos |

|---|---|---|

| Tiempo de resolución de metastabilidad | Tiempo necesario para que el sincronizador se resuelva a un nivel lógico válido | Muestra un período extendido de estado indefinido antes de que la señal se estabilice |

| Latencia de cruce de dominios | Retardo adicional introducido por el sincronizador | Aumenta la brecha de tiempo entre el evento de origen y el evento de destino |

| Latencia de handshake | Tiempo necesario para las señales de reconocimiento en protocolos asíncronos | Crea un patrón de ida y vuelta en la línea de tiempo de la señal |

Los analistas deben asegurarse de que el diagrama de tiempos tenga en cuenta el tiempo de resolución. Si un bloque posterior intenta leer la señal antes de que el sincronizador se resuelva, se produce corrupción de datos.

Identificación y resolución de condiciones de carrera ⚠️

Una condición de carrera ocurre cuando el comportamiento del sistema depende del tiempo relativo de eventos que no deberían influirse mutuamente. En la lógica asíncrona, esto es una preocupación frecuente. Los diagramas de tiempos son el método principal para detectar estas condiciones.

Hazard estáticos

Una falla estática ocurre cuando una señal debería permanecer a un nivel constante pero se invierte momentáneamente debido a retrasos en las rutas. Por ejemplo, si una señal debería mantenerse lógicamente en alto, pero un cambio en la entrada causa una breve caída a bajo, esto es una falla estática-1.

- Indicador visual:Un pico estrecho o pulso en una línea de señal que debería ser plana.

- Causa raíz:Retardos de propagación desiguales a través de diferentes puertas lógicas.

Fallas dinámicas

Las fallas dinámicas implican múltiples transiciones cuando solo se espera una. Esto suele ocurrir en caminos lógicos complejos donde las señales recorren diferentes números de puertas.

Pasos de análisis para condiciones de carrera

- Rastrear las rutas:Identifique todas las rutas que una señal sigue desde la fuente hasta el destino.

- Medir los retardos:Calcule el retardo para cada ruta utilizando el diagrama de tiempos.

- Comparar bordes:Verifique si los tiempos de llegada de señales competidoras se solapan de forma que genere ambigüedad.

- Verificar estabilidad:Asegúrese de que las señales de control permanezcan estables durante la ventana crítica de llegada de datos.

Si se encuentra una condición de carrera, es posible que el diseño deba reestructurarse. Las soluciones comunes incluyen agregar buffers para igualar los retardos, insertar protocolos de mano, o utilizar estructuras FIFO asíncronas.

Consideraciones de integridad de señal y ruido 🔌

Los diagramas de tiempo no existen en el vacío. La capa física introduce ruido que afecta la calidad de la señal. Al analizar sistemas asíncronos, los ingenieros deben distinguir entre errores lógicos de tiempo y degradación física de la señal.

Glitches de señal

Los glitches son pulsos de corta duración que pueden propagarse a través de un circuito. En sistemas asíncronos, un glitch puede activar erróneamente un latch o flip-flop. Los diagramas de tiempo a menudo los muestran como picos delgados.

- Filtrado:Asegúrese de que la lógica posterior tenga suficiente retardo para filtrar estos pulsos.

- Tasa de borde:Los bordes más pronunciados (tiempos de subida/bajada más rápidos) son más susceptibles a la acoplamiento de ruido.

Crosstalk

El crosstalk ocurre cuando una señal en un cable induce una tensión en un cable adyacente. Esto puede desplazar el tiempo de una señal, haciendo que llegue antes o después de lo esperado.

En un diagrama de tiempos, el crosstalk podría manifestarse como un desplazamiento en la ubicación del borde o como un pico adicional de ruido. Para mitigar esto, se debe considerar la separación entre señales durante la fase de diseño físico.

Mejores prácticas para la documentación 📝

Una documentación clara garantiza que el análisis de tiempo pueda reproducirse y entenderse por otros ingenieros. Un diagrama de tiempos bien estructurado incluye metadatos y anotaciones específicas.

Estandarización

- Utilice símbolos consistentes para los niveles lógicos.

- Etiquete todas las señales claramente con su función.

- Indique la escala de tiempo de forma explícita (por ejemplo, nanosegundos por división).

Anotaciones

Las anotaciones de texto son cruciales para explicar comportamientos específicos. Utilice flechas para señalar transiciones críticas o áreas potenciales de problema. Etiquete los valores de retardo de propagación directamente en el diagrama.

Control de versiones

Los diagramas de tiempo evolucionan conforme cambia el diseño. Mantenga números de versión para todos los diagramas para asegurar que el análisis coincida con el estado actual del hardware. No confíe en la memoria para detalles de tiempo.

Proceso paso a paso de análisis 🛠️

Para analizar de forma efectiva un sistema asíncrono, siga un enfoque estructurado. Esto asegura que no se omita ningún parámetro de tiempo crítico.

- Defina el disparador:Identifique el evento que inicia la secuencia. Este suele ser el punto de partida para el eje del tiempo.

- Mapa el intercambio de señales:Siga las señales de solicitud y de reconocimiento. Asegúrese de que sigan el protocolo correcto (por ejemplo, intercambio de cuatro fases o dos fases).

- Mida los retardos:Calcule la latencia total desde el disparador hasta la salida final. Descomponga esto en retardos de componentes.

- Verifique las restricciones:Verifique que se cumplan los tiempos de establecimiento y retención para todos los elementos de almacenamiento involucrados.

- Simule variaciones:Analice el diagrama bajo condiciones extremas, como temperatura máxima o voltaje mínimo.

- Revise la metastabilidad:Asegúrese de que la probabilidad de metastabilidad se reduzca a un nivel aceptable mediante sincronizadores.

Errores comunes en el análisis de tiempo ⚡

Incluso los ingenieros con experiencia pueden pasar por alto problemas sutiles. Ser consciente de los errores comunes ayuda a evitar reingenierías costosas.

- Ignorar el retardo del cableado:Depender únicamente del retardo de la puerta mientras se ignora la resistencia y la capacitancia de los interconexiones.

- Asumir retardo cero:Tratar los bucles de realimentación como instantáneos, lo cual es físicamente imposible.

- Descuidar el reinicio asíncrono:Fallar al tener en cuenta el tiempo de las señales de reinicio respecto a las señales de datos.

- Confundir borde y nivel: Confundir los comportamientos activados por borde y activados por nivel en la interpretación del diagrama.

Conclusión sobre la verificación ✅

Los diagramas de tiempo son indispensables para la verificación de sistemas asíncronos. Proporcionan una representación visual concreta de las relaciones temporales abstractas. Al analizar rigurosamente estos diagramas, los ingenieros pueden identificar condiciones de carrera, verificar protocolos de intercambio de señales y garantizar la integridad de las señales.

La complejidad del diseño asíncrono exige precisión. Cada nanosegundo cuenta. Una comprensión exhaustiva de los retardos de propagación, los tiempos de establecimiento y los tiempos de retención permite crear sistemas robustos. Aunque la ausencia de un reloj global añade dificultad, las percepciones obtenidas del análisis detallado del tiempo conducen a diseños más eficientes y confiables.

Continuar perfeccionando estas habilidades de análisis garantiza que los sistemas funcionen correctamente bajo diversas condiciones ambientales. El objetivo es la estabilidad y la previsibilidad, logradas mediante una documentación y medición meticulosas.

Consideraciones avanzadas 🔬

Para aplicaciones de alto rendimiento, entran en juego factores adicionales. Estos incluyen gradientes de temperatura a través del chip y caídas de voltaje durante los eventos de conmutación.

- Gradientes de temperatura:Las señales que viajan desde el centro caliente de un chip hasta el borde más frío experimentarán velocidades diferentes. Esta variación debe reflejarse en el análisis de tiempo.

- Ruido en la red de alimentación:El ruido de conmutación simultánea puede desplazar los umbrales lógicos. Los diagramas de tiempo deberían incluir idealmente una representación de la estabilidad de las líneas de alimentación.

- Latencia variable:Algunos protocolos asíncronos permiten una latencia variable. El diagrama de tiempo debe mostrar el rango de latencias aceptables, no solo un valor único.

Incorporando estas consideraciones avanzadas, el análisis de tiempo se convierte en una herramienta completa para la validación del sistema. Va más allá de la verificación simple hacia una verdadera optimización del rendimiento.

Recuerda que el tiempo no se trata solo de velocidad; se trata de corrección. Un sistema rápido que falla debido a errores de tiempo es menos útil que un sistema más lento que funciona de forma confiable. El diagrama de tiempo es el mapa que te guía hacia esa confiabilidad.