Comprender el flujo de señales dentro de un sistema digital es fundamental para los ingenieros que trabajan en hardware, firmware o software embebido. Un diagrama de tiempos actúa como la herramienta visual principal para representar cómo interactúan diferentes señales durante un período específico. Esta representación visual permite a los equipos verificar que los datos se capturen correctamente, que los relojes sean estables y que las transiciones lógicas ocurran sin conflictos. Sin una comprensión precisa de estos diagramas, la fiabilidad del sistema puede verse gravemente afectada. Esta guía explora los elementos esenciales que componen un diagrama de tiempos, asegurando un diseño y análisis precisos.

¿Qué es un diagrama de tiempos? 📊

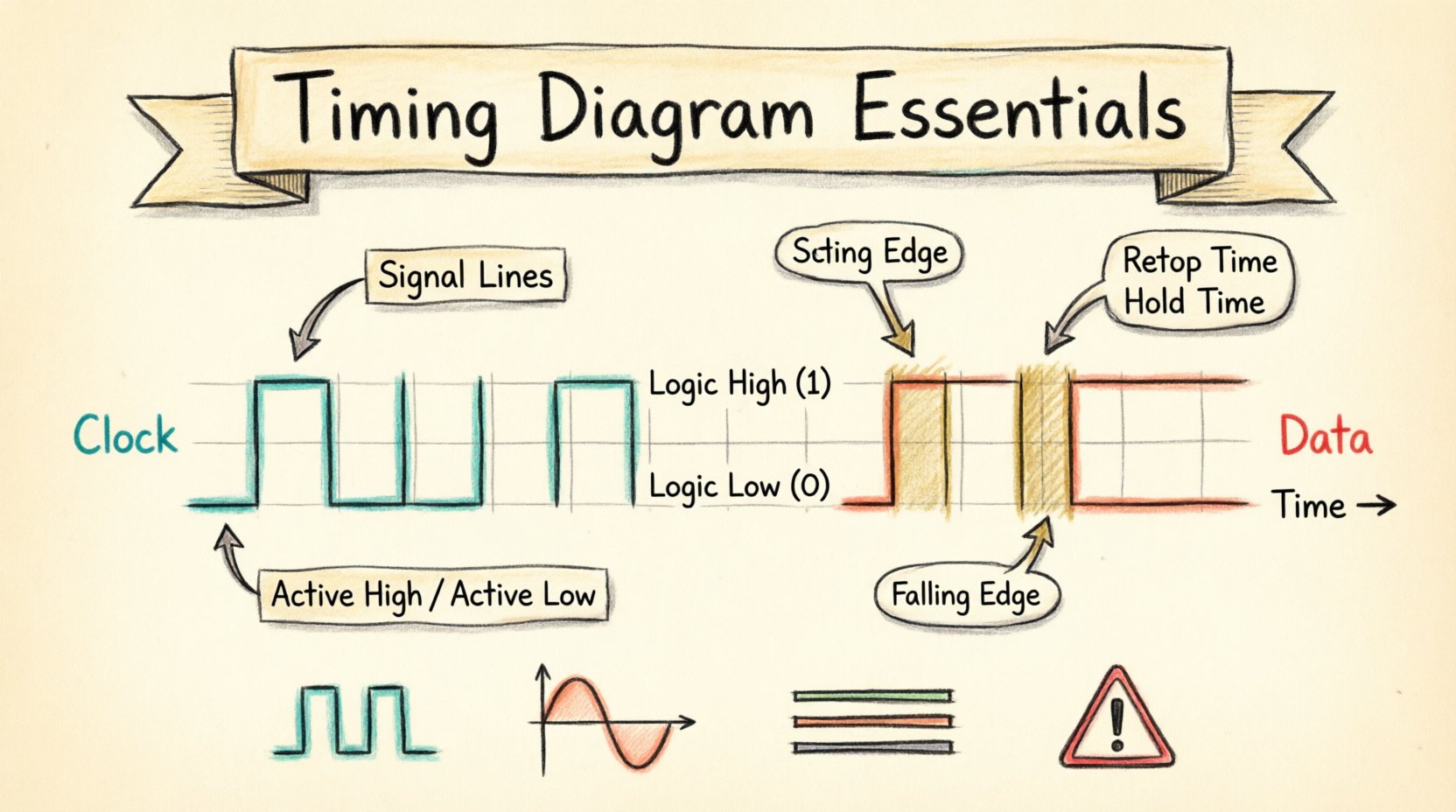

Un diagrama de tiempos es una ilustración gráfica que muestra el comportamiento de dos o más señales a lo largo del tiempo. Representa la secuencia de eventos, indicando cuándo las señales cambian de estado, cuánto tiempo permanecen en ese estado y cómo se relacionan con una fuente de reloj. En el diseño de hardware, estos diagramas son indispensables para verificar que los componentes se comuniquen correctamente. En software, ayudan a visualizar la concurrencia, las condiciones de carrera y los puntos de sincronización.

Estos diagramas suelen representar el tiempo en el eje horizontal (eje x) y el nivel o estado de la señal en el eje vertical (eje y). Las líneas verticales representan puntos específicos en el tiempo, mientras que las líneas horizontales indican el estado estable de una señal. Las transiciones entre estos estados son cruciales, ya que indican la transferencia real de datos o las acciones de control que ocurren dentro del sistema.

Componentes principales de un diagrama de tiempos 🔧

Para leer o crear un diagrama de tiempos efectivo, se debe comprender los bloques fundamentales. Cada diagrama, independientemente de su complejidad, depende de un conjunto consistente de elementos para transmitir la información con precisión.

- Eje del tiempo: La línea base horizontal que representa la progresión del tiempo. Suele fluir de izquierda a derecha, indicando el pasado al futuro.

- Líneas de señal: Trayectorias horizontales asignadas a cables específicos, buses o variables. Cada línea representa el nivel lógico de una señal específica.

- Niveles lógicos: Las posiciones verticales en la línea de señal. Normalmente se muestran los estados alto (1, Vcc, Verdadero) y bajo (0, Tierra, Falso).

- Transiciones: Las líneas verticales que conectan los niveles lógicos. Una transición ascendente va de bajo a alto, mientras que una transición descendente va de alto a bajo.

- Anotaciones: Etiquetas de texto o marcadores que aclaran eventos específicos, retrasos o estados.

El eje del tiempo: la precisión importa ⏳

El eje del tiempo es la base del diagrama. No siempre representa segundos del mundo real; a menudo representa ciclos de reloj o nanosegundos, dependiendo de la velocidad del diseño. La consistencia en la escala es vital. Si una sección del diagrama muestra 10 nanosegundos por cuadrado de cuadrícula, otra sección debe mantener esa escala, a menos que se haya ampliado explícitamente para mostrar detalles.

Al analizar el rendimiento del sistema, el eje del tiempo ayuda a identificar cuellos de botella. Por ejemplo, si una señal de datos requiere 50 nanosegundos para estabilizarse, pero el borde del reloj ocurre después de 40 nanosegundos, existe una violación. El eje permite a los ingenieros medir directamente estos intervalos.

Líneas de señal y niveles lógicos 🔄

Cada línea de señal corresponde a un cable físico o una variable lógica. En sistemas complejos, un bus podría representarse mediante una línea gruesa con múltiples señales agrupadas, o líneas individuales para cada bit. Los niveles lógicos definen el estado de la señal:

- Activo alto: La señal se considera “encendida” o “verdadera” cuando el voltaje es alto.

- Activo bajo: La señal se considera “encendida” o “verdadera” cuando el voltaje es bajo. Esto a menudo se indica con un círculo en el símbolo o con una convención de nombres específica.

Comprender el estado activo es crucial para interpretar señales de control como “Seleccionar chip” o “Habilitar escritura”. Interpretar erróneamente una señal activa baja como activa alta puede provocar fallos en el diseño que son difíciles de depurar.

Transiciones y bordes ⚡

Las transiciones ocurren cuando una señal cambia de un nivel lógico a otro. Estos cambios rara vez son instantáneos en el mundo físico, pero en un diagrama de tiempos, a menudo se dibujan como líneas verticales para representar el momento ideal de cambio.

- Borde ascendente: La transición de bajo a alto. Este es a menudo el punto de activación para la lógica síncrona.

- Borde de caída: La transición de alto a bajo. Algunos sistemas utilizan esta transición para capturar datos.

- Disparado por borde: Lógica que responde únicamente en el momento de la transición.

- Disparado por nivel: Lógica que responde mientras la señal permanezca en un estado específico.

Las señales del mundo real tienen tiempos de subida y bajada. Una línea vertical perfecta es una abstracción. En diseños de alta velocidad, la pendiente de la transición importa porque afecta la interferencia electromagnética y la integridad de la señal.

Parámetros y restricciones de tiempo 📐

Más allá de las líneas visuales, el valor crítico de un diagrama de tiempos radica en los parámetros cuantitativos definidos junto con las señales. Estos parámetros determinan los límites físicos dentro de los cuales debe operar el hardware.

Tiempo de preparación y tiempo de retención ⚙️

Estas son las dos restricciones más comunes en el diseño de lógica secuencial, particularmente cuando se captura datos mediante un flip-flop en un borde de reloj.

- Tiempo de preparación: La cantidad mínima de tiempo que la señal de datos debe permanecer estableantes el borde activo del reloj. Si los datos cambian demasiado cerca del borde del reloj, el flip-flop podría no capturar el valor correcto.

- Tiempo de retención: La cantidad mínima de tiempo que la señal de datos debe permanecer establedespués el borde activo del reloj. Si los datos cambian demasiado pronto después del borde, la captura podría verse corrupta.

| Parámetro | Definición | Consecuencia de la violación |

|---|---|---|

| Tiempo de preparación | Tiempo durante el cual los datos deben estar estables antes del borde del reloj | Metastabilidad o captura incorrecta de datos |

| Tiempo de retención | Tiempo durante el cual los datos deben estar estables después del borde del reloj | Metastabilidad o captura incorrecta de datos |

| Retardo de propagación | Tiempo que tarda la señal en viajar a través de una puerta | Reducción del margen de tiempo, frecuencia máxima más baja |

| Desviación del reloj | Diferencia en el tiempo de llegada de la señal de reloj | Reducción del margen de tiempo efectivo |

Retardo de propagación ⏱️

El retardo de propagación es el tiempo que tarda un cambio en la entrada en afectar a la salida. En un diagrama de tiempos, esto se observa como el espacio entre una transición del reloj y el cambio de datos resultante. Este retardo se debe a limitaciones físicas, como la capacitancia en los cables y la velocidad de conmutación de los transistores.

Al diseñar un sistema, la suma de los retardos de propagación a lo largo de una ruta debe ser menor que el período del reloj menos el tiempo de configuración. Si el retardo es demasiado largo, el sistema no puede funcionar a la velocidad de reloj deseada.

Desviación del reloj y jitter 📉

La desviación del reloj se refiere a la diferencia en los tiempos de llegada de la señal de reloj en diferentes partes del circuito. En un diagrama ideal, la línea de reloj es vertical y simultánea para todos los componentes. En la realidad, las diferencias en la ruta causan desviación. Una desviación positiva significa que el reloj llega más tarde en el destino, lo que puede ayudar con el tiempo de configuración pero perjudica el tiempo de retención.

El jitter es la variación en el momento de las transiciones de la señal. Es ruido que hace que la transición ocurra antes o después de lo esperado. Un alto jitter reduce el margen de tiempo efectivo, lo que obliga al sistema a funcionar más lentamente para mantener la estabilidad.

Tipos de señales y buses 📡

Los diferentes sistemas utilizan distintos métodos de señalización. El diagrama de tiempos debe reflejar estas diferencias para ser preciso.

Señales digitales

La mayoría de los diagramas de tiempos se centran en la lógica digital. Estas señales son binarias, conmutando entre 0 y 1. La claridad del diagrama depende de marcar claramente los umbrales lógicos. Algunas señales pueden tener estados intermedios o condiciones de “no importa”, generalmente marcadas con una X.

Señales analógicas

Aunque menos comunes en diagramas de tiempos puramente digitales, las señales analógicas como las líneas de voltaje o las salidas de sensores a veces se incluyen. Se representan con líneas inclinadas o curvas en lugar de pasos agudos, indicando una variación continua en lugar de cambios de estado discretos.

Buses y datos en paralelo

Cuando múltiples bits viajan simultáneamente, a menudo se agrupan. Un diagrama de tiempos de bus muestra el estado de todos los bits a la vez. Es esencial etiquetar el ancho del bus (por ejemplo, 8 bits, 32 bits) y mostrar la ventana de datos válidos donde todos los bits están estables al mismo tiempo.

Lectura de un diagrama de tiempos: una guía paso a paso 🔍

Interpretar estos diagramas requiere un enfoque sistemático para evitar omitir detalles críticos.

- Identifique el reloj: Localice la referencia principal de tiempo. Todos los demás eventos deben medirse en relación con esta línea.

- Determine la sensibilidad de la transición: Verifique si el sistema se activa en la transición ascendente o descendente del reloj.

- Rastree la validez de los datos: Busque el período en el que las líneas de datos son estables. Este es la “ventana válida”.

- Verifique las señales de control: Identifique las líneas de habilitación, reinicio o selección de chip que controlan la transferencia de datos.

- Mida los intervalos: Utilice el eje del tiempo para medir retardos, tiempos de preparación y anchos de pulso.

Violaciones y errores de temporización comunes ⚠️

Aunque se planifique con cuidado, ocurren violaciones de temporización. Reconocer las señales en un diagrama es el primer paso para corregirlas.

- Violación de preparación: Los datos llegan demasiado tarde para el siguiente borde de reloj. La solución a menudo implica ralentizar el reloj o optimizar la ruta lógica para reducir el retardo.

- Violación de mantenimiento: Los datos cambian demasiado pronto después del borde de reloj. Esto suele ser más difícil de corregir porque puede requerir añadir retardo en la ruta de datos o en la ruta de reloj.

- Metastabilidad: Un estado en el que la salida de un flip-flop no es ni 0 ni 1 durante un período indefinido. Esto suele ocurrir cuando se violan los tiempos de preparación o de mantenimiento.

- Glitches: Pulsos cortos e involuntarios causados por condiciones de carrera en la lógica combinacional. Estos pueden provocar cambios de estado falsos si no se filtran.

Diseño asíncrono frente a síncrono 🔄

Los diagramas de temporización tienen aspectos diferentes según el método de diseño.

Diseño síncrono

Los eventos se coordinan mediante un reloj global. El diagrama de temporización muestra líneas de reloj claras y periódicas. Los datos solo cambian en los bordes del reloj. Este enfoque simplifica el análisis porque la ventana de temporización es fija.

Diseño asíncrono

Los eventos se coordinan mediante señales de intercambio (como Petición y Reconocimiento). El diagrama de temporización muestra intervalos irregulares entre eventos. Aunque es más flexible, este tipo de diagramas es más difícil de analizar porque no existe una referencia temporal fija.

Aplicación en protocolos 📡

Los protocolos de comunicación dependen en gran medida de un temporizado preciso. Comprender el diagrama es clave para implementar estas normas.

Comunicación serial

Las interfaces seriales envían datos uno a uno. El diagrama de temporización muestra el período de bit. La relación entre el reloj y la línea de datos (por ejemplo, datos válidos en el borde ascendente) define las reglas del protocolo.

Comunicación paralela

Las interfaces paralelas envían múltiples bits a la vez. El diagrama de temporización debe mostrar el tiempo de preparación para toda la báscula. Todos los bits deben estar estables antes de que ocurra el borde de bloqueo.

Mejores prácticas para la documentación 📝

Crear una documentación clara garantiza que otros ingenieros puedan entender el sistema sin ambigüedades.

- Use etiquetas consistentes: Nombre las señales exactamente como aparecen en el código o el esquema.

- Incluya unidades: Especifique siempre las unidades de tiempo (ns, µs, ciclos) en el eje.

- Destaque las rutas críticas: Utilice líneas en negrita o colores para indicar las señales más sensibles al tiempo.

- Anote las violaciones: Si se conoce una violación, márquela claramente en lugar de ocultarla.

- Manténgalo actualizado: Actualice los diagramas cada vez que cambie el diseño. Los diagramas desactualizados son una fuente principal de errores.

Consideraciones avanzadas: Dominios de reloj múltiples 🌐

Los sistemas modernos a menudo operan con múltiples dominios de reloj que funcionan a diferentes velocidades. Un diagrama de tiempo para estos sistemas debe mostrar claramente la relación entre los relojes.

- Transiciones entre relojes: Los datos que pasan de un dominio rápido a uno lento requieren una sincronización cuidadosa para evitar pérdidas de datos.

- Relaciones de fase: Si dos relojes comparten una fuente pero tienen fases diferentes, el diagrama debe mostrar el desfase.

- Lógica de intercambio de señales: Los puentes asíncronos entre dominios dependen de señales de intercambio. El diagrama de tiempo debe mostrar el ciclo completo de solicitud-acknowledgment.

El papel de la simulación en el análisis de tiempo 💻

Antes de construir el hardware, las simulaciones verifican los diagramas de tiempo. Los ingenieros utilizan visualizadores de ondas para comparar el comportamiento esperado con los resultados simulados.

- Análisis estático de tiempo: Calcula los retrasos peor caso sin simular las ondas reales.

- Simulación dinámica de tiempo: Ejecuta una versión virtual del circuito para generar ondas reales.

- Simulación post-layout: Toma en cuenta las longitudes físicas de los cables y la capacitancia después de diseñar el chip.

Estas herramientas permiten a los ingenieros validar el diagrama de tiempo frente a la realidad física. Si la simulación muestra una violación de configuración, el diseño debe revisarse antes de la fabricación.

Conclusión sobre la precisión del tiempo ✅

Dominar la creación e interpretación de diagramas de tiempo es una habilidad fundamental para los profesionales técnicos. Estos diagramas cierran la brecha entre la lógica abstracta y la realidad física. Garantizan que las señales lleguen cuando se necesitan, en el estado correcto y con suficiente estabilidad para que el sistema funcione. Al adherirse a los elementos y restricciones descritos en esta guía, los equipos pueden reducir errores y mejorar la confiabilidad del sistema. La atención al detalle en estas representaciones visuales tiene beneficios en la estabilidad y el rendimiento del producto final.

Ya sea que trabaje en interfaces de memoria de alta velocidad, microcontroladores de bajo consumo o buses de datos complejos, los principios permanecen los mismos. El tiempo es la constante, y las señales son las variables. Comprender su relación es la clave para una ingeniería exitosa.