La comunicación ingenieril depende en gran medida de la precisión visual. Al discutir interacciones del sistema, propagación de señales o flujo de datos, un diagrama de tiempo bien construido sirve como el lenguaje universal. Estos diagramas capturan la relación entre eventos a lo largo del tiempo, permitiendo a los ingenieros diagnosticar problemas, verificar lógica y documentar el comportamiento del sistema de forma efectiva. Sin embargo, un diagrama confuso, ambiguo o mal escalado puede provocar malentendidos costosos. Esta guía establece los estándares esenciales para crear diagramas que transmitan la verdad técnica sin confusión.

📊 Comprendiendo los fundamentos de los diagramas de tiempo

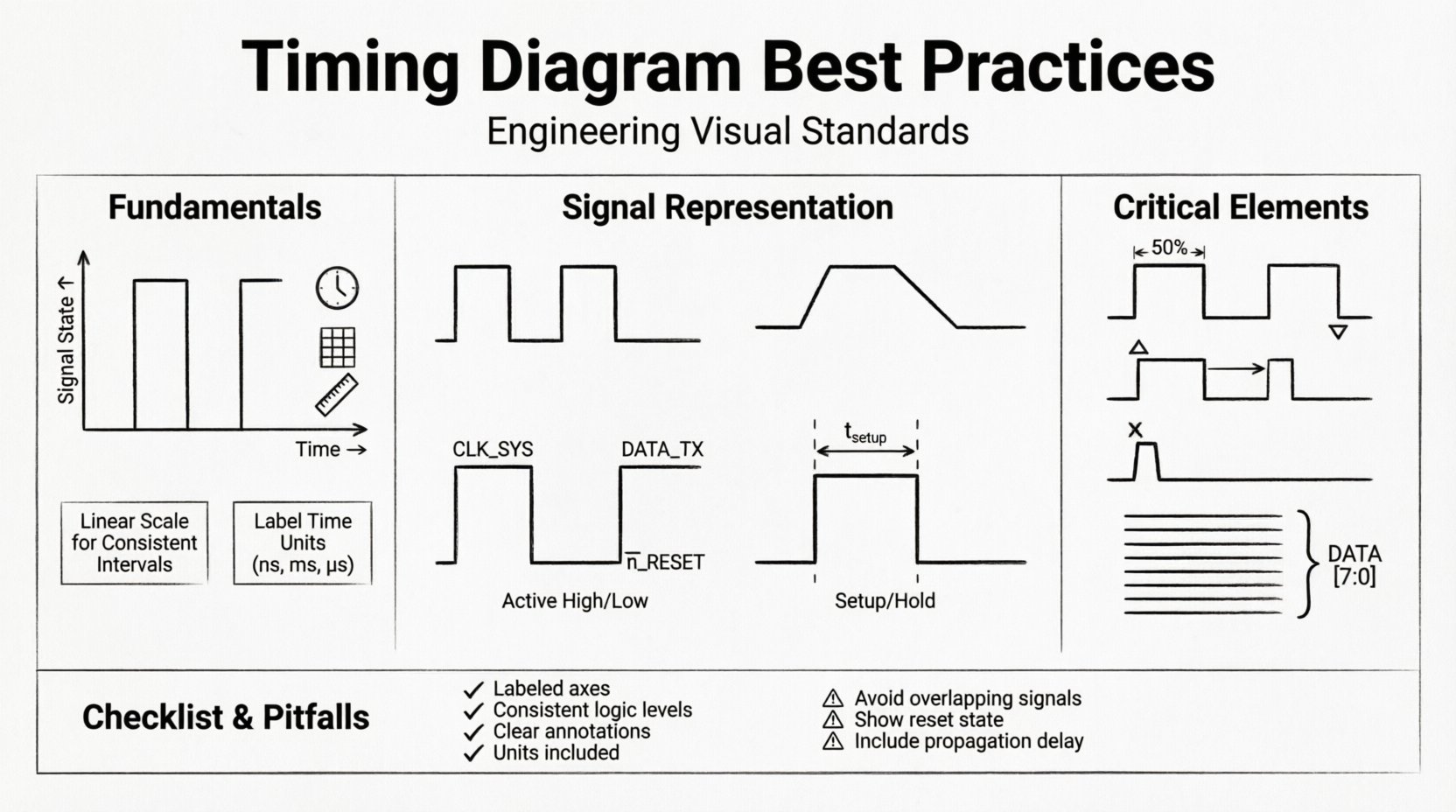

Un diagrama de tiempo es una representación gráfica de cómo cambian de estado las señales con el tiempo. No es simplemente un dibujo; es una especificación. Ya sea que esté trabajando en interfaces de hardware, sistemas embebidos o protocolos de software, el principio subyacente permanece el mismo: el tiempo fluye horizontalmente y los estados de la señal se representan verticalmente. En este contexto, la claridad no es un lujo; es un requisito para la seguridad y la confiabilidad.

Al crear estas visualizaciones, el objetivo es reducir la carga cognitiva para el lector. No deberían tener que adivinar dónde comienza el reloj, qué línea representa los datos o cuáles son los umbrales de voltaje. Cada elemento debe cumplir una función.

- Eje del tiempo: La dimensión horizontal representa la progresión del tiempo. Puede ser lineal o logarítmica, dependiendo de los eventos que se capturen.

- Líneas de señal: La dimensión vertical representa el estado de una señal, como Alto/Bajo, 1/0 o niveles de voltaje.

- Eventos: Puntos específicos en el tiempo en los que ocurren cambios, como bordes, pulsos o transferencias de datos.

📏 Configurando tu lienzo y escala

La base de un diagrama claro es la cuadrícula. Sin una escala consistente, la relación entre eventos se distorsiona. Un boceto que parece correcto a un nivel de zoom puede revelar violaciones críticas de tiempo a otro nivel.

1. Definir la escala de tiempo

Las escalas de tiempo deben elegirse según el evento más rápido del sistema. Si está documentando una interacción a nivel de microsegundos, dibujar la línea de tiempo en milisegundos ocultará los detalles. Por el contrario, si los eventos abarcan segundos, una escala de microsegundos genera ruido innecesario. Etiquete siempre claramente la unidad de tiempo en el eje.

- Escalado lineal:Úselo para intervalos consistentes. Es el estándar para la documentación de la mayoría de protocolos.

- Escalado logarítmico: Raramente utilizado, pero necesario cuando los eventos abarcan órdenes de magnitud (por ejemplo, retrasos de arranque frente a tiempos de procesamiento).

2. Líneas de cuadrícula y puntos de referencia

Las líneas de cuadrícula ayudan al ojo a rastrear los intervalos de tiempo a través del diagrama. Las líneas gruesas deben marcar las unidades principales (por ejemplo, 10 ms), mientras que las líneas más delgadas marcan las unidades menores (por ejemplo, 1 ms). Esta jerarquía visual evita que el lector se pierda.

Asegúrese de que las líneas verticales de cuadrícula coincidan con eventos importantes. Si una transición del reloj cae exactamente en una línea de cuadrícula, proporciona un ancla natural para leer los tiempos de preparación y retención. No fuerce los eventos a ajustarse a la cuadrícula si representan mediciones del mundo real; en su lugar, ajuste la cuadrícula o use anotaciones para mostrar el desfase.

⚡ Representando las señales con precisión

La forma en que se dibuja una señal determina cómo se interpreta. Una transición ascendente implica una transición de bajo a alto, pero la velocidad y la forma de esa transición pueden tener significado respecto a la integridad de la señal.

1. Estados y niveles de señal

Defina claramente qué constituye un estado lógico. En la lógica digital, esto suele ser 0 (Bajo) y 1 (Alto). En contextos analógicos o de señales mixtas, se requieren niveles de voltaje (por ejemplo, 0V a 5V). Use estilos de línea distintos para diferenciar entre:

- Alto activo: La señal es verdadera cuando la línea está en el nivel superior.

- Bajo activo: La señal es verdadera cuando la línea está en el nivel inferior (a menudo indicado con una barra sobre el nombre de la señal).

2. Representación de aristas

Las aristas son la parte más crítica del diagrama. Indican el momento exacto en que ocurre un cambio de estado. Utilice líneas agudas y sólidas para transiciones ideales. Si necesita representar tasas de cambio físicas o tiempos de subida, dibújelas como líneas inclinadas en lugar de picos verticales.

Evite líneas dentadas a menos que esté documentando específicamente ruido o fallos. Las líneas limpias sugieren estabilidad; las líneas dentadas sugieren interferencia. Sea intencional con la forma que dibuje.

3. Convenciones de nomenclatura de señales

Un nombre de señal no es solo una etiqueta; es una definición. Evite nombres genéricos comoSignal_A o Wire_1. En su lugar, utilice nombres funcionales que describan la finalidad, comoCLOCK_SYS o DATA_TX.

- Prefijos: Utilice prefijos estándar para indicar el tipo de señal (por ejemplo,

Npara lógica negativa,CLKpara reloj). - Mayúsculas y minúsculas: Utilice mayúsculas para constantes y señales, y mayúsculas y minúsculas para variables si es aplicable.

- Consistencia: Asegúrese de que el nombre en el diagrama coincida exactamente con el nombre en el código o en la hoja de datos.

⏱️ Clocking y sincronización

Los relojes controlan el tiempo de los sistemas síncronos. Representar incorrectamente un reloj puede invalidar todo el diagrama. La señal de reloj suele ser el primer punto de referencia que revisa un lector.

1. Ciclo de trabajo y período

Dibuje la señal de reloj con un ciclo de trabajo consistente, a menos que el sistema requiera específicamente un tiempo variable. Si el ciclo de trabajo no es del 50%, anote las duraciones alta y baja. El período (el tiempo para un ciclo completo) debe marcarse claramente.

Para sistemas de frecuencia variable, no asuma que una longitud de línea constante representa un tiempo constante. Etiquete cada período individualmente si difieren significativamente.

2. Disparo por borde

Indique si el sistema se activa por el borde ascendente (positivo) o el borde descendente (negativo). Puede usar flechas o triángulos pequeños en el punto del borde. Esto es crucial para entender cuándo se muestrea los datos.

- Borde de subida:Marca con un pequeño triángulo apuntando hacia arriba.

- Borde de bajada:Marca con un pequeño triángulo apuntando hacia abajo.

3. Jitter y fase

En sistemas de alta velocidad, el jitter (variación en el tiempo) es un factor conocido. Si estás dibujando un ideal teórico, líneas rectas están bien. Si estás documentando un comportamiento medido, utiliza una región sombreada o múltiples trazos para mostrar la variabilidad. Las relaciones de fase entre múltiples relojes deben indicarse explícitamente.

🔄 Manejo de transiciones de datos

Las señales de datos suelen ser más complejas que los relojes. Cambian según el estado del sistema. Documentar correctamente estas transiciones requiere atención a la relación entre los datos y el reloj.

1. Tiempos de preparación y retención

Estas son restricciones críticas para la captura confiable de datos. El tiempo de preparación es la duración antes del borde del reloj en la que los datos deben estar estables. El tiempo de retención es la duración después del borde del reloj en la que los datos deben permanecer estables. Visualízalos como ventanas relativas al borde del reloj.

Dibuja líneas verticales punteadas para indicar las ventanas de preparación y retención. Etiqueta la duración en unidades de tiempo (por ejemplo, t_setup = 5ns). Esto visualiza el margen disponible para que el sistema funcione correctamente.

2. Metastabilidad

Cuando las señales cruzan dominios de reloj, puede ocurrir metastabilidad. Este es un estado en el que la señal no está completamente alta ni baja. Representa esto con una línea punteada o una sombreadura específica en la ventana de tiempo. Documentar esto advierte al lector de que la señal podría tardar más de lo habitual en resolverse.

3. Averías y ruido

Pulsos espurios, conocidos como averías, pueden causar errores lógicos. Si una avería es un problema conocido, dibújala como un pulso estrecho que no cumple con el requisito mínimo de ancho de pulso de la lógica receptora. No ocultes estos artefactos; a menudo son la causa raíz de fallas intermitentes.

🏷️ Anotaciones y etiquetado

El texto en un diagrama tiene peso. Sobrecargar el diagrama con texto lo hace ilegible. Etiquetar insuficientemente lo hace ambiguo. Encuentra el equilibrio mediante una colocación estratégica.

1. Colocación del texto

Coloca el texto cerca de la parte relevante de la señal, pero evita que se solape con las líneas de señal. Usa líneas de referencia (líneas delgadas que conectan el texto con la señal) si la señal es demasiado densa para contener el texto directamente arriba o abajo.

2. Unidades y símbolos

Incluye siempre unidades. El tiempo debe estar en segundos, milisegundos o nanosegundos. El voltaje debe estar en voltios. No dependas de que el lector adivine. Usa símbolos estándar para operaciones lógicas (por ejemplo, ! para NO, & para AND) si estás mostrando ecuaciones lógicas junto con el tiempo.

3. Legibilidad

El tamaño de fuente importa. En un documento impreso o en una pantalla, el texto debe ser legible sin necesidad de acercar. Si el diagrama es complejo, considera dividirlo en varias vistas: una visión general de alto nivel y una vista detallada y ampliada de eventos específicos.

🚫 Errores comunes que deben evitarse

Incluso los ingenieros con experiencia cometen errores al elaborar estas visualizaciones. Ser consciente de los errores comunes puede ahorrar horas de depuración.

- Ignorar el retardo de propagación:Las señales tardan tiempo en viajar a través de los cables y puertas lógicas. Si una señal cambia en el punto A y llega al punto B, dibuje el retardo. Una línea vertical en el punto B implica un viaje instantáneo, lo cual es físicamente imposible.

- Niveles lógicos inconsistentes: Asegúrese de que la definición de Alto y Bajo no cambie a mitad del diagrama. Esto es confuso y peligroso.

- Señales superpuestas: Si dos señales deben cruzarse, asegúrese de que sean claramente distinguibles. Use diferentes grosores de línea o colores si el medio de salida lo permite.

- Estados de reinicio omitidos: Los sistemas a menudo comienzan en un estado específico. Muestre el estado inicial antes de que comience a funcionar el reloj. Esto evita la confusión sobre lo que hacen las señales en el tiempo cero.

🧠 Consideraciones avanzadas

A medida que los sistemas se vuelven más complejos, los diagramas de tiempo deben evolucionar para manejar escenarios multi canal y asíncronos.

1. Temporización multi canal

Al trabajar con buses (como buses de datos), agrupe las señales relacionadas. Use un corchete para indicar que las líneas superiores representan el ancho del bus (por ejemplo, DATA[7:0]). Muestre la transición de todo el grupo para indicar una transferencia paralela.

2. Handshake asíncrono

No todos los sistemas usan un reloj global. Los protocolos de handshake dependen de señales de solicitud y reconocimiento. Dibújelas claramente con flechas que indiquen la dirección del handshake. Muestre los estados de espera en los que el sistema se detiene hasta recibir la señal.

3. Estados de gestión de energía

Los sistemas modernos entran en modos de bajo consumo. Indique estas transiciones en el diagrama de tiempo. Una señal podría bajar para indicar el modo de suspensión, pero el reloj podría detenerse o ralentizarse. Documente el estado de energía junto con el estado de tiempo.

✅ Lista de verificación de revisión

Antes de finalizar un diagrama, revise esta lista para asegurarse de cumplir con las mejores prácticas.

| Elemento de verificación | Criterios |

|---|---|

| Eje de tiempo | ¿La escala es lineal y etiquetada con unidades? |

| Nombres de las señales | ¿Todas las señales están nombradas de forma funcional y consistente? |

| Bordes del reloj | ¿Los bordes ascendentes/descendentes están claramente marcados? |

| Transiciones | ¿Son visibles y etiquetados los tiempos de setup/hold? |

| Retardos | ¿Se incluyen los retardos de propagación cuando son relevantes? |

| Anotaciones | ¿El texto es legible y libre de superposiciones? |

| Unidades | ¿Todas las mediciones van acompañadas de unidades (ns, V, etc.)? |

| Estado inicial | ¿Se muestra el estado de reinicio o estado de espera al inicio? |

| Claridad | ¿Un ingeniero colega puede interpretarlo sin hacer preguntas? |

📝 Pensamientos finales sobre la documentación

La calidad de un diagrama de temporización refleja la calidad de la ingeniería detrás de él. Un diagrama claro facilita la colaboración entre los equipos de hardware y software, reduce el tiempo de depuración y asegura que los futuros mantenimientos entiendan el comportamiento del sistema. Es una herramienta de verdad, no solo una ilustración.

Enfóquese en la precisión antes que en la estética. Aunque un diagrama atractivo es agradable, un diagrama correcto es esencial. Tómese el tiempo para verificar las mediciones, etiquetar cada restricción y alinear su lenguaje visual con las especificaciones técnicas. Al adherirse a estas prácticas, asegura que la información de temporización se preserve con precisión durante todo el ciclo de vida del producto.

Recuerde, el diagrama es un contrato. Define cómo se comporta el sistema. Cuando dibuja una línea, está haciendo una promesa sobre el comportamiento de la señal. Mantenga esa promesa clara, precisa e inequívoca.

Adoptar estas normas eleva el nivel profesional de su documentación. Envía un mensaje a su equipo y a los interesados de que valora la fiabilidad y la claridad. En el mundo complejo del diseño de sistemas, un buen diagrama a menudo marca la diferencia entre un lanzamiento exitoso y un problema recurrente.

🔧 Conclusión

Crear diagramas de temporización efectivos requiere un enfoque disciplinado en el diseño, la etiquetación y la representación. Al priorizar la claridad, la consistencia y la precisión técnica, los ingenieros pueden producir visualizaciones que sirvan como referencias confiables para el desarrollo y el mantenimiento. Siga las directrices sobre representación de señales, sincronización de reloj y anotaciones para asegurar que su documentación resista la prueba del tiempo y la complejidad.